1、UDP的使用場景

User-defined primitives (UDPs) 翻譯過來就是用戶自定義原語,常常用于構(gòu)建組合邏輯模型和時序邏輯模型。

我們編寫Verilo代碼時,定義寄存器使用的是reg 和always@(*clk*),運行VCS RTL仿真時,VCS能夠識別此類信號是寄存器,能夠模擬其行為模型。

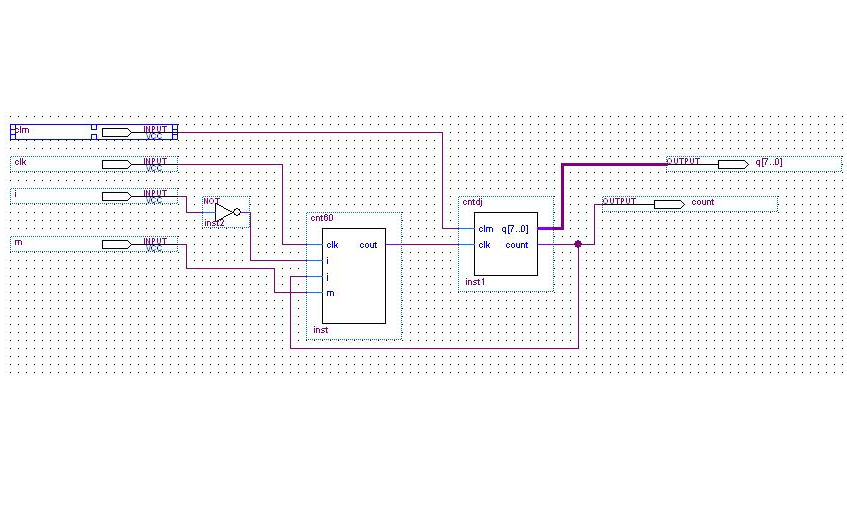

然而在使用VCS進(jìn)行網(wǎng)表仿真時,此時網(wǎng)表中寄存器名稱是這樣的SDFF*_XXXX,其中SDFF_XXXX是每個寄存器類型對應(yīng)的標(biāo)準(zhǔn)Cell的名稱。

SDFF_XXXX是每個Fab廠家獨有的名稱,且在Verilog規(guī)范中并沒有相關(guān)術(shù)語,那么VCS等EDA仿真工具是如何識別并且模擬其器件行為的呢?

實際上進(jìn)行網(wǎng)表仿真時,EDA工具會讀取對應(yīng)SDFF_XXXX的UDPs模型,從而進(jìn)行SDFF_XXXX的行為模擬。

2、UDPs的語法說明

2.1. 2種類型

UDPs的分為combinational UDP(組合邏輯)和 sequential UDP(時序邏輯)。

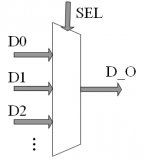

combinational UDP用于構(gòu)建組合邏輯模型,常見有mux模塊.

sequential UDP用于構(gòu)建寄存器和Latch模型,sequential UDP可以是邊沿觸發(fā),也可以是電平觸發(fā)。

2.2.基本語法規(guī)范

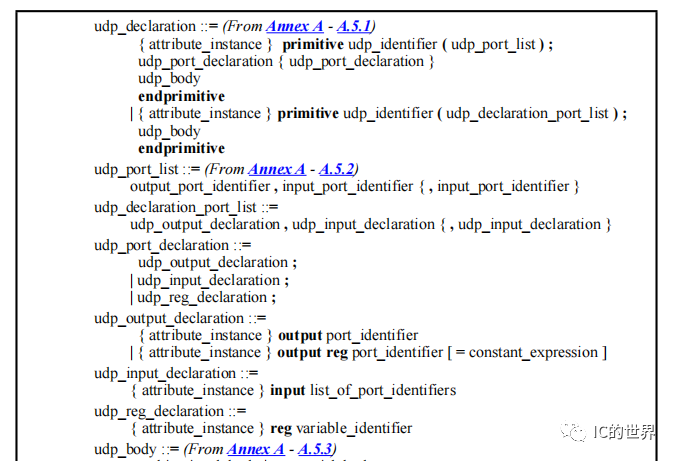

UDP建模使用primitive表示建模開始,類似module,endprimitive表示建模結(jié)束,類似endmodule。

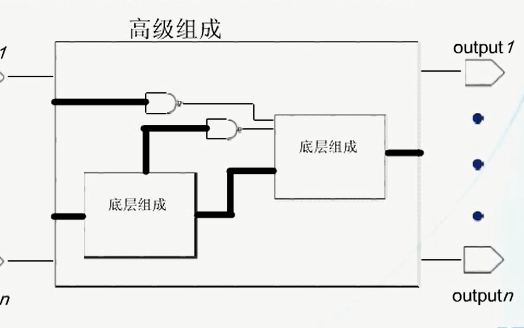

UDP模型在描述層級上與module/endmodule屬于同一等級,因此primitive/endprimitive不能出現(xiàn)在module/endmodule內(nèi)部,就像不能在一個模塊里出現(xiàn)module~module~endmodule~endmodule.

//語法錯誤 modulexxx(); primitive endprimitive endmodule

每個UDP有且只有一個輸出,并且輸出只有三種狀態(tài),0, 1, or x,不支持Z狀態(tài)。

每個UDP可以由多個輸入信號,如果輸入信號為z,則當(dāng)做X對待。時序UDP至少允許9個輸入信號,組合UDP至少允許10個輸入信號。

每個UDP不支持定義inout類型的信號

時序UDP的輸出信號應(yīng)該使用reg申明。

組合UDP的輸出信號不能使用reg申明。

時序UDP可以使用initial語句定制仿真開始前output信號的初始值

2.3.UDP state table(狀態(tài)表)

UDP模型使用狀態(tài)表來描述模型的行為,

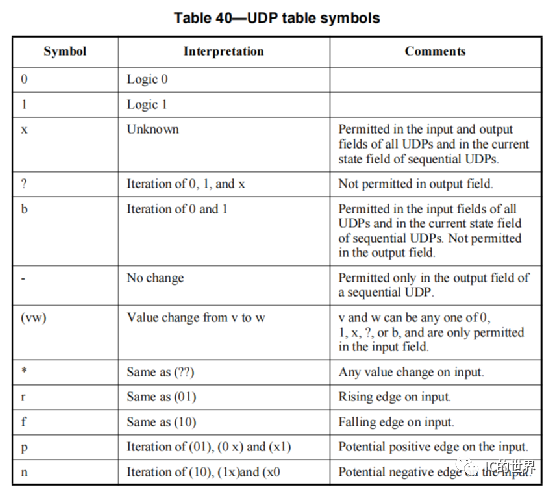

狀態(tài)表中使用的各類變量見表40。例如r表示上升沿,f表示下降沿。*表示數(shù)值改變。

狀態(tài)表中的每行以分號結(jié)束。

狀態(tài)表本質(zhì)上就是一個輸入信號/輸出信號組合的列表。

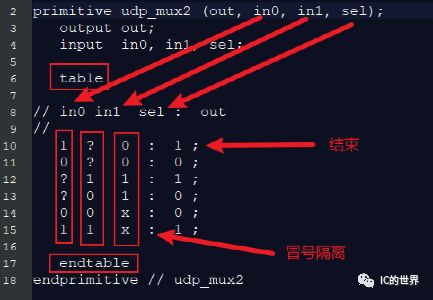

組合UDP狀態(tài)表中有一個冒號“:”,用于隔離輸入和輸出信號。

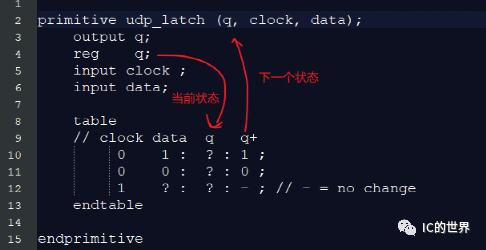

時序UDP狀態(tài)表中有當(dāng)前狀態(tài),還有下一個狀態(tài),因此有2個冒號“:”,用于隔離輸入、輸出(當(dāng)前狀態(tài))和下一個狀態(tài)。

組合UDP模型中,如果輸入信號狀態(tài)組合在狀態(tài)表中沒有指定,則輸出會是X。

2.4.UDP結(jié)構(gòu)

本節(jié)可忽略,直接看案例

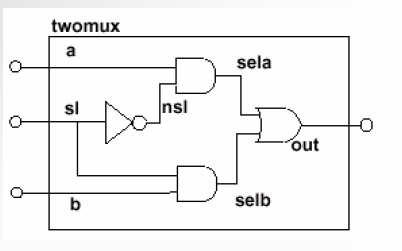

3、組合UDP案例

如下案例為2選1的mux,sel為1時,out為in1;sel為0時,out為in0。

請注意:信號列表中,輸出信號out在第一個。狀態(tài)表中,out處于最后一列。

4、電平觸發(fā)時序UDPs

如下案例為一個低電平觸發(fā)的latch。

使用reg申明了一個內(nèi)部變量,表示當(dāng)前狀態(tài)q,即當(dāng)前udp的輸出狀態(tài)。

table中的q+代表的是下一個有效周期的輸出狀態(tài)。

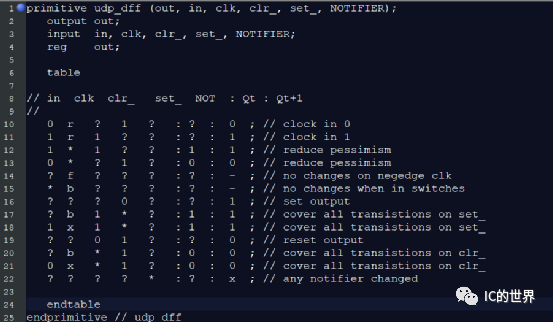

5、邊沿觸發(fā)時序UDP

如下所示為一個上升沿觸發(fā)寄存器的模型。

其中NOTIFIER信號用于建立時間和保持時間檢查,通過建立時間和保持時間檢查,則NOTIFIER不變,時序檢測不通過則NOTIFIER翻轉(zhuǎn),udp_dff輸出為x態(tài)。

6、小技巧

將primitive類比成module,將endprimitive類比成endmodule,將table 類比成case,將endtable類比成endcase,你就知道該怎么寫UDP模型了。

7、總結(jié)

雖然使用UDP能夠構(gòu)建網(wǎng)表時序邏輯和組合的邏輯的行為模型,但是仿真終究是仿真,無法做到與實際芯片行為完全一致,特別是在部分信號為X態(tài)時。因此網(wǎng)表仿真中如果X態(tài)的出現(xiàn)導(dǎo)致仿真出現(xiàn)問題,此時不代表電路真的存在問題,需要仔細(xì)分析原因,其中需要重點分析UDP模型是怎么寫的。

-

寄存器

+關(guān)注

關(guān)注

31文章

5322瀏覽量

120021 -

仿真

+關(guān)注

關(guān)注

50文章

4044瀏覽量

133424 -

Verilog

+關(guān)注

關(guān)注

28文章

1345瀏覽量

109988 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59706

原文標(biāo)題:Verilog語法: 必須掌握的User-defined primitives (UDPs)

文章出處:【微信號:IP與SoC設(shè)計,微信公眾號:IP與SoC設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Verilog_HDL的基本語法詳解(夏宇聞版)

FPGA視頻教程之Verilog語法基礎(chǔ)的詳細(xì)資料說明

Verilog HDL的基礎(chǔ)知識詳細(xì)說明

有關(guān)Verilog中的一些語法詳細(xì)資料說明

Verilog UDPs的語法說明

Verilog UDPs的語法說明

評論