Vivado是Xilinx公司2012年推出的新一代集成開發環境,它強調系統級的設計思想及以IP為核心的設計理念,突出IP核在數字系統設計中的作用。

01

什么是IP核

隨著電子設計自動化工具功能的不斷增強,以及半導體制造工藝的飛速發展,所設計的數字系統功能越來越復雜,所要求的設計周期越來越短,設計可靠性越來越高。對設計人員來說,不可能從頭開始進行復雜數字系統的設計。目前普遍采用的方法是,在設計中盡可能使用已有的功能模塊。人們把這些現成的模塊通常稱為知識產權(Intellectual Property,IP)核,也就是IP核。IP核可以理解為一個個具有特定功能的電路模塊,通過這些模塊間端口的互聯完成功能復雜的數字系統設計。

02

IP核來源

①IP核可以來自FPGA生產廠商,例如,Vivado設計工具中的IP目錄中就提供了豐富的IP核,可以直接使用。

②IP核還可以是第三方IP廠商提供。

③我們也可以將自己設計的,經過驗證的電路模塊封裝成IP核,可以在后期設計中重復使用。

我們自己的設計包括:

RTL代碼描述的電路。

HLS高層次綜合工具的設計。

Syetem Generator工具生成的工程。

03

IP核如何使用

那么我們如何在Vivado中使用IP核呢?

有兩種方式:

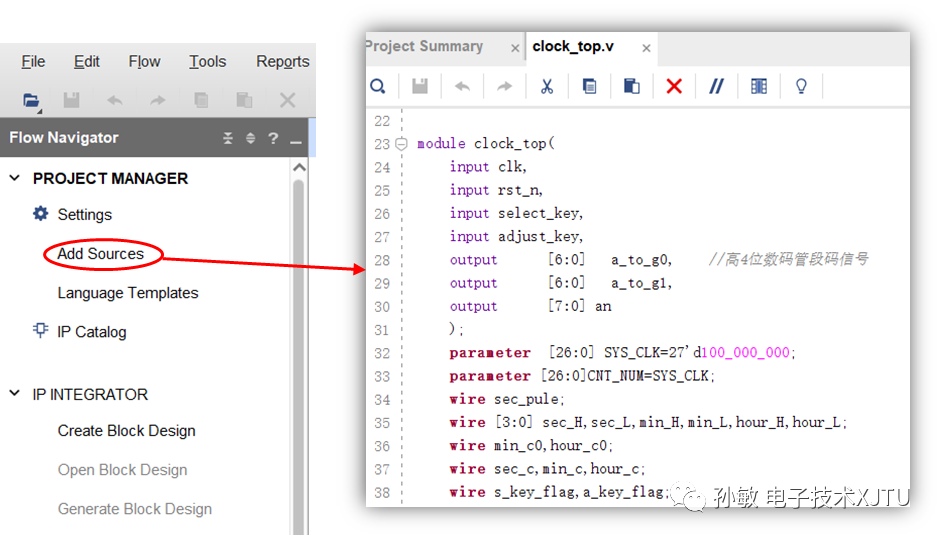

①一種是在RTL工程中,在我們的Verilog設計程序中調用IP核,我們叫做實例化IP。

△ 實例化IP

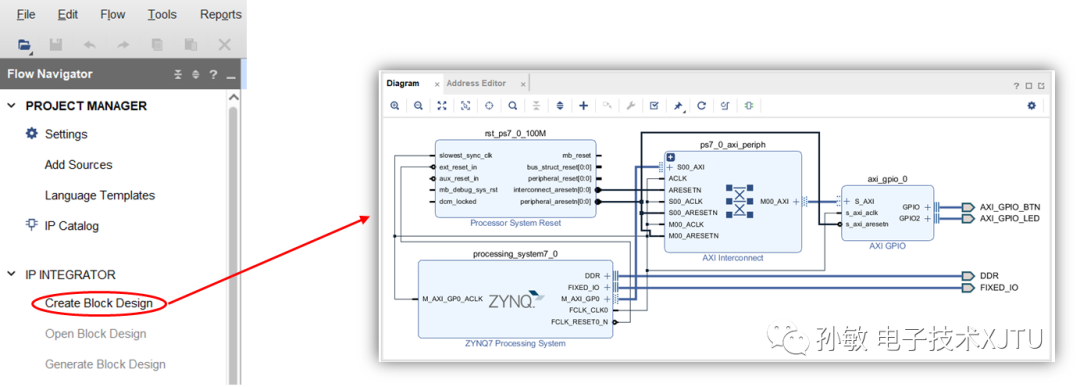

②一種是在IP Integrator中,也就是使用IP集成器創建一個Block Design,可以將IP核,以圖形化的方式添加到界面中,再通過端口的互聯,像搭積木一樣完成一些復雜的設計。

04

Vivado設計輸入

在Vivado中,我們有多種方式來進行我們的設計輸入。

RTL工程

通常使用的方法是創建RTL工程,使用硬件描述語言編寫代碼。所謂的RTL是Register Transfer Level 的縮寫,也就是寄存器傳輸級。

△ 創建RTL工程

我們在描述一個數字系統時,可以采用不同的抽象層級,抽象程度從高到低有系統級、算法級,RTL級,邏輯門級,以及開關級。

RTL級設計是描述數據信號是如何在寄存器中傳輸和處理的,一般都是通過硬件描述語言實現的。如,最常使用的Verilog 和VHDL,以及近年來,發展起來的System Verilog。

System Verilog實際上是Verilog的超集,可以被看做是Verilog的升級加強版,尤其加強了對設計驗證的支持,在現代數字系統設計與驗證廣泛使用。

IP集成器

另一種方式就是通過IP集成器,可以將IP核添加到圖形化界面中,再通過連線完成設計,這里的IP來自于IP目錄中的IP核。

△ 通過IP集成器創建工程

高層次綜合(HLS)工具

Xilinx還推出了Vivado High-Level Synthesis (HLS)高層次綜合工具,用戶可以使用C或C++ 來對FPGA編程,實現算法開發,然后通過高級綜合工具直接將C語言轉換為硬件描述語言,可以大大加速我們的設計,提高開發效率。HLS會將轉換后的RTL代碼封裝成IP,我們可以將其添加到IP 目錄中,在Vivado設計輸入時使用。

System Generator

Vivado還提供了System Generator 工具,該工具是基于MATLAB下的Simulink工具運行的。他將Xilinx開發的一些模塊嵌入到了Simulink中,主要用于數字信號處理開發。在Simulink中設計完成后,可以生成HDL文件,包括測試文件,能夠加快DSP系統的開發進度。

05

基于IP的設計

Vivado HLS的輸出結果也可以導入到System Generator中,以模塊化的方式使用。

Vivado中的IP packaging功能可以將我們的RTL代碼,High Level Symthesis設計,System Generator模塊以及IP集成器生成的設計封裝成新的IP,放到IP目錄中使用。

所以說,Vivado是基于IP的設計。

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26489 -

寄存器

+關注

關注

31文章

5325瀏覽量

120048 -

C語言

+關注

關注

180文章

7601瀏覽量

136251 -

RTL

+關注

關注

1文章

385瀏覽量

59710 -

Vivado

+關注

關注

19文章

808瀏覽量

66347

發布評論請先 登錄

相關推薦

Vivado IP交付

怎么在Vivado HLS中生成IP核?

Vivado生成IP核

vivado調用IP核詳細介紹

如何在Vivado Design Suite 中進行IP加密

如何使用Vivado Logic Analyzer與邏輯調試IP進行交互

如何使用Vivado IP Integrator組裝具有多個時鐘域的設計

使用VIvado封裝自定IP并使用IP創建工程

Vivado中BRAM IP的配置方式和使用技巧

Vivado IP核Shared Logic選項配置

為什么說Vivado是基于IP的設計?

為什么說Vivado是基于IP的設計?

評論