0****1

時序邏輯電路設計方法

時序邏輯電路的特點是輸出信號不僅與電路的輸入有關,還與電路原來的狀態有關。

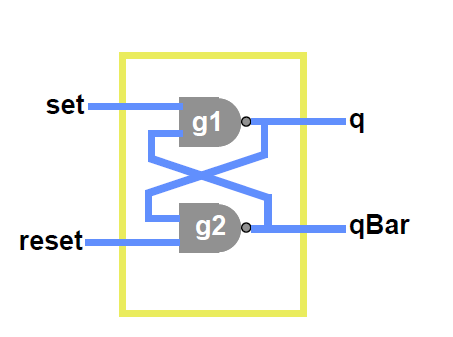

因此,電路需要具有記憶功能的存儲電路。FPGA中基本的存儲單元是D觸發器,也是實現時序邏輯的基本單元。

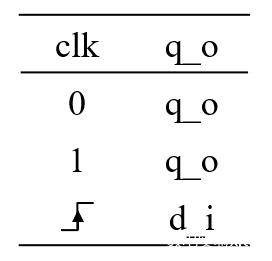

那么,什么樣的語句會被綜合成觸發器呢?在Verilog中,常使用always進程塊描述時序邏輯。此時,always進程塊中的敏感列表一般為時鐘邊沿和異步控制信號,

** always ** @(posedge clk,posedge rst)

always進程塊的執行是在時鐘邊沿觸發下進行的。

時序邏輯電路按狀態變化的特點,可以分為同步時序邏輯電路和異步時序邏輯電路。

同步時序邏輯電路的各個觸發器狀態的轉換在同一時鐘脈沖作用下完成。目前,大多數數字電路都是同步時序電路。我們實驗中所涉及到的也都是同步時序電路。

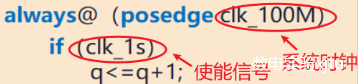

在設計時需要注意,所有always敏感列表中第一項敏感信號應該為同一時鐘信號,比如,都為系統時鐘clk的上升沿。

不出現其他派生信號,比如,系統時鐘產生的分頻信號等等。

異步時序邏輯電路中,沒有統一時鐘,各觸發器狀態轉換是異步完成的。

在always進程塊描述時序邏輯時,賦值語句使用非阻塞賦值,即“<=”。

0****2

時序邏輯電路設計實例

下面來看幾個D觸發器的設計實例,來理解Verilog語句與電路之間的關系。

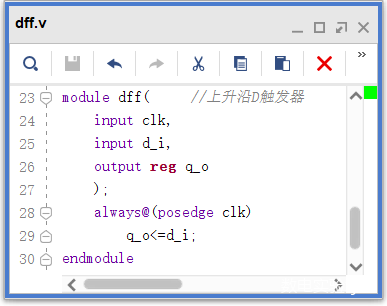

實例1:基本D觸發器

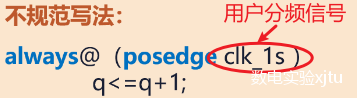

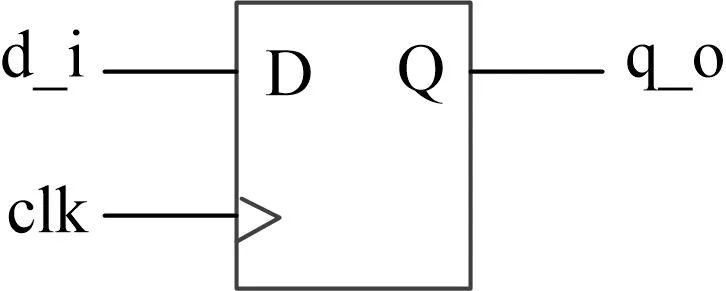

設計一個簡單的D觸發器,在時鐘上升沿觸發下,輸出等于輸入,其他時間輸出保持不變。

使用always語句進行描述,敏感列表為時鐘上升沿。當時鐘信號由0變為1時,執行always語句“q_o=d_i”,如下圖所示。

我們看到輸入信號d_i不出現在敏感信號列表中,也就表明,輸入的變化不會引發輸出立即變化,只有在時鐘上升沿時才被采樣。

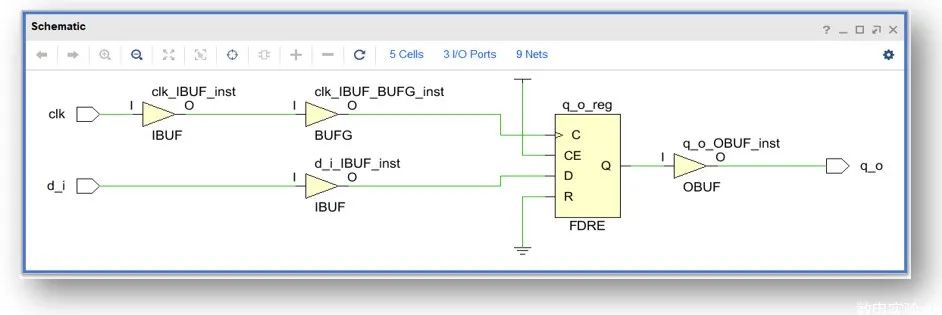

下面是綜合后的原理圖,綜合就是將Verilog設計對應到FPGA內部組成單元上。

我們看到,綜合出的是D觸發器(FDRE為D觸發器,參見賽靈思官方文檔ug799),其中敏感列表中的clk被綜合為觸發器的時鐘信號C,d_i連接D觸發器輸入端D。D觸發器還包含信號CE(時鐘使能端),以及R(復位端,高有效),在本示例中均未用到。因此,將CE連接高電平,使時鐘始終有效,R連接低電平,使復位無效。

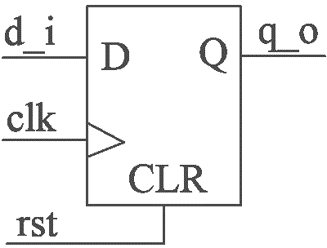

實例2:帶復位(高有效)的D觸發器

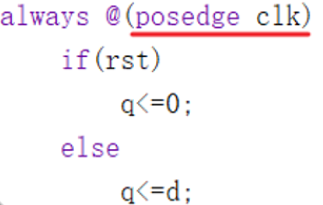

下面的例子加入了復位信號。復位分為同步復位和異步復位。

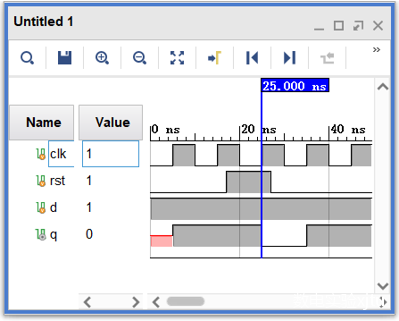

同步復位中,當復位信號有效時,必須要等到時鐘上升沿到來時,才能執行復位信號相關的行為語句,如仿真波形圖中所示。

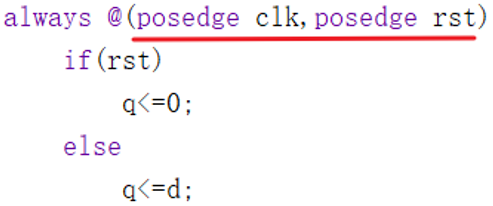

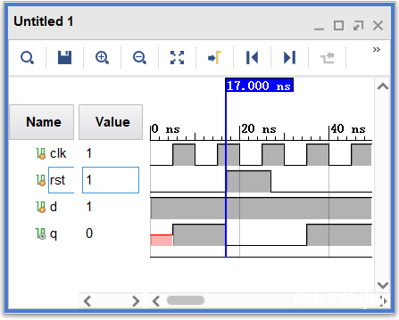

異步復位中的復位信號與時鐘沒有關系,只要復位信號有效,就立即執行復位相關的邏輯行為。要實現異步復位,復位信號要放在敏感列表中。

仿真波形圖中可以看到,當rst有效時,輸出立即被復位,下一個clk上升沿到來時,此時,rst信號仍然有效,因此,輸出為0。再一個clk到來時,復位無效,則輸出等于輸入。

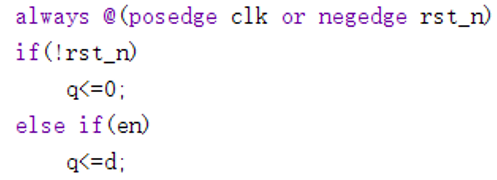

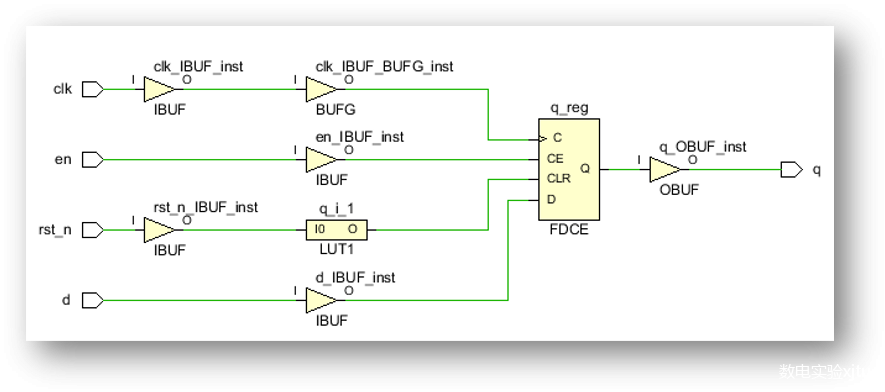

實例3:含異步復位(低有效)和同步使能的D觸發器

下面是一個帶有同步使能信號的D觸發器。

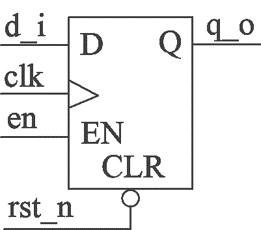

這里我們使用了低電平復位,當復位信號無效,使能信號有效時,在時鐘上升沿觸發下,輸出等于輸入。

在綜合后的原理圖中,en使能信號連接在了D觸發器的CE端。復位信號rst_n與CLK的連接經過一個LUT(LUT是FPGA用于實現組合邏輯的基本單元查找表),在Vivado中可以看到該LUT的真值表,它實現的是反相器的功能,這也說明了賽靈思的FPGA中觸發器的復位引腳是高有效的,如果你設計中復位是低有效,這里就會多出一個反相器將其邏輯取反。

03

always進程塊用法總結

always進程塊是最常用的行為描述語句,他可以描述組合邏輯也可以描述時序邏輯。

描述組合邏輯時,敏感列表中為輸入電平信號,而描述時序邏輯時,敏感列表為時鐘邊沿及異步控制信號。Vivado綜合工具會根據always后面的敏感列表的不同形式綜合出相應的電路。

always在仿真中還可以通過延時控制來產生激勵信號。例如,always #5 clk=~clk,表示當執行到該語句時,需要延遲5個時間單位的時間(由`timescales 定義),然后再執行“clk=~clk”。

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26483 -

反相器

+關注

關注

6文章

310瀏覽量

43243 -

D觸發器

+關注

關注

3文章

164瀏覽量

47861 -

時序邏輯電路

+關注

關注

2文章

94瀏覽量

16527 -

CLK

+關注

關注

0文章

127瀏覽量

17125

發布評論請先 登錄

相關推薦

如何使用Verilog硬件描述語言描述時序邏輯電路?

如何使用Verilog硬件描述語言描述時序邏輯電路?

評論