相關閱讀:

RA2快速設計指南 [2] MCU工作模式和選項設置存儲器

RA2快速設計指南 [3] 時鐘電路

6. 復位要求和復位電路

Arm?Cortex?-M23產(chǎn)品共有12或13種類型的復位。

表11. Arm?Cortex?-M23 MCU復位

注:RA2E1及RA2E2產(chǎn)品不支持。

6.1 引腳復位

當RES#引腳被拉低時,所有處理都將中止,MCU進入復位狀態(tài)。要在運行中復位MCU,應在指定的復位脈沖寬度內(nèi)將RES#保持為低電平。有關時序要求的更詳細信息,請參見《硬件手冊》中“電氣特性”一章的“復位時序”部分。另請參見本系列文章的第2節(jié)“仿真器支持”,了解與調(diào)試支持相關的復位電路的詳細信息。

無需在RES#線路上使用外部電容,因為POR電路在內(nèi)部將其保持為低電平以實現(xiàn)良好的復位,并且需要最小的復位脈沖來啟動此過程。

6.2 上電復位

有兩種情況會產(chǎn)生上電復位(POR):

1. 如果RES#引腳在接通電源后處于高電平狀態(tài)。

2. 如果RES#引腳在VCC低于VPOR時處于高電平狀態(tài)。

在VCC超過上電復位電壓(VPOR)并經(jīng)過上電復位時間(tPOR)之后,芯片將從上電復位狀態(tài)釋放。上電復位時間是允許外部電源和MCU達到穩(wěn)定狀態(tài)的時間。有關電壓大小和時序的詳細信息,請參見《硬件手冊》中“電氣特性”一章的“POR和LVD特性”部分。

由于POR電路依賴于RES#與VCC同時為高電平,因此請勿在復位引腳上放置電容。這將減慢RES#相對于VCC的上升時間,從而妨礙POR電路正確識別上電條件。

當電源(VCC)降至不超過VPOR時,如果RES#引腳為高電平,則會產(chǎn)生上電復位。在VCC上升到VPOR以上并且經(jīng)過tPOR之后,芯片將從上電狀態(tài)釋放。

上電復位后,RSTSR0中的PORF位置1。引腳復位后,PORF清零。

這是由獨立看門狗定時器(IWDT)產(chǎn)生的內(nèi)部復位。

當IWDT下溢時,可以選擇產(chǎn)生獨立看門狗定時器復位(可以改為產(chǎn)生NMI),并且RSTSR1中的IWDTRF位置1。短暫延遲后,將取消IWDT復位。詳情請參照《硬件手冊》。

6.4 看門狗定時器復位

這是看門狗定時器(WDT)產(chǎn)生的內(nèi)部復位。

當WDT下溢時,可以選擇產(chǎn)生看門狗定時器復位(可以改為產(chǎn)生NMI),并且RSTSR1中的WDTRF位置1。短暫延遲后,將取消WDT復位。詳情請參照《硬件手冊》。

6.5 電壓監(jiān)視復位

RA2系列包括允許MCU在欠壓期間防止不安全操作的電路。板上比較器根據(jù)三個參考電壓Vdet0、Vdet1和Vdet2檢查電源電壓。當電源下降到每個參考電壓以下時,會產(chǎn)生中斷或復位。檢測電壓Vdet0、Vdet1和Vdet2均可從3個不同大小的值中選擇。

當Vcc隨后上升到超過Vdet0、Vdet1或Vdet2時,經(jīng)過穩(wěn)定時間后,電壓監(jiān)視復位釋放將繼續(xù)。

上電復位后,將禁用低電壓檢測。可以通過使用選項功能寄存器OFS1來使能電壓監(jiān)視。有關更多詳細信息,請參見《硬件手冊》中的“低電壓檢測(LVD)”一章。

LVD復位后,RSTSR0中的LVDnRF(n = 0、1、2)位置1。

6.6 軟件復位

這是通過SYSRESETREQ位寫入Arm內(nèi)核的AIRCR寄存器產(chǎn)生的內(nèi)部復位。當SYSRESETREQ位設為1時,產(chǎn)生軟件復位,再經(jīng)過內(nèi)部復位時間(tRESW2)后,將取消內(nèi)部復位,CPU進行復位異常處理。詳情請參照MCU硬件手冊。

有關SYSRESETREQ位的詳細信息,請參照Arm?Cortex?-M23的技術(shù)手冊。

6.7 其他復位

MCU內(nèi)的大多數(shù)外設功能都可以在特定的故障條件下產(chǎn)生復位。無需硬件配置即可使能這些復位。有關將為每個外設功能產(chǎn)生復位的條件的詳細信息,請參見《硬件手冊》中的相關章節(jié)。

6.8 冷/熱啟動的確定

借助RA2 MCU,用戶可以確定發(fā)生復位過程的原因。RSTSR2中的CWSF標志指示是上電復位導致了復位過程(冷啟動),還是操作期間輸入的復位信號導致了復位過程(熱啟動)。

發(fā)生上電復位時,該標志置0。否則,該標志不會置0。通過軟件向該標志寫入1時會將其置1。即使在寫入0時也不會將其置0。

6.9 確定復位源

借助RA2 MCU,用戶可以確定復位信號產(chǎn)生源。讀取RSTSR0和RSTSR1,以確定哪個復位是復位源。有關流程圖,請參見《硬件手冊》中的“復位產(chǎn)生源的確定”部分。

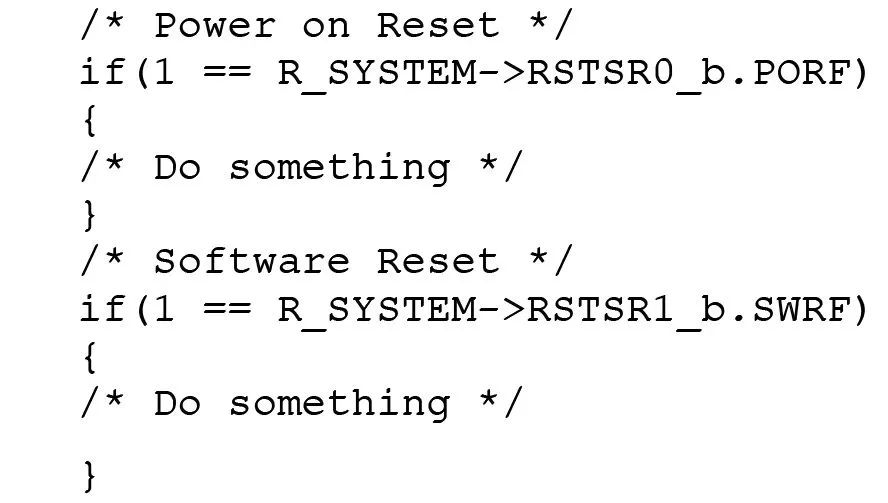

以下代碼示例展示了如何使用Renesas FSP中基于CMSIS的寄存器結(jié)構(gòu)確定復位是由軟件復位、深度軟件待機還是上電復位導致的。

來源:瑞薩MCU小百科

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進行處理

審核編輯 黃宇

-

mcu

+關注

關注

146文章

16991瀏覽量

350308 -

仿真器

+關注

關注

14文章

1016瀏覽量

83635 -

復位電路

+關注

關注

13文章

322瀏覽量

44536 -

Vcc

+關注

關注

2文章

305瀏覽量

35852

發(fā)布評論請先 登錄

相關推薦

RA2快速設計指南 [4] 復位要求和復位電路

RA2快速設計指南 [4] 復位要求和復位電路

![<b class='flag-5'>RA</b>6<b class='flag-5'>快速</b>設計<b class='flag-5'>指南</b> [6] <b class='flag-5'>復位</b><b class='flag-5'>要求和</b><b class='flag-5'>復位</b><b class='flag-5'>電路</b> (上)](https://file1.elecfans.com/web2/M00/89/ED/wKgaomSNDpGAehkrAAABlx7xSrs968.png)

![<b class='flag-5'>RA2</b><b class='flag-5'>快速</b>設計<b class='flag-5'>指南</b> [9] 一般布線實踐與參考資料(完結(jié))](https://file1.elecfans.com/web2/M00/A3/1F/wKgZomUDyFSAT6fEAABMTVrCfpI979.png)

![<b class='flag-5'>RA2</b><b class='flag-5'>快速</b>設計<b class='flag-5'>指南</b> [7] 模塊停止功能,中斷控制單元與低功耗](https://file1.elecfans.com/web2/M00/A4/8C/wKgaomUDyOyAOoMAAAI-ZvuSIMY086.jpg)

![<b class='flag-5'>RA2</b><b class='flag-5'>快速</b>設計<b class='flag-5'>指南</b> [6] 寄存器寫保護和I/O端口配置](https://file1.elecfans.com/web2/M00/A4/8C/wKgaomUDyRmANKEWAABPNEaw3Rg626.jpg)

![<b class='flag-5'>RA2</b><b class='flag-5'>快速</b>設計<b class='flag-5'>指南</b> [5] 存儲器](https://file1.elecfans.com/web2/M00/A3/21/wKgZomUDyXWAV5qfAAEgG1i2Pgo328.jpg)

![<b class='flag-5'>RA2</b><b class='flag-5'>快速</b>設計<b class='flag-5'>指南</b> [3] 時鐘<b class='flag-5'>電路</b>](https://file1.elecfans.com/web2/M00/A4/8D/wKgaomUDydmANV-eAAHf1-Z0aUw286.jpg)

評論