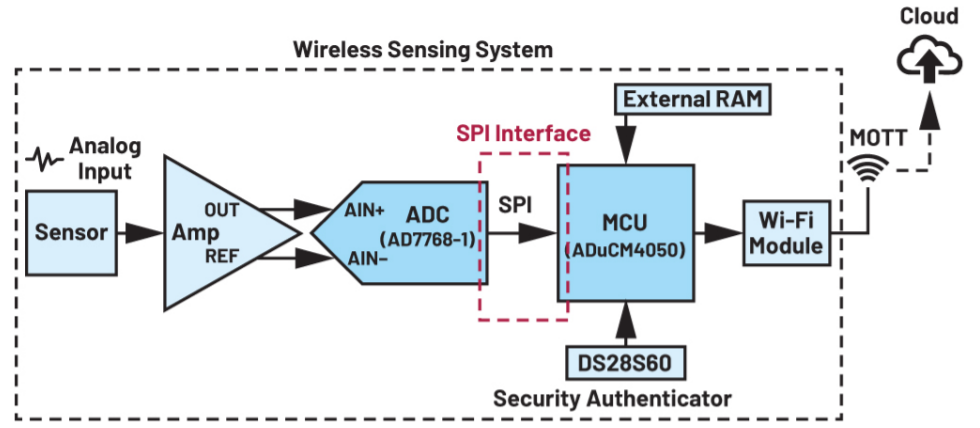

隨著技術的進步,低功耗物聯網(IoT)和邊緣/云計算需要更精確的數據傳輸。圖1展示的無線監測系統是一個帶有24位模數轉換器(ADC)的高精度數據采集系統。在此我們通常會遇到這樣一個問題,即微控制單元(MCU)能否為數據轉換器提供高速的串行接口。

本文描述了設計MCU和ADC之間的高速串行外設接口(SPI)關于數據事務處理驅動程序的流程,并簡要介紹了優化SPI驅動程序的不同方法及其ADC與MCU配置。本文還詳細介紹了SPI和直接存儲器訪問(DMA)關于數據事務處理的示例代碼。最后,本文演示了在不同MCU(ADuCM4050、MAX32660)中使用相同驅動程序時ADC的吞吐率。

圖1. 狀態監控。

通用SPI驅動程序簡介

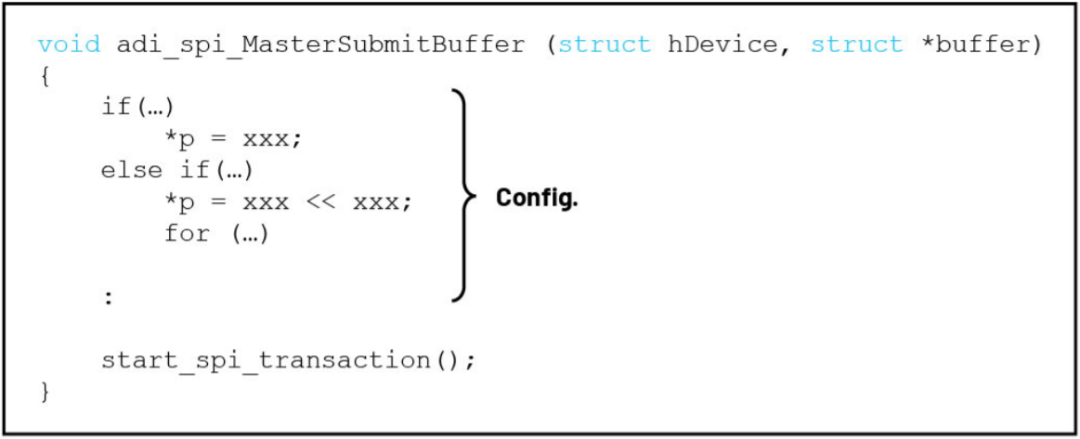

通常,MCU廠商會在例程代碼中提供通用的SPI驅動程序/API。通用SPI驅動程序/API通常可以涵蓋大多數用戶的應用,這些代碼可能包含許多配置或判斷語句。但在某些特定情況下,比如ADC數據采集,通用的SPI驅動程序可能無法滿足ADC數據的全速的吞吐速率需求,因為通用的驅動程序中有過多的配置,而未使用的配置會產生額外的開銷并導致時間延遲。

圖2. 通用API的配置。

設計思路與實踐框架

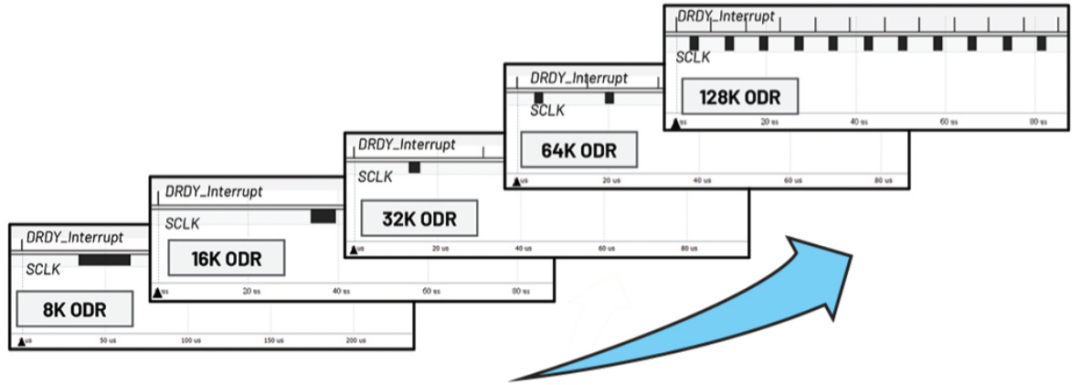

我們通常會選擇低功耗高性能的MCU作為主機通過SPI提取ADC的輸出數據。但是,由于ADI的SPI驅動程序的數據事務處理命令存在冗余,因此數據輸出速率可能被顯著降低。為了充分釋放ADC的潛在速率,本文使用ADuCM4050和AD7768-1進行實驗并嘗試可能的解決方案。盡管在使用默認濾波器的情況下,ADuCM4050的最大數據輸出速率可達256 kHz,但在當前情況下,其速率被限制在8 kHz。提高輸出速率的潛在解決方案包括刪除不必要的命令以及激活DMA控制器。本文將在以下小節中介紹這些思路。

圖3. 不同ODR以及DRDY與SCLK之間的關系。

以MCU作為主機

ADuCM4050 MCU是一款主時鐘速率為26 MHz的超低功耗微控制器,內核為ARM? Cortex?-M4F處理器。ADuCM4050配有三個SPI,每個SPI都有兩個DMA通道(接收和發射通道)可與DMA控制器連接。DMA控制器和DMA通道可實現存儲器與外設之間的數據傳輸。這是一種高效的數據分配方法,可將內核釋放以處理其他任務。

以ADC作為從機

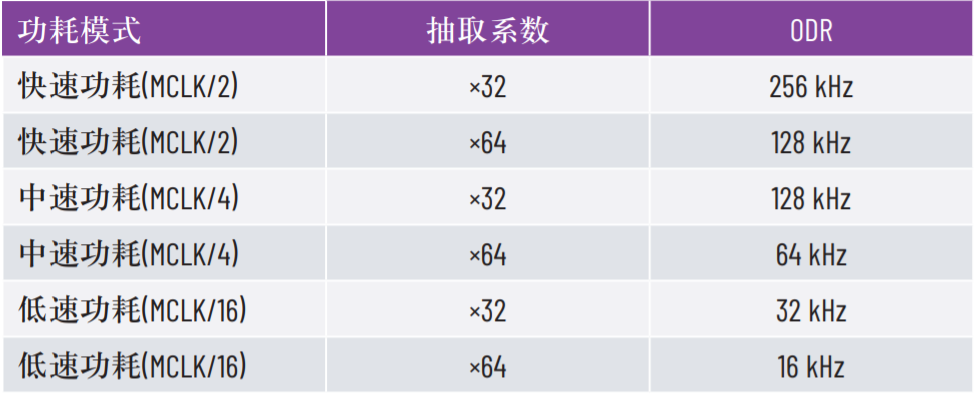

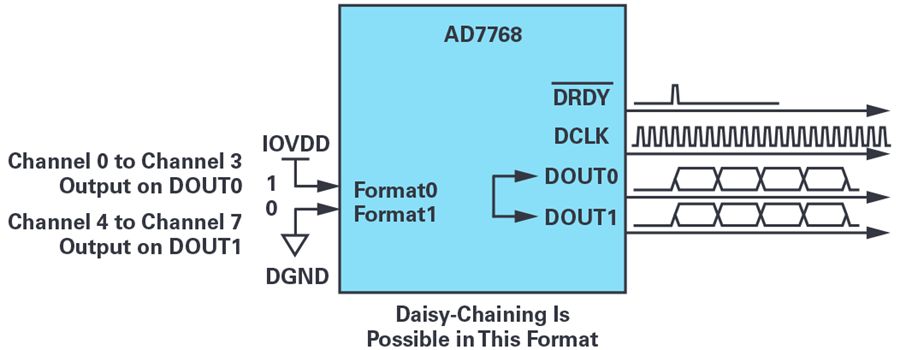

AD7768-1是一款24位低功耗、高性能的Σ-Δ ADC。其數據輸出速率 (ODR)和功耗模式均可根據用戶的要求進行配置。ODR由抽取系數和功耗模式共同決定,如表1中所示。

表1. 數據輸出速率的功耗模式配置

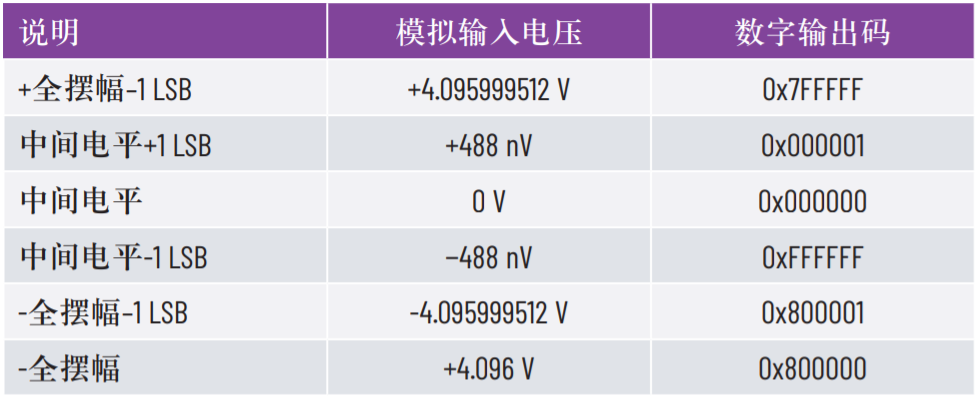

AD7768-1的連續讀取模式也是該產品的一個重要特性。ADC的輸出數據存儲在寄存器0x6C中。一般而言,每次讀/寫操作之前,ADC寄存器中的數據都需要地址才可以訪問,但是連續讀取模式則支持在收到每個數據就緒信號后直接從0x6C寄存器提取數據。ADC的輸出數據為24位的數字信號,對應的電壓如表2 所示。

表2. 數字輸出碼和模擬輸入電壓

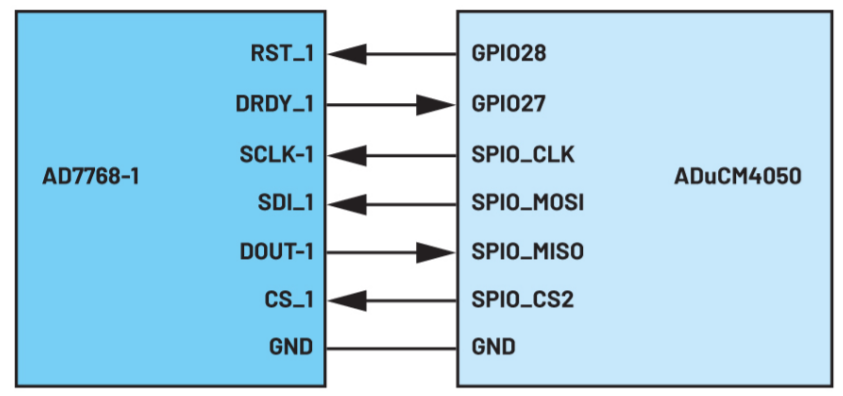

引腳連接示意圖

ADuCM4050和AD7768-1組成的數據事務處理示例模型的引腳連接如圖4所示。

圖4. AD7768-1和ADuCM4050的接口引腳連接。

ADC的復位信號引腳RST_1連接至MCU的GPIO28,而數據就緒信號引腳DRDY_1則連接至MCU的GPIO27。其余引腳則根據通用的SPI配置標準進行連接,其中MCU為主機,而ADC為從機。SDI_1接收MCU發送的ADC寄存器讀/寫命令,而DOUT_1則將ADC的輸出數據發送至MCU。

數據事務處理的實現

中斷數據事務處理

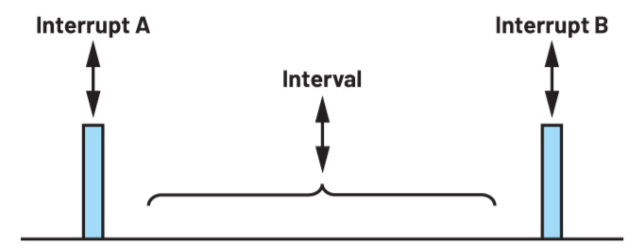

為實現連續數據事務處理,本文將MCU的GPIO27引腳(連接至ADC 的DRDY_1引腳)用作中斷觸發引腳。ADC將數據就緒信號發送至 GPIO27時會觸發MCU包含數據事務處理命令的中斷回調函數。如圖5所示,數據采集必須在中斷A和中斷B之間的時間間隔內進行。

圖5. 兩次中斷的時間間隔。

利用ADI的SPI驅動程序可以在ADC和MCU之間輕松實現數據事務處理。但是,由于驅動程序內存在冗余命令,ADC的ODR會被限制在8 kHz。本文盡可能地精簡了代碼以加快ODR,將介紹實現DMA 數據事務處理的兩種方法:基本模式的DMA事務處理和乒乓模式 的DMA事務處理。

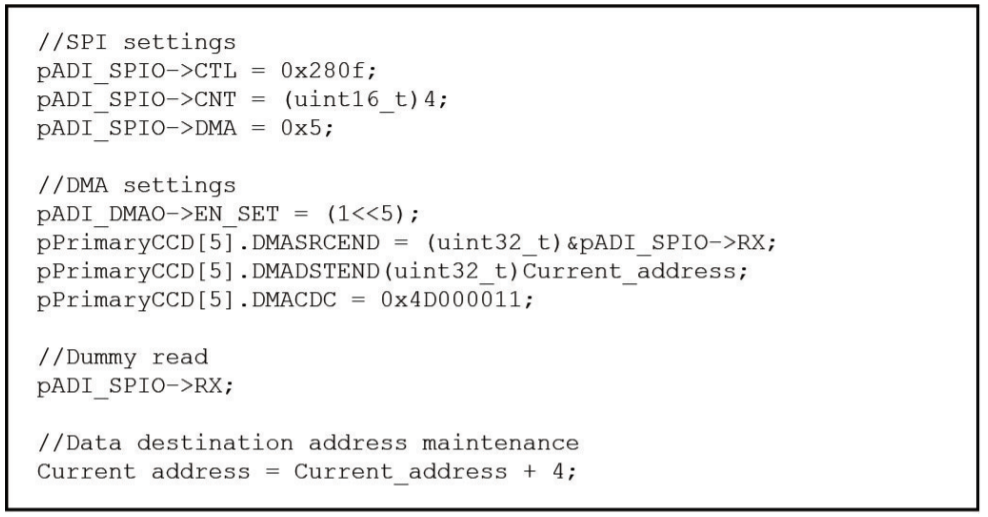

基本模式的DMA事務處理

在實現每個DMA事務處理之前需要對SPI和DMA進行配置(參見圖6 中的示例代碼)。SPI_CTL為SPI配置,其值為0x280f,源于ADI的SPI 驅動程序的設定值。SPI_CNT為傳輸字節數。由于每個DMA事務處理只能發送固定的16位數據,因此SPI_CNT必須是2的倍數。本例設置SPI_CNT為4,以滿足ADC的24位的輸出數據要求。SPI_DMA寄存器為SPI的DMA使能寄存器,設定其值為0x5以使能DMA接收請求。命令pADI_DMA0->EN_SET=(1<<5)使能第五個通道的DMA,即SPI0 RX。

圖6. 基本DMA事務處理模式的代碼。

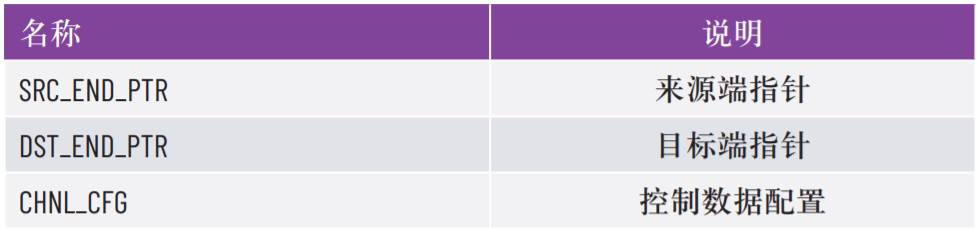

每個DMA通道都有一個DMA結構寄存器,如表3中所示。需要指出的是,這里的數據來源地址的結尾(即SPI0 Rx,亦即來源端指針SRC_END_PTR)在整個操作期間無需增加,因為Rx FIFO會自動 將寄存器中的數據推送出去。另一方面,數據目標地址的結尾(即目標端指針DST_END_PTR)根據ADI的SPI驅動程序的使用函數計算得出,即目標地址+ SPI_CNT -2。

表3. DMA結構寄存器

當前地址為內部數組緩沖區的地址。DMA控制數據配置CHNL_CFG 包括來源數據大小、來源地址增量、目標地址增量、剩余傳輸次數和DMA控制模式等設置,其值0x4D000011按照表4中所述的設置配置。

表4. 控制數據配置0x4D00011的DMA配置

SCLK時鐘通過偽讀取命令SPI_SPI0 -> RX啟動,輸出數據通過MISO 從ADC傳至MCU。MOSI上其它的數據傳輸可以忽略不計。一旦完成 Rx的FIFO填充,DMA請求就會生成從而激活DMA控制器,以將數據從 DMA來源地址(即SPI0 Rx FIFO)傳輸至DMA目標地址(即內部數組的緩沖區)。值得注意的是,SPI_DMA=0x3時會生成Tc請求。

最后,通過將當前目標地址加4的方式將目標地址用于下一個4 字節的傳輸。

請注意,SPI0 DMA通道的pADI_DMA0->DSTADDR_CLR和pADI_ DMA0->RMSK_CLR必須在首次中斷觸發之前在主函數中設置。前一個為DMA通道目標地址減量使能清零寄存器,用于在增量模式下設置每次DMA傳輸后的目標地址移位(目標地址計算函數僅在增量模式下有效)。后一個為DMA通道請求屏蔽清零寄存器,用于將通道的DMA請求狀態清零。

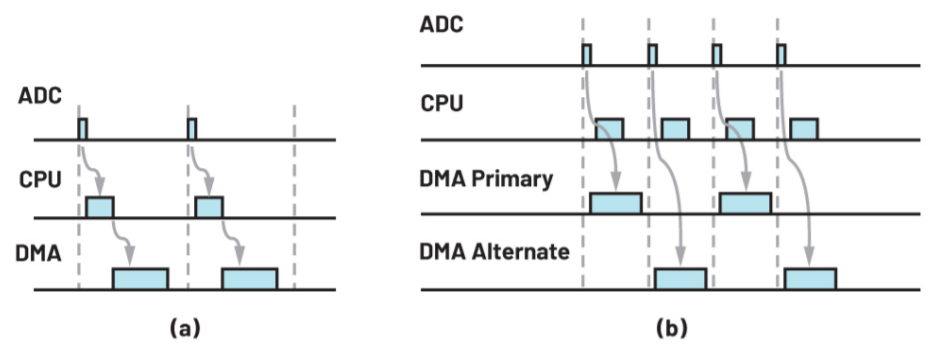

基本模式的DMA事務處理時間圖如圖7a所示。圖中三個時隙分別代表DRDY信號、SPI/DMA設置和DMA數據事務處理。在該模式中,CPU的空閑時間較多,因此希望DMA控制器在處理數據傳輸時能將任務分配給CPU。

圖7. (a)基本模式DMA和(b)乒乓模式的時間圖。

乒乓模式的DMA事務處理

在執行偽讀取命令后,DMA控制器會開始數據事務處理,從而使得MCU的CPU處于空閑狀態而不處理任何任務。如果能夠讓CPU和 DMA控制器同時工作,那么任務處理就從串行模式轉變為并行模式。這樣,就可以同時進行DMA配置(通過CPU)以及DMA數據事務處理(通過DMA控制器)。為實現這一思路,需要設置DMA控制器處于乒乓模式。乒乓模式將兩組DMA結構進行了整合:主結構和備用結構。每次DMA請求時,DMA控制器會在兩組結構之間自動切換。變量p的初始設置為0,其值表示是主DMA結構(p = 0) 還是備用DMA結構(p = 1)負責數據事務處理。如果p = 0,則在收到偽讀取命令時啟動主DMA結構進行數據事務處理,同時會為備用DMA結構分配值,使其在下一個中斷周期內負責數據事務處理。如果p = 1,則主結構和備用結構的作用互換。當僅有主結構處于基本DMA模式時,在DMA事務處理期間對DMA結構的修改會失敗。乒乓模式使得CPU能夠訪問和寫入備用DMA結構,而DMA控制器可以讀取主結構,反之亦然。如圖7b所示,由于DMA的結構配置是在最后一個周期內完成的,因此在DRDY信號從ADC傳送至 MCU后DMA數據事務處理可以被立即執行,使得CPU和DMA同時工作而無需等待。現在,ADC的ODR得到了提升空間,因為總的工作時間已大大縮短。

中斷處理程序的優化

兩次DRDY信號之間的時間間隔不僅包括了中斷回調函數的命令執行時間,還包括了ADI的GPIO中斷處理函數的命令執行時間。

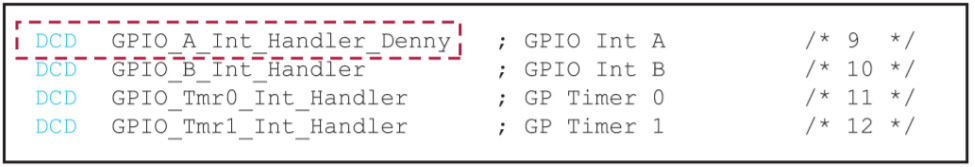

當MCU啟動時,CPU會運行啟動文件(即startup.s)。所有事件的處理函數均在該文件中定義,包括GPIO中斷處理函數。一旦觸發GPIO中斷,CPU就會執行中斷處理函數(即ADI的GPIO驅動程序中的GPIO_A_INT_HANDLER和GPIO_B_INT_HANDLER)。通用的中斷處理函數會在所有的GPIO引腳中搜索觸發中斷的引腳并清零其中斷狀態、運行回調函數。由于DRDY是本文應用的唯一中斷信號,因此可以對函數進行簡化以加快進程。可選的解決方案包括 (1)在啟動文件中重新定位目標,以及(2)修改原始的中斷處理函數。重新定位目標意味著自定義中斷處理函數,并替換啟動文件中的原始的中斷處理函數。

而修改原始的中斷處理函數只需要添加一個自定義的GPIO驅動程序。本文采用第二種方案修改原始的中斷處理函數,如圖8所示。該方案只將連接至DRDY的GPIO的引腳中斷狀態清零,并直接轉到回調函數。請注意,這里需要通過取消選擇build target中關于原始GPIO驅動函數的勾選框內容來隔離原始的GPIO驅動程序。

圖8. 嵌套矢量中斷控制器(NVIC)。

結果

速率性能

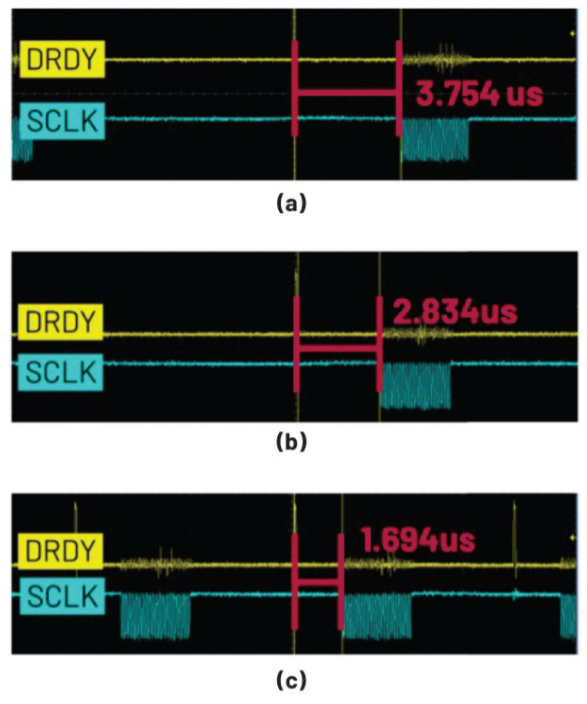

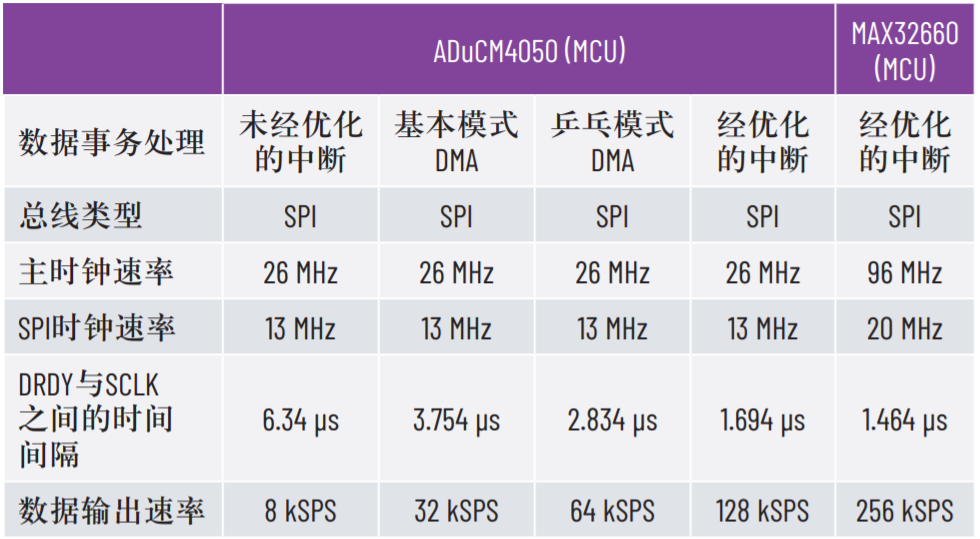

假定現在需要讀取200個24位的ADC輸出數據,并且SPI位速率設置為13 MHz。將DRDY信號和SCLK信號的引腳連接至示波器,可以通過觀察DRDY信號與SPI數據事務處理(亦即DMA事務處理)啟動之間的時間間隔的方法可以量化本文所述的每種方法對速率的改善程度。這里將DRDY信號至SCLK信號開始的時間間隔記為?t,那么對于13 MHz的SPI速率,測量得出的?t為:

(a)基本模式DMA Δt = 3.754 μs

(b)乒乓模式DMA Δt = 2.8433 μs

(c)乒乓模式DMA(使用優化的中斷處理函數)Δt = 1.694 μs

方法(a)和(b)可支持64 kHz的ODR,而方法(c)可支持128 kHz的ODR。這是因為方法(c)的?t最短,從而使得SCLK信號能夠更早結束。如果 SCLK信號(即數據事務處理)能在T/2之前完成(T為當前ADC的數據輸出周期),則ODR可實現翻倍。這較之于原始的ADISPI驅動程序可以達到的8 kHz的ODR性能是一次巨大的進步。

圖9. (a)基本模式DMA、(b)乒乓模式以及(c)乒乓模式(使用優化的中斷處理函數)的Δt。

使用MAX32660控制AD7768-1

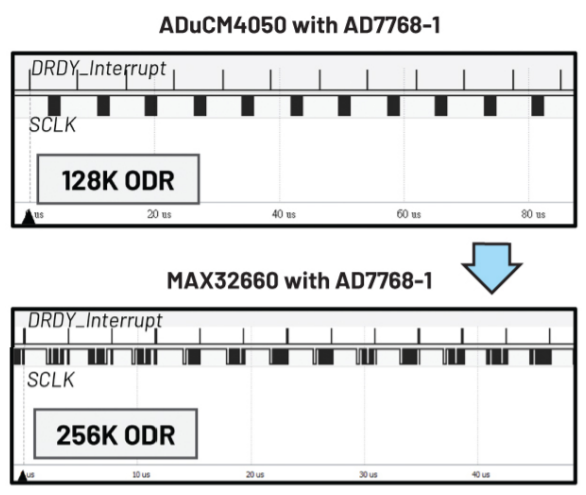

使用主時鐘速率為96 MHz的MCU MAX32660控制AD7768-1)時的結果如何?在該情況下,使用優化的中斷處理函數的中斷設置,可在不使用DMA函數的情況下實現256 kHz的數據輸出速率。參見圖10。

圖10. 不使用DMA時MAX32660的ODR。

結論

本文利用選定的ADC(AD7768-1)和MCU(ADuCM4050或MAX32660)通過 SPI實現了高速的數據事務處理。為實現速率優化的目標,本文簡化了ADI的SPI驅動程序執行數據事務處理。此外本文提出,激活DMA控制器釋放內核也可以加快連續數據事務處理的流程。在 DMA的乒乓模式下,DMA的配置時間可通過適當的調度來節省。在此基礎上,還可以通過直接指定中斷引腳的方式優化中斷處理函數。在13 MHz的SPI位速率下,本文提出的方案的最佳性能可達到128 kSPS的ADC ODR。

表5. 使用ADuCM405和MAX32660實現的高速SPI連接

來源:ADI智庫

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理

審核編輯 黃宇

-

mcu

+關注

關注

146文章

16986瀏覽量

350298 -

adc

+關注

關注

98文章

6430瀏覽量

544079 -

數據采集

+關注

關注

38文章

5903瀏覽量

113514 -

SPI

+關注

關注

17文章

1700瀏覽量

91317 -

驅動程序

+關注

關注

19文章

826瀏覽量

47956

發布評論請先 登錄

相關推薦

pcie設備驅動程序安裝步驟

硬盤電機怎么驅動程序?它有什么典型特征?

Linux設備驅動程序分類有哪些

linux驅動程序如何加載進內核

linux驅動程序主要有哪些功能

linux驅動程序的編譯方法是什么

linux驅動程序運行在什么空間

怎么編寫Framebuffer驅動程序

使用TSIP驅動程序(Azure RTOS)的TLS實現示例

ch341a驅動程序無法使用

能否用MCU訪問非標準SPI接口?

如何優化MCU SPI驅動程序以實現高ADC吞吐速率

如何優化MCU SPI驅動程序以實現高ADC吞吐速率

評論