NCP51820 是一款 650 V、高速、半橋驅動器,能夠以高達 200 V/ns 的 dV/dt 速率驅動氮化鎵(以下簡稱“GaN”) 功率開關。只有合理設計能夠支持這種功率開關轉換的印刷電路板 (PCB) ,才能實現實現高電壓、高頻率、快速dV/dt邊沿速率開關的全部性能優勢。本文將簡單介紹NCP51820及利用 NCP51820 設計高性能 GaN 半橋柵極驅動電路的 PCB 設計要點。

NCP51820 是一款全功能專用驅動器,為充分發揮高電子遷移率晶體管 (HEMT) GaNFET 的開關性能而設計。與擊穿電壓額定值相似的硅器件相比,制造 GaNFET 所使用的芯片尺寸更小。因此,哪怕與同類最佳的硅 MOSFET 相比,GaNFET 的柵極電荷、輸出電容和動態導通電阻也大大降低。此外,GaNFET 沒有 PN結,因此漏極-源極上沒有本征寄生體二極管,也就沒有與第三象限操作相關的反向恢復電荷。

GaNFET 非常適用于離線半橋功率拓撲、無橋 PFC 和單端有源箝位拓撲。這些功率級常常采用零電壓開關 (ZVS),但也可以在硬開關條件下采用大約 400V 的電壓工作。所有這些改進使得 GaNFET 能夠以 MHz 范圍或接近該范圍的頻率開關,漏源邊沿速率高達 100V/ns。能否實現基于 GaN 的功率級的最優性能,在很大程度上取決于設計人員對寄生電路元件(如封裝電感、PCB 走線電感、變壓器電容)以及元器件選擇和布局的理解。雖然硅 MOSFET 功率系統中也存在這些寄生元件,但在 GaN 功率解決方案中,當受到其中存在的高 dV/dt 和 di/dt 激勵時,會有更明顯的響應,因此會產生問題。

NCP51820 的 MLP 無引線功率封裝(圖 3)以及行業中的各種無引線 GaNFET 功率封裝(圖 1 和圖 2),體現了為充分降低寄生電感所作的設計努力。同樣,必須特別注意 PCB 設計和元器件布局。為了充分發揮利用 NCP51820 驅動高速半橋功率拓撲中使用的 GaN 功率開關的優勢,有一些重要的 PCB 設計因素需要考慮,本白皮書將重點討論其中的一些重要注意事項。

HEMT GaN 和 NCP51820 封裝說明

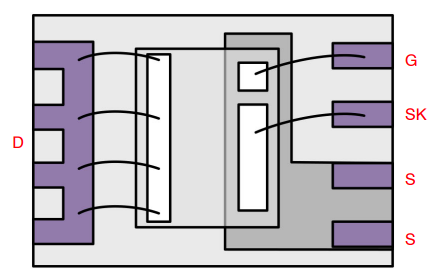

大多數 GaNFET 封裝包含一個專用源極開爾文返回引腳,如圖 1 中的“SK”所示,其作用只是為了將柵極驅動返回電流送回 NCP51820。較高電流的漏源引腳通過多條焊線焊接到多個焊盤,不過為了簡明起見,圖 1 中的簡化示意圖僅顯示了一條焊線連接。NCP51820 輸出和 GaNFET 柵源開爾文引腳之間的接口必須是直接單點連接,該接口特別重要,如含有源極開爾文引腳的 GaNFET 部分所述。

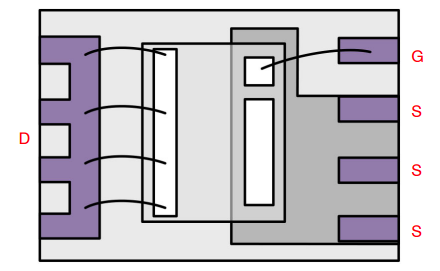

但是,并非所有 GaNFET 都包含一個專用源極開爾文返回引腳,例如圖 2 所示的示例。對于不含源極開爾文返回引腳的 GaNFET,為 PCB 設計中的柵極驅動部分布線時必須特別注意。對于半橋功率級的開關節點連接,高壓側 GaNFET 的源極直接連接到低壓側 GaNFET 的漏極,構成一個承載高 di/dt 負載電流的高 dV/dt 節點。不建議直接使用此高壓開關節點的柵極驅動返回引腳,如不含源極開爾文引腳的 GaNFET 部分所述。

圖1. 含有源極開爾文返回引腳的典型 GaN

圖2. 不含源極開爾文返回引腳的典型 GaN

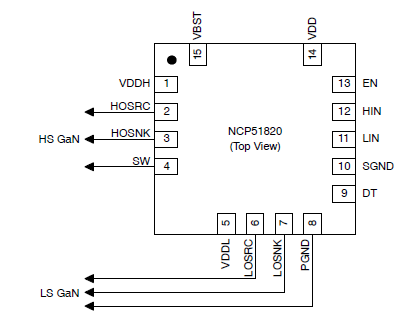

NCP51820 采用 4x4 mm 無引線封裝,所有邏輯電平輸入和編程功能都設置在 IC 右側,與策略性設置在 IC 其余三側的電源功能分開。基于設計策略安置引腳,以便必要時提供高壓隔離。以下 PCB 布局部分說明,將充分展現 NCP51820 引腳分配的優勢。

圖3. NCP51820 GaN 驅動器引腳分配

PCB 設計策略概要

使用 GaNFET 開始 PCB 設計時,最好根據優先級考慮整個布局,如下所列。

1.必須采用多層PCB設計,并且按照本文所述適當使用接地/返回平面。高頻率、高電壓、高dV/dt和高di/dt都要求采用多層PCB設計方法。為了實現基于GaN的功率級的全部優勢,接地平面必須采取適當的布線或設計,而廉價的單層PCB設計無法做到。

2. 開始時,首先將對噪聲最敏感的元器件安置在 NCP51820 附近。VDD、VDDH 和 VDDL 旁路電容以及 VBST 電容、電阻和二極管應盡可能靠近各自的引腳。

3.將 DT 電阻直接放在 DT 和 SGND 引腳之間。

4.HO和LO、拉電流和灌電流柵極驅動電阻應盡可能靠近 GaNFET。

5.將 NCP51820 和關聯的元器件移到盡可能靠近 GaNFET 拉電流和灌電流電阻的位置。

6. 如果可能,安置 GaNFET 時使 HO 和 LO 柵極驅動長度盡可能匹配。為了避免高電流和高 dV/dt 流經過孔,兩個 GaNFET 最好和 NCP51820 位于 PCB 的同一面。

7.應將 HO 和 LO 柵極驅動視為兩個獨立的、相互電隔離的柵極驅動電路。因此,HO 和 LO 各自都需要專用銅觸點 (copper land) 返回平面,這些平面在第 2 層上,位于第 1 層柵極驅動布線正下方。

電源環路、開關節點、柵極驅動環路的正確布線以及使用平面,對于順利完成 GaN PCB 設計至關重要。這部分內容如有需求,后續可能會推送新的文章配合插圖對每一項加以說明。對于柵極驅動器,正確的布線和噪聲隔離將有助于減少額外的寄生環路電感、噪聲注入、振鈴、柵極振蕩和意外導通。目的是設計一個精心考慮了適當接地,同時讓受控電流以最小環路距離流經直接通路連接的高頻電源 PCB。

元器件布局和布線

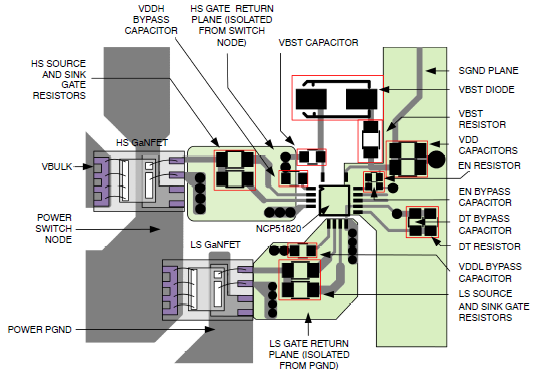

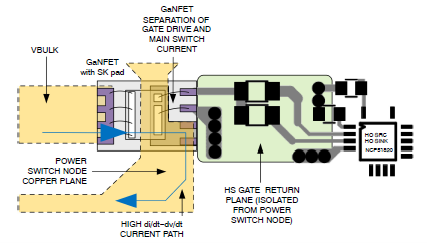

圖 4 突出顯示了 NCP51820 周圍的關鍵元器件布局以及與 HS 和 LS GaNFET 的接口。

圖4. NCP51820 元器件布局

含有源極開爾文引腳的GaNFET

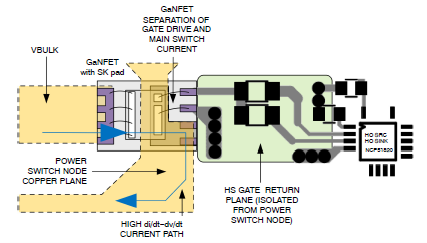

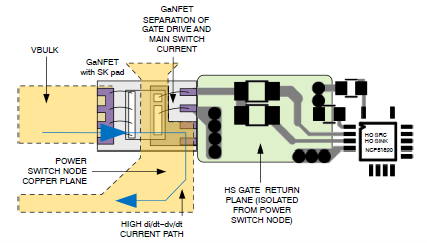

許多 GaNFET 封裝包括一個專用源極開爾文引腳,用于將柵極驅動返回電流與功率開關節點(高壓側)或電源地(低壓側)出現的較高電流和電壓電平隔離。對于具有專用源極開爾文引腳的 GaNFET,柵極驅動布線相當簡單。推薦 PCB 布線設計示例如圖 5 所示,可以看到高壓側 GaNFET 柵極驅動返回電流與功率開關節點電流有效分隔。

圖5. 源極開爾文 GaNFET 布線

不含源極開爾文引腳的GaNFET

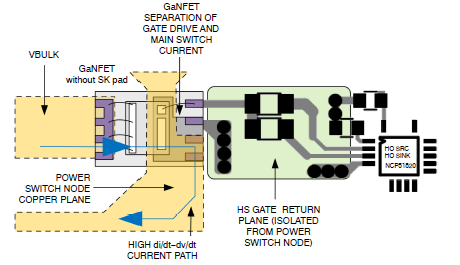

有些 GaNFET 封裝不含專用源極開爾文引腳,還必須要仔細考慮,將柵極驅動返回電流與功率開關節點(高壓側)或電源地(低壓側)出現的較高電流和電壓電平隔離。對于沒有專用源極開爾文引腳的 GaNFET,應從 GaNFET 源極接出一段額外的銅蝕刻線,其唯一作用是將柵極驅動返回電流送回 NCP51820。盡管不如專用開爾文引腳連接那么有效,但這種布線技術仍然可以在柵極驅動電流和功率開關節點之間實現可接受程度的分離。推薦 PCB 布線設計示例如圖 6 所示,可以看到高壓側 GaNFET 柵極驅動返回電流與功率開關節點電流有效分隔。無論何種類型的 GaNFET 封裝,其設計目標都是避免 NCP51820 和支持電路接觸到流過功率級的潛在破壞性開關電壓和電流。

圖6. 無源極開爾文引腳的 GaNFET 布線

來源:安森美

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理

審核編輯 黃宇

-

pcb

+關注

關注

4317文章

23002瀏覽量

396228 -

驅動器

+關注

關注

52文章

8154瀏覽量

145995 -

氮化鎵

+關注

關注

59文章

1613瀏覽量

116156 -

GaN

+關注

關注

19文章

1918瀏覽量

72975

發布評論請先 登錄

相關推薦

如何用集成驅動器優化氮化鎵性能?

干貨 | 氮化鎵GaN驅動器的PCB設計策略概要

干貨 | 氮化鎵GaN驅動器的PCB設計策略概要

評論