1、前言

在 STM32 無線系列產品的 PCB 設計中,需要對射頻部分電路進行阻抗控制,良好的阻抗控制可以減少信號衰減、反射和 EMC 輻射。本篇 LAT 主要介紹印制電路板(PCB)上射頻走線阻抗仿真計算工具的使用方法。使用的計算工具為 Altium Designer V21.1.0,其他專業計算工具有 Si9000,AppCAD 等,使用時可參照本文章設置的方法進行仿真。

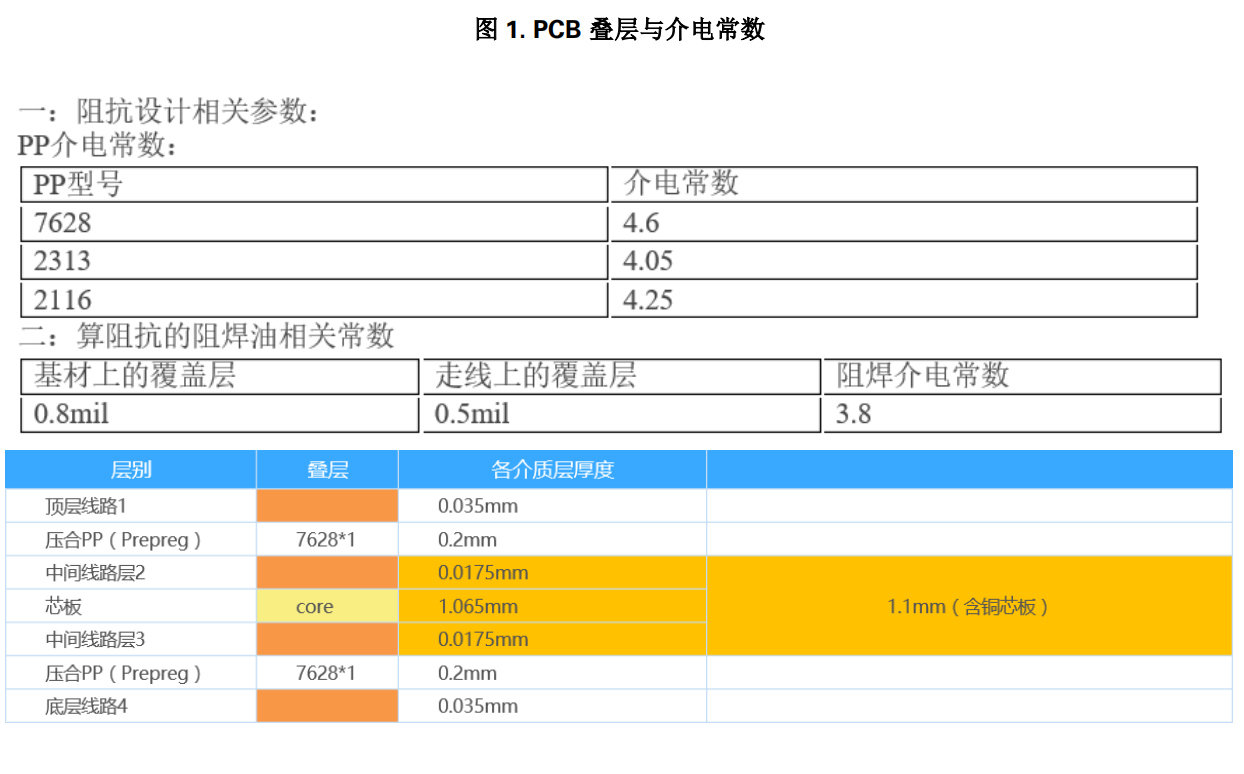

2. PCB 疊層設計

PCB 的疊層里的 Prepreg 類型、線路層的間距以及銅箔厚度都會影響到阻抗,因此需要按照實際 PCB 疊層進行推導計算射頻走線的阻抗。本文選取嘉立創的一個 1.6mm 典型四層板疊層(Prepreg 為 7628)分布為例:

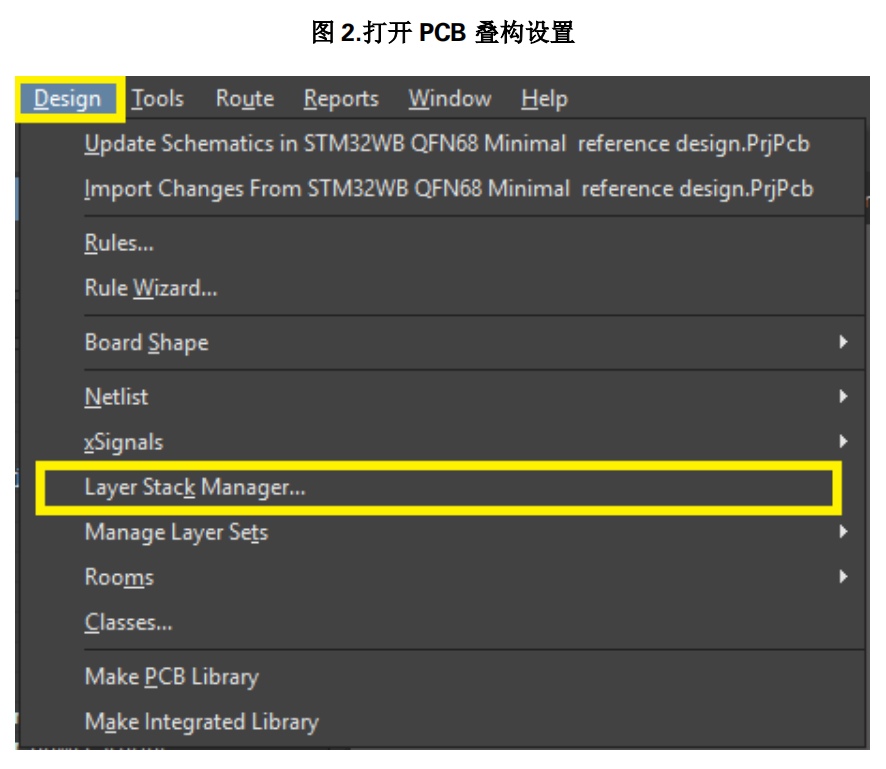

3.Altium Designer 阻抗分析

打開一個 PCB 文件,在 “Design”目錄里找到“Layer Stack Manager”。點擊打開會自

動生成 PCB 文件的 “Stackup”文件。

按照疊層分布圖對“Stackup”進行設置,需要設置線路層的厚度、壓合 Prepreg 厚度以及 FR4 的介電常數。

點擊“Impedance”,再點擊“Add”增加一個阻抗計算表格。射頻走線模型分為單端和差分兩種,

還可以根據參考地平面的不同進行選擇對應的射頻走線阻抗模型。

點選 Top 層,可以更改阻抗線對應的參考層,默認為 L2 GND 層,可以更改為 L3 或者 L4。如果使用

非相鄰層作為參考層,則需要將中間各層對應部分挖空處理。圖 5 是將參考層更改為 L3 時的線寬參數,可以看到線寬明顯變寬了。

下面兩個范例分別為參考地為相鄰層 L2 和參考地為兩側共面加參考層 L2 的仿真結果,仿真的阻抗為單端 50ohm。從結果可以看出增加兩側共面為參考層可以減小阻抗線的寬度。

下面的范例圖 8 為采用 L3 參考層為參考地時的仿真結果,與圖 7 相比,結果顯示由于參考地距離射

頻走線更遠,在保持共面地間距不變的情況下需要更寬的走線來達到同樣的 50ohm 阻抗。如果覺得阻抗線的寬度不理想可以適當調整阻抗線與兩側 GND 之間的間距。

圖 9 為差分 100ohm 阻抗線設置范例,可通過差分線之間的間距,差分線寬度,差分線與兩側 GND間距以及參考平面來調整阻抗。

小結

PCB 板的射頻走線阻抗與射頻性能息息相關,因此在設計射頻電路板時需要根據實際板材的材質、疊層組成以及走線參考地來仿真阻抗。在實際阻抗仿真的過程中,可以通過調節線寬、線間距以及參考面來達到預期的阻抗目標

文檔中所用到的工具及版本

Altium Designer V21.1.0

來源: STM32單片機

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理(

-

射頻

+關注

關注

104文章

5549瀏覽量

167550 -

印制電路板

+關注

關注

14文章

952瀏覽量

40698 -

阻抗

+關注

關注

17文章

940瀏覽量

45818

發布評論請先 登錄

相關推薦

PCB電路板的阻抗工藝中控制要點

X-ray射線無損檢測設備檢測印制電路板

工程師筆記 | 印制電路板射頻走線阻抗計算

工程師筆記 | 印制電路板射頻走線阻抗計算

評論