Cortex-M0處理器允許兩種形式的中斷請求:電平觸發和脈沖輸入。

電平觸發是外設的中斷請求有持續的電平信號,若電平信號在處理器從ISR返回之前沒有被取消,則中斷返回后將再次觸發已經服務過的中斷。

脈沖中斷是在信號的上升沿同步采樣的中斷信號,為了確保NVIC檢測到中斷,外設必須維持中斷信號至少一個時鐘周期,在此期間,NVIC檢測脈沖和鎖存中斷。后續的脈沖可以將暫掛狀態加到活動中斷中,使狀態為中斷活動且掛起。然而,在有限周期內發生的多個脈沖只登記作為中斷調度的單個事件。

哪些中斷是電平觸發的,哪些是脈沖觸發的,具體選擇哪一種是根據芯片設計來決定,不過大多數的外設使用電平觸發中斷輸出。

1. 電平觸發和脈沖輸入

Cortex-M0處理器鎖存所有中斷,外圍中斷成為等待其中一個原因是:

NVIC檢測到中斷信號的上升沿

軟件寫入相應的中斷集掛起寄存器位

掛起的中斷將一直掛起,直到下列情況之一發生:

處理器為中斷進入ISR,這將改變中斷的狀態等待活躍:

對于電平觸發型中斷,當處理器從ISR返回時,NVIC采樣中斷信號。如果中斷信號仍然有效,表示中斷的狀態更改為pending,這可能會導致處理器立即重新進入ISR。否則,中斷的狀態將變為非活動狀態。

對于脈沖觸發型中斷,NVIC繼續監視中斷信號,如果這樣觸發時,中斷狀態變為掛起和活動狀態。在這種情況下,當處理器從ISR返回中斷狀態時,中斷狀態變為掛起狀態可能會導致處理器立即重新進入ISR。如果中斷信號不是脈沖而處理器是在ISR,當處理器從ISR返回中斷狀態變為非活動狀態。

軟件寫入相應的中斷清除寄存器位。

對于電平觸發型中斷,如果中斷信號仍然有效,則中斷的狀態中斷不會改變。否則,中斷的狀態將變為非活動狀態。

對于脈沖中斷,中斷狀態變為:

inactive,如果狀態是pending

active,如果狀態是活動的和掛起的

2. 中斷處理

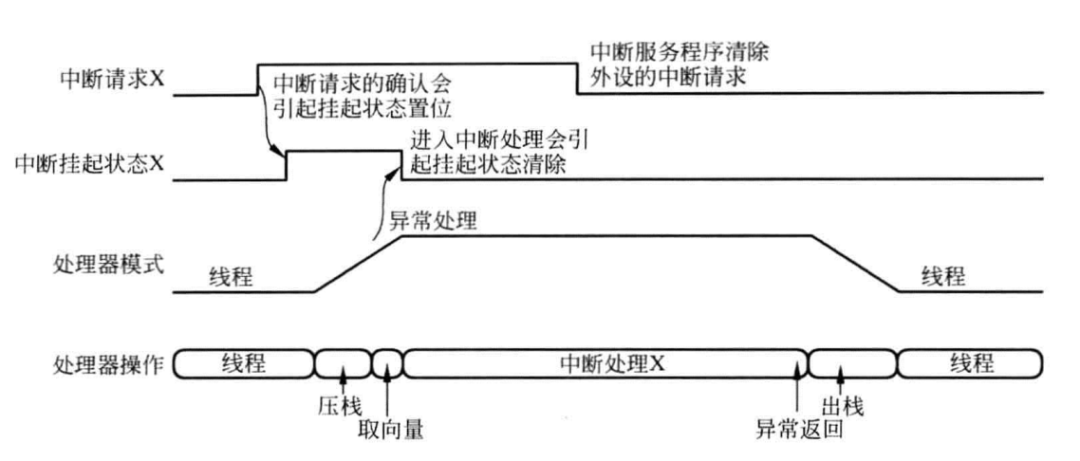

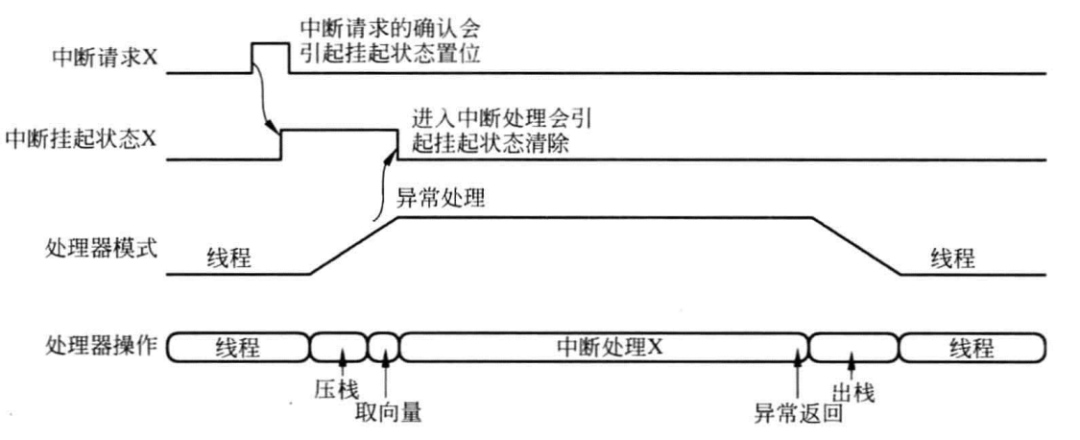

當中斷事件發生時,由于外設連接到了NVIC上,中斷信號就會得到確認。在處理器執行中斷服務并且沒有清除外設的中斷的信號以前,該信號會保持高電平。

在NVIC內部,當檢測到有中斷發生時,該中斷的掛起狀態會被置位,當處理器接受該中斷并且開始執行中斷服務后,掛起狀態就會被清除。

針對脈沖輸入的中斷請求,這種情況下,在中斷得到服務之前,掛起狀態寄存器將會一直保持該請求。

如果中斷請求沒有立即執行,并且在確認之前被軟件清除了,處理器將會忽略掉本次請求,并且不會執行中斷處理。

如果在軟件清除掛起狀態時,外設仍然保持著中斷請求,掛起狀態寄存器還會立即生成。

3. 中斷等待

通常情況下,處理器的中斷等待時間為16個周期,這個等待時間從中斷確認的處理器時鐘周期開始,一直到中斷處理開始執行結束。

計算中斷等待需具備以下前提:

該中斷使能并沒有PRIMASK或者其他正在執行的異常處理所屏蔽

存儲器系統沒有任何等待狀態,在中斷處理、壓棧、取向量表或者中斷處理開始時取指都會用到總線傳輸,如果存儲器系統需要等待,那么總線傳輸時產生的等待狀態則可能使得中斷延遲。

下面幾種情況可能會導致不同的中斷等待:

中斷的咬尾連鎖,如果一個中斷返回時立即產生另外一個中斷請求,處理器就會跳過出棧和壓棧時間,減少了中斷等待時間。

延遲到達,如果中斷發生時,另外一個低優先級中斷正在進行壓棧處理,由于延遲到達,高優先級的中斷就會立即執行,這樣會導致高優先級的中斷等待時間減少。

4. 異常屏蔽寄存器PRIMASK

有些對時間敏感的應用,需要在短時間內禁止響應所有的中斷,對于這種應用,處理器不是直接使用中斷使能、禁止控制寄存器來禁止所有中斷再恢復,而是一個單獨的特殊寄存器 - PRIMASK,通過它可以屏蔽掉除了NMI和HardFault異常的其他的所有的中斷和系統異常。

PRIMASK寄存器只有1位有效,并且在復位后默認為0。該寄存器為0時,所有的中斷和異常都處于允許狀態,設置為1后,只有NMI和HardFault處于使能狀態。

MOVS R0, #0x1 ; //中斷#2 MSR PRIMASK , R0 ; //將R0的值送到PRIMASK

NVIC編程提示軟件使用CPSIE i和CPSID i指令來啟用和禁用中斷。

CPSIE i ; //清除 PRIMASK(使能中斷) CPSID i ; //設置 PRIMASK(不響應中斷)

CMSIS設備驅動庫提供了C語言的實現函數,用戶可以直接使用函數來設置和清除PRIMASK寄存器:

void __disable_irq(void) //不響應中斷 void __enable_irq(void) //啟用中斷

在對時間敏感的程序完成后,應該清除PRIMASK。要不然即使在中斷處理中使用__disable_irq()函數,處理器將停止接受新的中斷請求。主要原因是PRIMASK寄存器和Xpsr是相互獨立的,因此異常返回不會影響中斷屏蔽狀態。

5. NVIC使用提示

確保軟件使用正確對齊的寄存器訪問,處理器不支持對 NVIC 寄存器的未對齊訪問。

即使中斷被禁用,它也可以進入掛起狀態。

禁用中斷只能防止處理器處理中斷。

在對中斷向量表重定義之前,必須包含所有的異常中斷,例如 NMI、HardFault 和外設中斷等。

素材來源 | 極術社區

直接轉載來源:strongerHuang

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理

審核編輯 黃宇

-

處理器

+關注

關注

68文章

19165瀏覽量

229130 -

單片機

+關注

關注

6032文章

44516瀏覽量

633032 -

寄存器

+關注

關注

31文章

5317瀏覽量

120008

發布評論請先 登錄

相關推薦

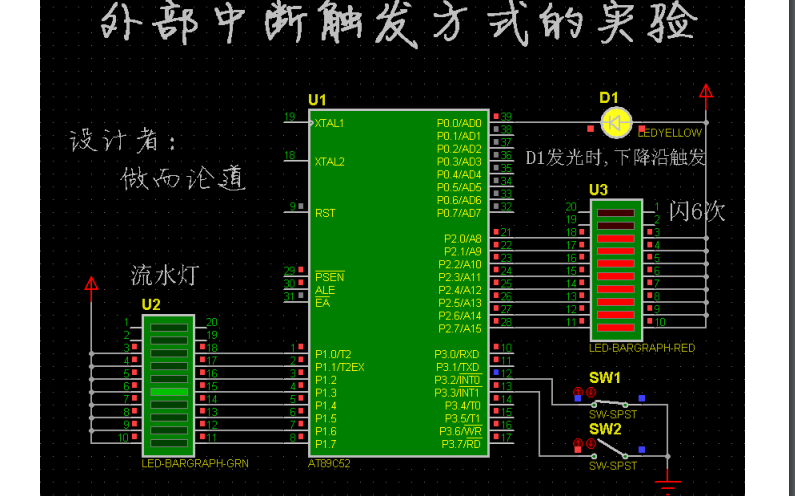

單片機應用系統設計技術——單一外中斷的應用

51單片機之外部中斷應用實例(電平觸發、邊沿觸發)

單片機系統設計技術——外部中斷

單片機中斷電平觸發和脈沖輸入

單片機中斷電平觸發和脈沖輸入

評論