以應用于數模混合信號芯片中的運算放大器為對象,完成芯片設計驗證的全流程,包括運算放大器的電路和版圖設計、設計階段的前仿和后仿驗證、以及對PDK的驗證全流程實驗。

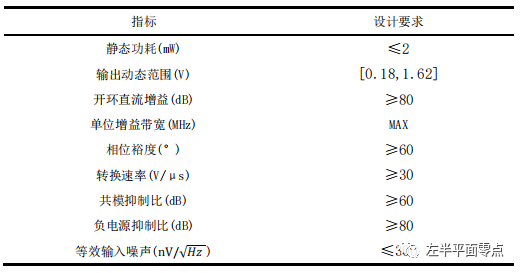

3.設計要求

①使用0.18μm工藝進行設計

②電源電壓:1.8V±10%

③工作溫度:25℃,0℃至50℃,-20℃至85℃,-40℃至+125℃

④詳細指標要求:

4.作品特色

本作品在差分輸入單端輸出的共源共柵運算放大器基本架構的基礎上,大膽嘗試了一種新的設計架構,即故意失配的不對稱結構。與常規的對稱結構相比,節省了大約20%的版圖面積以及10%的靜態功耗。

5.作品介紹

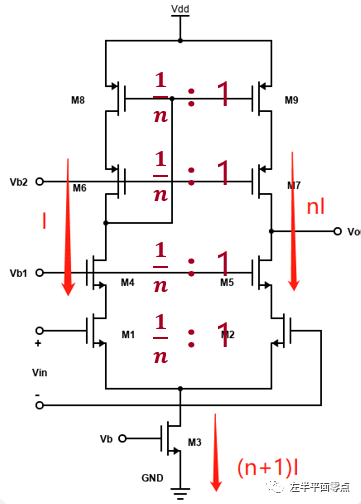

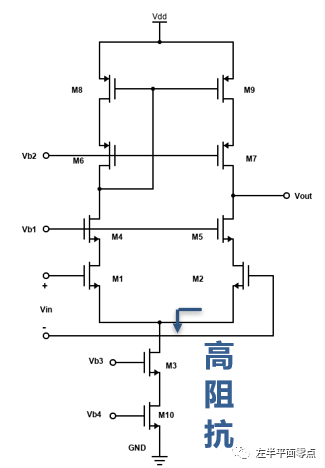

5.1 不對稱結構

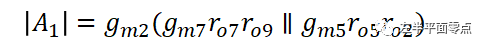

如上圖,為運算放大器的主體部分結構。輸出側采用較大尺寸MOS,非輸出側采用較小尺寸的MOS,兩側尺寸之比n:1,形成故意失配結構,兩側電流之比也為n:1。增益由輸出側視入電阻、輸入對管跨導確定:

此表達式與對稱結構完全一致!同時節省了非輸出側的版圖面積以及靜態功耗,同時能實現對差分信號的處理。

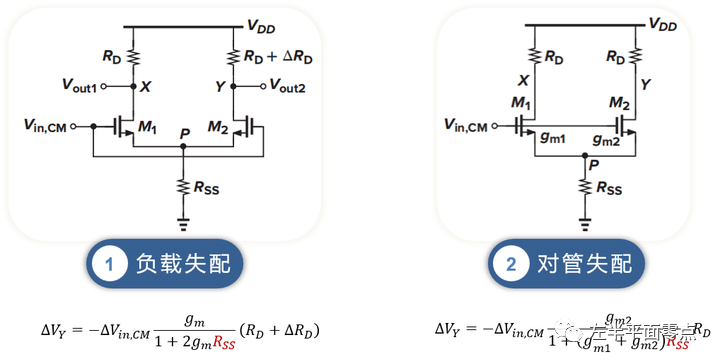

5.2 高等效視入電阻電流源解決共模抑制比的惡化

為了解決故意失配的不對稱結構造成的共模抑制比惡化的問題,本團隊改進了尾電流源,采用雙管堆垛的電流源結構。尾電流源等效視入電阻增加gmro倍,從而同時優化了負載失配以及輸入對管失配造成的從共模到輸出結點的電壓變化。

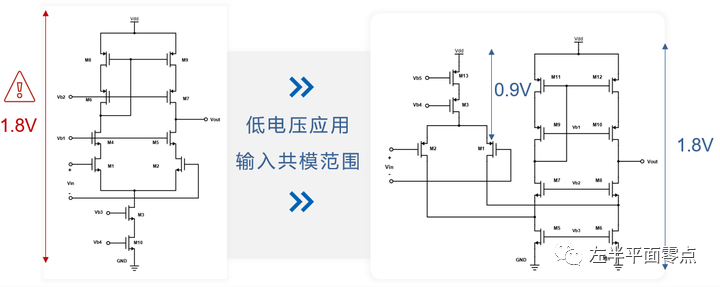

5.3 折疊式結構解決多管堆疊造成的偏置困難

由于采用了共源共柵架構以及上述的雙管堆垛的高等效視入電阻尾電流源架構,運算放大器主體部分單條支路上多達6個晶體管,造成偏置困難、工作不穩定的問題。因此,必須采用折疊式輸入設計,本團隊對運算放大器主體部分做了下圖改進。

5.4 Cascode補償提高帶寬

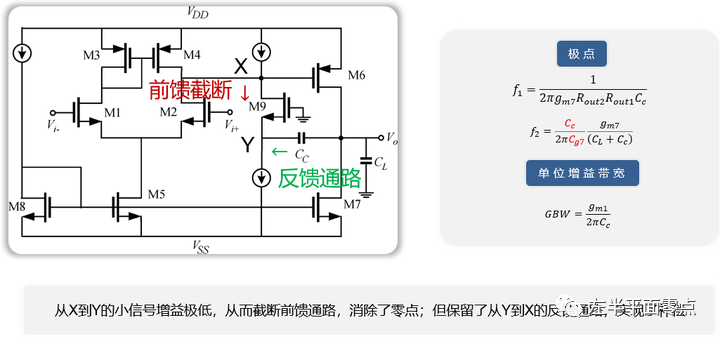

5.4.1 Cascode補償介紹

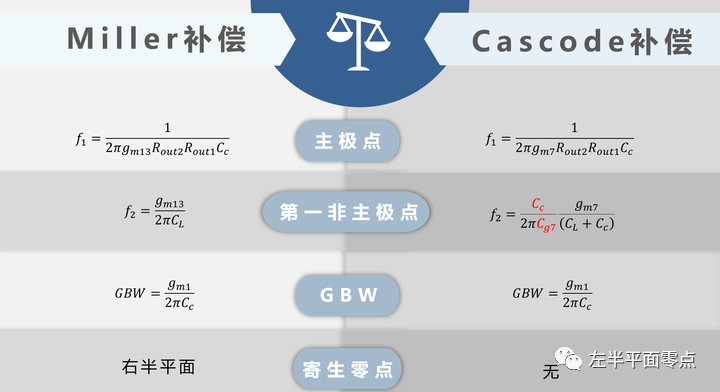

Cascode補償基本結構如下圖。與Miller補償相比,M9截斷了從結點X到結點Y的前饋通路,從而消除了零點。同時,與Miller補償相比,次極點位置也移至更高頻率,使得用更小的補償電容,也具有相當的補償效果,帶寬從而得以提升。

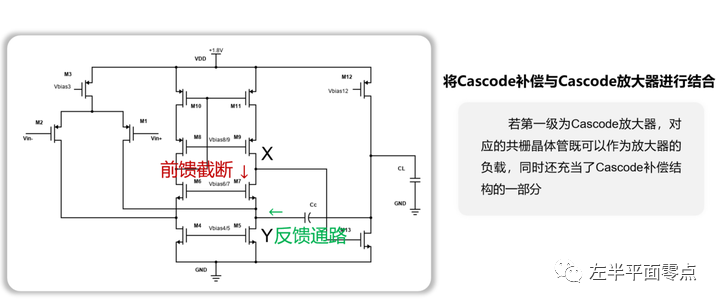

5.4.2 Cascode補償與共源共柵放大器的結合

若第一級為共源共柵放大器,Cascode補償MOS管可以作以下結合:

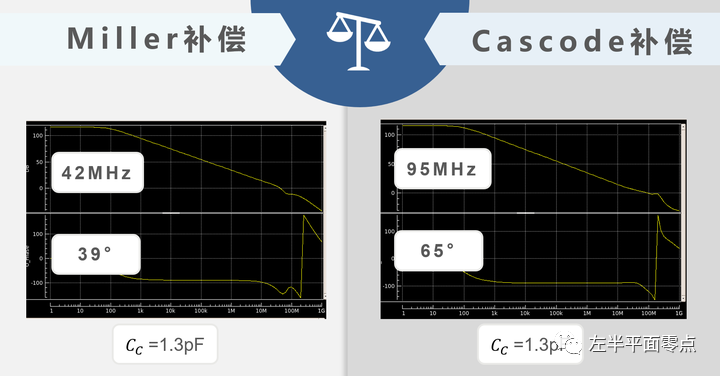

Miller補償與Cascode補償仿真對比如下:

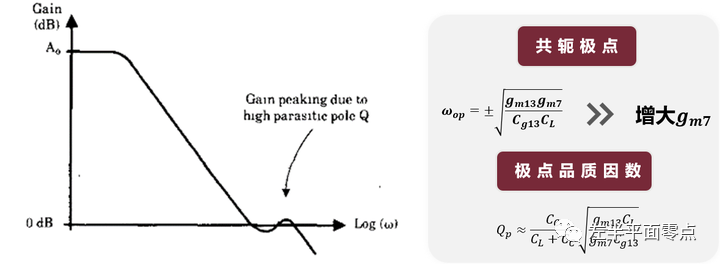

5.4.3 尖峰問題

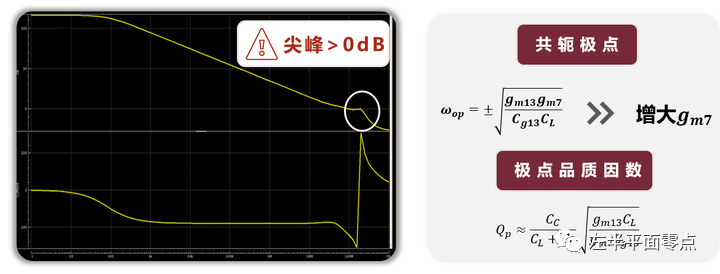

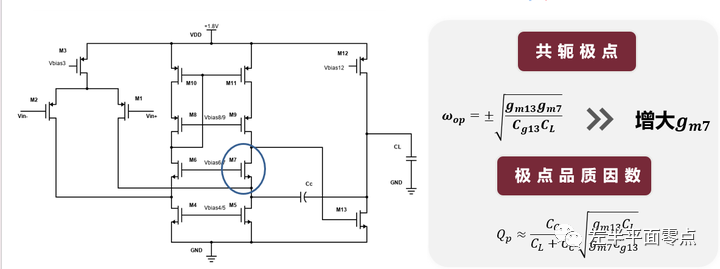

仿真結果顯示,Cascode補償在單位增益帶寬外較近的位置產生了尖峰,主要原因是Cascode補償MOS管M7等效視入電阻并不是無窮大。

由于共軛極點十分靠近單位增益頻率,產生的尖峰對系統穩定性影響十分嚴重,因此需要減小共軛極點產生的尖峰,這需要減小共軛極點的品質因數

-

電阻器

+關注

關注

21文章

3762瀏覽量

62048 -

運算放大器

+關注

關注

215文章

4898瀏覽量

172598 -

MOS管

+關注

關注

108文章

2396瀏覽量

66617 -

電源電壓

+關注

關注

2文章

987瀏覽量

23946 -

共模抑制比

+關注

關注

3文章

79瀏覽量

15933

發布評論請先 登錄

相關推薦

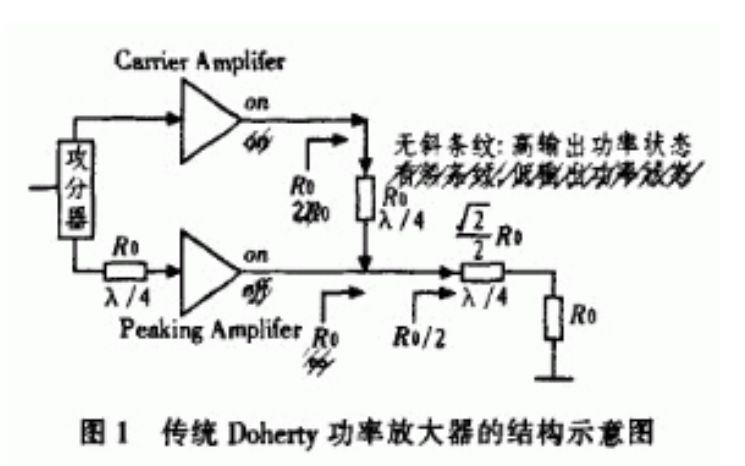

一款滿足WCDMA基站性能要求的不對稱Doberty功率放大器設計

滿足WCDMA基站性能要求的不對稱Doberty功率放大器設計

【2023集創賽】國家集創中心杯三等獎:不對稱輕失配運算放大器

采用不對稱RC雙T反饋電路的選頻放大器分析與設計

不對稱Doherty功率放大器ADS仿真

不對稱Doherty功率放大器ADS仿真與工作原理

基于ADS平臺不對稱Doherty功率放大器的仿真設計[圖]

如何使用ADS平臺設計不對稱的Doherty功率放大器

如何使用ADS仿真不對稱Doherty功率放大器

求一種不對稱輕失配運算放大器的設計方案

求一種不對稱輕失配運算放大器的設計方案

評論