在數字FPGA電路中,作為入門級別的外設除LED燈外,數碼管算是使用頻率最多、應用范圍最廣的一個核心集成外設了,因此學習數碼管的使用非常有必要,下面一起來看看數碼管的顯示原理及其實現方式吧!

1. 數碼管顯示原理

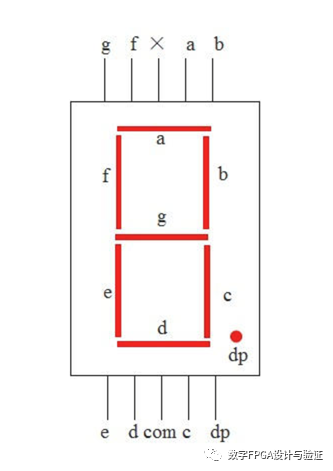

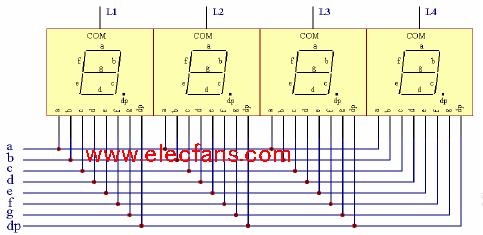

數碼管是電子設計中常用的外設設備之一,用來顯示一些數據數值。常見的數碼管有單個的以及多個共用一起的,那么首先由最簡單的單個數碼管的原理介紹,方便大家的理解。如下圖a所示:

圖a單個數碼管內部結構

這就是一個常見的單個數碼管內部的結構造型,可以理解成7個長方形的LED小燈組成,由這些小燈的亮滅狀況來組成數碼管顯示的不同數值,下面我以手繪圖展示幾個數字的情況,大家應該能更清楚直觀的明白其工作原理,如下圖b所示:

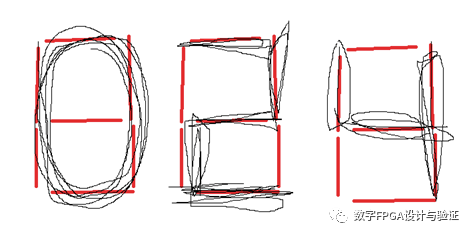

圖b顯示數字024

這里是三個單獨的數碼管,分別顯示數字0、2、4,所以數碼管的原理可以簡單的理解為點亮小燈的組合排列即可(具體內部電路的可以參考后面的附錄,因為其不屬于數字電路的內容,故放在附錄中),明白了數碼管的原理那么再來實現這部分的操作就很簡單啦,下面就一起具體看看是如何實現的吧。

2. 數碼管顯示部分的程序實現

在日常生活中燈的亮滅是通過開關來進行控制,開可以理解為一個高電平的指令,關則相反,而在數字電路中,邏輯電平高低分別用1和0來進行表示,因此要實現點亮數碼管的功能,也就可以通過0和1來進行控制a~g這七個小燈,比如讓數碼管顯示1那么只需要b、c這兩個小燈點亮就可以了,那么下面就來實現數碼管顯示部分的程序,使用的Verilog語言:

module one_digit(

input [3:0] data,

output [7:0] seg

);

reg [7:0] seg;

always @(data) begin

case(data)

4'h0:seg = 8'b11000000;

4'h1:seg = 8'b11111001;

4'h2:seg = 8'b10100100;

4'h3:seg = 8'b10110000;

4'h5:seg = 8'b10010010;

4'h4:seg = 8'b10011001;

4'h6:seg = 8'b10000010;

4'h7:seg = 8'b11111000;

4'h8:seg = 8'b10000000;

4'h9:seg = 8'b10010000;

4'ha:seg = 8'b10001000;

4'hb:seg = 8'b10000011;

4'hc:seg = 8'b11000110;

4'hd:seg = 8'b10100001;

4'he:seg = 8'b10000110;

4'hf:seg = 8'b10111111;

endcase

end

endmodule

以上就是基于的是LUT查找表的原理所寫的單個數碼管顯示的程序。

3. 數碼管程序的驗證

當寫完一部分語法驗證沒有錯誤、編譯能夠成功的程序后,下面要做的就是核心的功能驗證,那么對于上面的數碼管程序如何進行驗證呢?

對于FPGA設計的驗證來說,常見的驗證方式有兩種:a.仿真驗證b.下板驗證,當身邊沒有合適硬件板卡的時候,仿真驗證往往是不錯的選擇,這個時候借助一些EDA工具,可以方便的驗證好設計的程序邏輯功能是否正確,Modelsim就是這樣一款便于仿真驗證的工具,當然進行仿真驗證的時候也需要進行激勵的輸入(編寫一部分代碼),下面對這個數碼管的程序使用仿真驗證的方式看看效果吧,如下圖c所示:

圖c數碼管仿真結果

可以從仿真波形的高低判斷出對應的數碼管內部LED小燈的亮滅情況,由此排列組合推斷出實際的數碼管顯示情況,以此作為仿真驗證判斷的依據,下面給出仿真驗證的程序:

`timescale 1ns/1ns

module TB_one_dight;

reg [3:0]data;

wire[7:0]seg ;

one_digituut(

data,

seg

);

initial begin

data= 0;

#100;

repeat(16)begin

data= data+ 1;

#100;

end

$stop;

end

endmodule

至于實物驗證的部分的話,建議結合相關的硬件板塊配套例程來進行學習驗證,這里就不做板卡推薦了,FPGA板卡以實物配套為文檔教程為準。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602040 -

led

+關注

關注

242文章

23153瀏覽量

658622 -

Verilog

+關注

關注

28文章

1345瀏覽量

109996 -

數碼管

+關注

關注

32文章

1876瀏覽量

90970 -

數字電路

+關注

關注

193文章

1601瀏覽量

80513

發布評論請先 登錄

相關推薦

基于51單片機實現動態數碼管顯示

如何實現多個數碼管同時顯示呢

單片機中的數碼管顯示原理及其實現

靜態數碼管和動態數碼管

數碼管的顯示原理及其實現方式

數碼管的顯示原理及其實現方式

評論