NVME

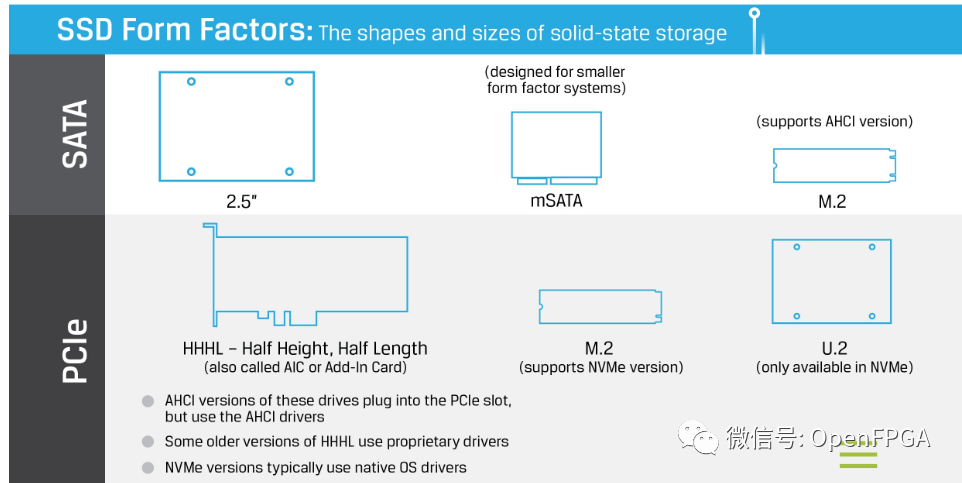

NVM Express ( NVMe ) 或 Non-Volatile Memory Host Controller Interface Specification( NVMHCIS ) 是一種開放式邏輯設備接口規范,用于訪問通過PCI Express總線連接的計算機非易失性存儲介質。NVM 的縮寫代表非易失性存儲器,通常是 NAND 閃存,具有多種物理外形,包括固態驅動器(SSD)、PCIe 附加卡和M.2( mSATA的后繼者 )。

從架構上講,NVMe 邏輯物理存儲在 NVMe 控制器芯片內并由該芯片執行,該芯片與存儲介質(通常是 SSD)物理位于同一位置。NVMe 的版本更改(例如 1.3 到 1.4)已合并到存儲介質中,并且不會影響主板、CPU 等 PCIe 借口兼容組件。

SATA和NVME外形區別 圖片來源:金士頓官網

FPGA實現NVME

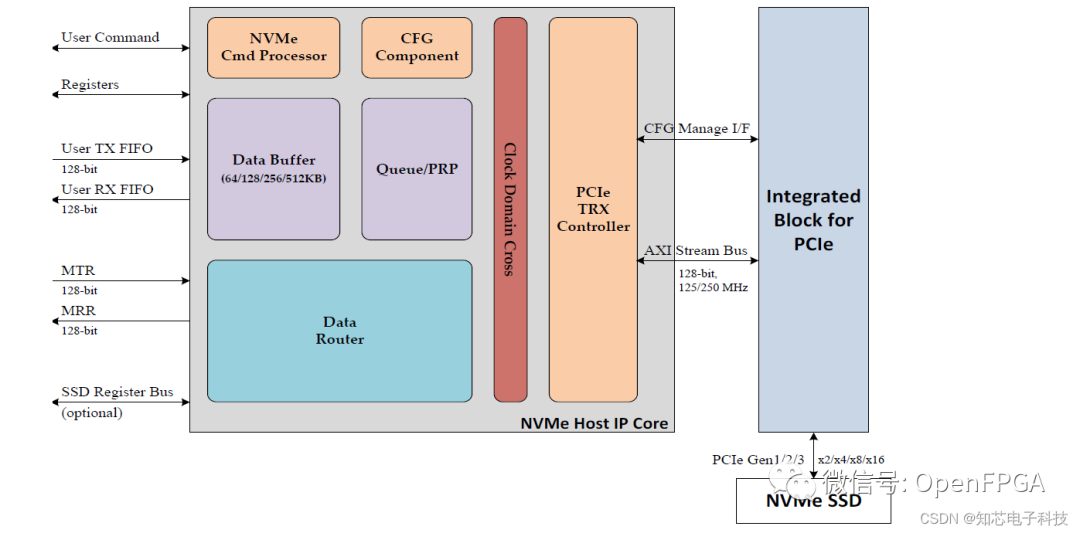

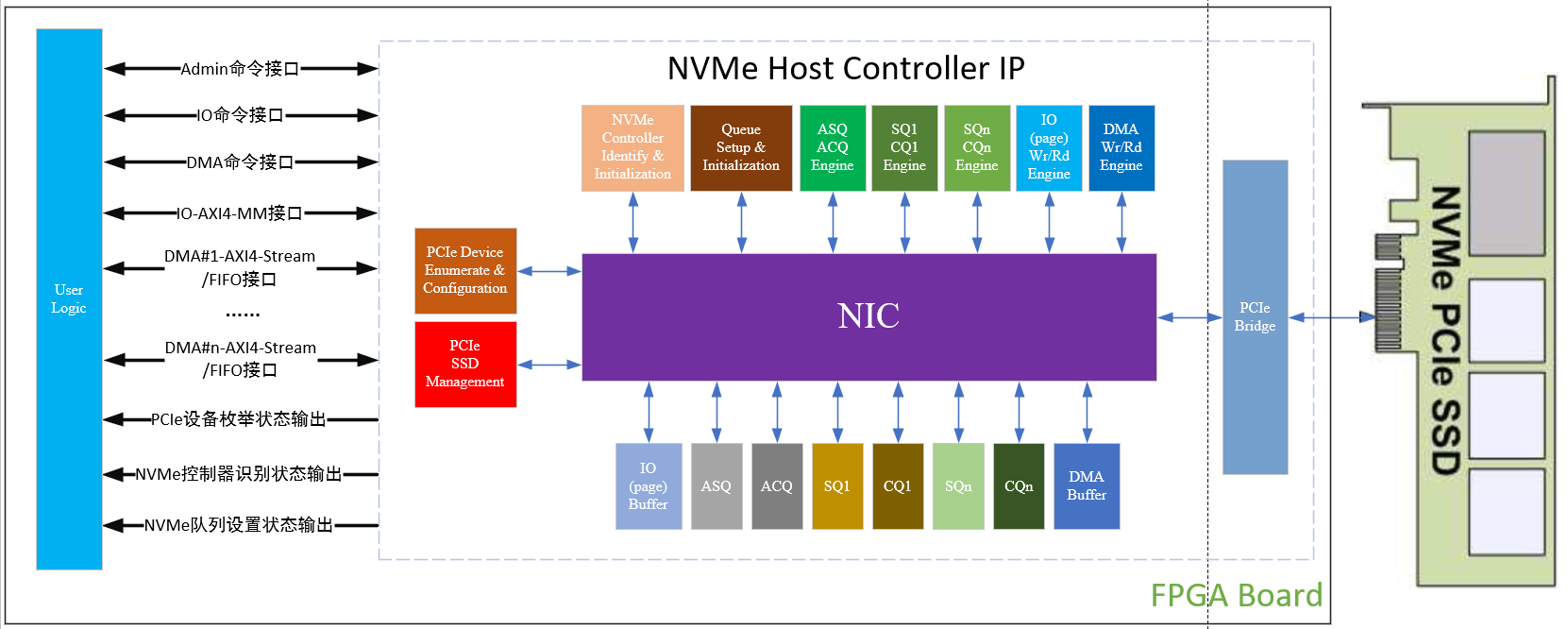

NVMe協議基于PCIe協議之上實現NVMe Host與NVMe SSD之間高速數據通信。FPGA實現的簡單架構如下:

FPGA實現NVME控制(圖片來源見水印)

下面介紹幾個NVME協議的實現的開源項目。

OpenSSD+nvme storage

介紹

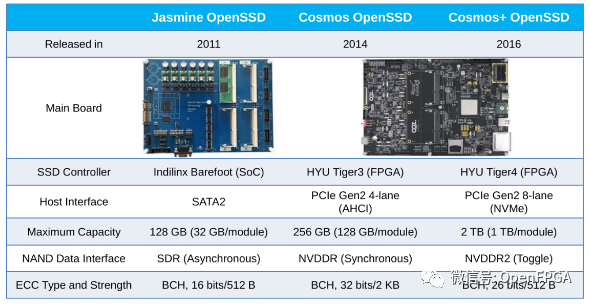

OpenSSD的發展歷史如下:

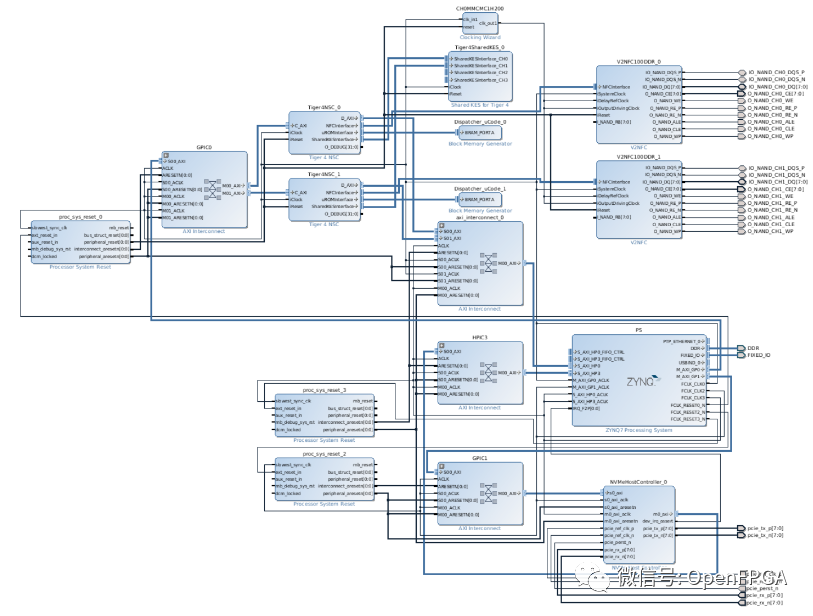

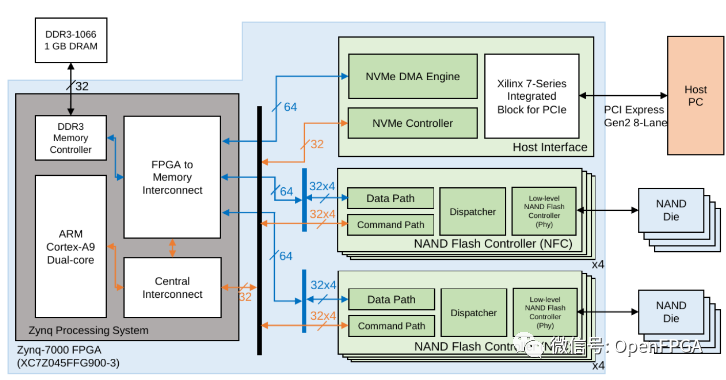

nvme_comp_storage項目是基于OpenSSD的存儲系統,詳細的架構如下:

兩個項目都有異常詳細的文檔介紹,鏈接如下:

其中OpenSSD是有官方網址的,截止發文前,官網訪問受限~

antmicro for nvme

該項目和上面項目類似,唯一的區別就是該項目從底層PCIe到頂層所有的代碼都是自己寫的(在PCIe項目中有介紹),不想借助官方IP的項目,這個項目很具有借鑒意義。

該項目介紹的非常項目,就不贅述了。

NVMe

介紹

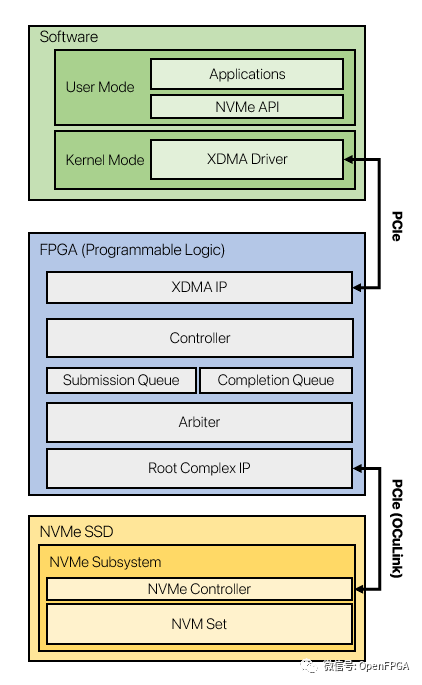

本項目基于AMD-XILINX FPGA XDMA的NVME控制器,詳細的文件架構如下:

NVMe/ ├──hw/(RTLcodes) │├──COMSTRAINTS/(Constraints:Boardconnections) │├──IP/(IPs:ILA,XDMAIP,Boarddesign) │├──RTL/(NVMeHardwareDriverRTLcodes) │├──scripts/ │├──SIM/ │└──SYNTH/(NVMeHardwareDriverProjectdirectories) ├──sw/(NVMesuFileLibrary) ├──SIM/ ├──README.md ├──LICENSE └──CMakeLists.txt

具有硬件加速功能的 NVMe 控制器

介紹

NVMeCHA 是一款超低延遲和高吞吐量的 NVMe 控制器,具有高度并行、流水線和可擴展的架構,具有一個管理控制器和多個完全硬件自動化的 I/O 控制器。管理控制器采用軟硬件協同設計,其中 NVMe 管理命令的復雜處理由軟件管理,而 PCIe 上的數據傳輸由硬件處理。這種混合架構結合了軟件靈活性和硬件效率,減少了 CPU 資源并提高性能。I/O控制器采用高度并行和流水線的硬件架構設計,允許并行處理許多NVMe I/O命令,而無需任何軟件干預。每個I/O控制器對應一個NVMe I/O隊列對。

該項目在 Xilinx KCU105 FPGA 板上進行驗證,該板通過 PCIe gen3 x8 接口連接到計算機。通過SPDK-Perf基準測試工具進行評估,該NVMe控制器的最大讀寫帶寬均可達到7.0GB/s,占理論PCIe帶寬的89%。最大4KB大小的讀/寫吞吐量可以達到每秒170萬次I/O操作(MIOPS)。4KB大小的平均讀/寫延遲僅為2.4μs/3.2μs。

該項目也進行論文發表: IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,doi:10.1109/TCAD.2021.3088784。

pl-nvme

介紹

這個項目也和上面項目類似,不過性能沒有上面的架構強。

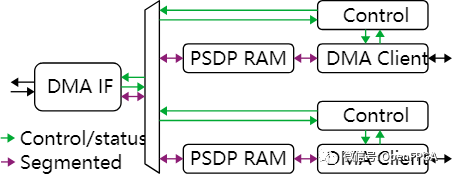

該項目包含 Dune NvmeStorage 系統的源代碼以及簡單的NVMe測試環境,允許使用低級Xilinx FPGA進行接口驗證。

包含FPGA源代碼、仿真環境或 Nvme 測試 FPGA 固件以及 nvme_test 主機軟件。

總結

NVME部分因為基本和FPGA PCIe息息相關,所以基本和PCIe項目同時出現,對于想從底層開始實現的,強烈建議 antmicro 項目。

最后,還是感謝各個大佬開源的項目,讓我們受益匪淺。后面有什么感興趣方面的項目,大家可以在后臺留言或者加微信留言,今天就到這,我是爆肝的碎碎思,期待下期文章與你相見。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601802 -

閃存

+關注

關注

16文章

1777瀏覽量

114808 -

控制器

+關注

關注

112文章

16197瀏覽量

177394 -

Verilog

+關注

關注

28文章

1343瀏覽量

109980 -

nvme

+關注

關注

0文章

217瀏覽量

22582

原文標題:優秀的 Verilog/FPGA開源項目介紹(三十九)- NVMe

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA的模糊PID控制器的設計實現

Xilinx FPGA NVMe Host Controller IP,NVMe主機控制器

Xilinx FPGA NVMe主機控制器IP,高性能版本介紹應用

Xilinx FPGA高性能NVMe SSD主機控制器,NVMe Host Controller IP

高性能NVMe主機控制器,Xilinx FPGA NVMe Host Accelerator IP

高性能NVMe主機控制器,Xilinx FPGA PCIe 3

Flashtec NVMe 3108 PCIe第四代NVMe固態硬盤控制器怎么樣?

使用Verilog實現基于FPGA的SDRAM控制器

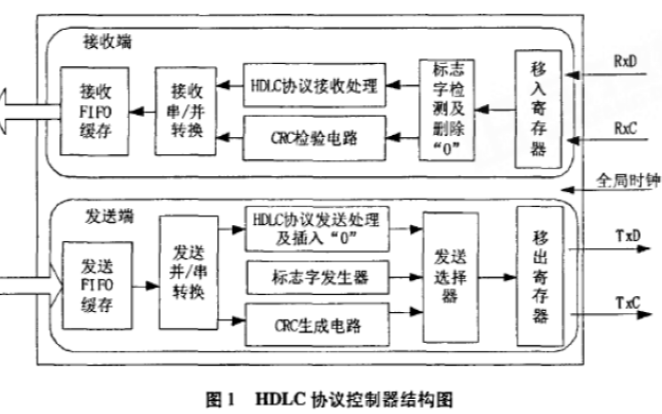

如何使用FPGA實現HDLC協議控制器

實現基于FPGA的SPIFlash控制器設計

基于FPGA的SDRAM控制器的設計與實現簡介

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

基于FPGA實現NVME控制器

基于FPGA實現NVME控制器

評論