點擊上方藍字關注我們

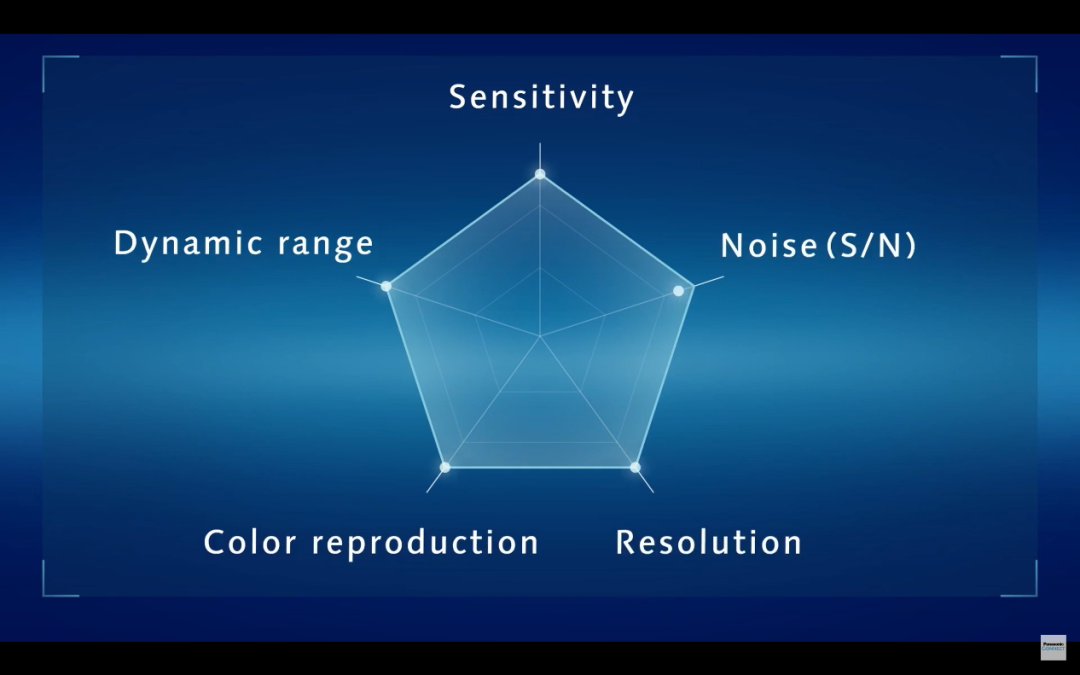

圖像傳感器可以說是在數字視頻或靜止相機中視頻或靜止圖像處理流水線的最重要部分。如果沒有傳感器,就沒有圖像信號可進行處理。眾所周知傳感器是非標準化的。在采用的方案中,它們有以下的不同之處:

轉換可見光或紅外光為電信號的方式;尤其是在該信號離開這塊芯片之前,對這個信號采用的編碼和壓縮(有時)的方式。

對傳感器內部的寄存器進行編程的方式,以調整增益、曝光時間、傳感器模式(如線性、HDR),傳感器圖像坐標等。

實現特殊功能的方式,如高(或寬)動態范圍(HDR/WDR);例如通過在同一封裝中的多個傳感器,對于同一圖像幀多次曝光等。

這些傳感器廠商采用的接口,以使這些電子圖像信號離開傳感器,并進入下游的處理邏輯。

FPGA提供一個具成本效益的,尺寸非常小的可編程邏輯平臺,可以輕松地將信號從不同的圖像傳感器接口轉換到數字信號,以供下游的邏輯進行處理。FPGA提供具有成本效益的可編程機制,以適應各種信號編碼方案、寄存器管理方案和傳感器接口,從而為不同類型的傳感器提供可編程支持。

圖像傳感器技術

根據用于將可見光轉換成電信號的基本技術,圖像傳感器可分為兩大類。它們是CCD(電荷耦合器件)傳感器和CMOS(互補金屬氧化物半導體)傳感器。到目前為止,出貨量最多的圖像傳感器是CMOS傳感器。本文只關注CMOS傳感器接口。

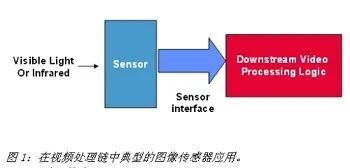

在視頻處理鏈中典型的圖像傳感器的應用如圖1所示。

如今有幾個著名的圖像傳感器制造商,它們是Aptina、OmniVision Technologies、索尼、三星、松下、東芝和Altasens。

如前所述,傳感器制造商配置了一系列接口,用于將離開其芯片的圖像信號傳至下游邏輯進行處理。非常普遍的是,同一傳感器制造商根據需要從芯片中提取的數據量使用不同的接口。例如,具有兆像素分辨率的現代傳感器需要在給定的周期時間傳出比僅具有VGA級分辨率的傳感器多得多的數據。像高動態范圍(HDR)這樣的要求還增加了數據量,需要從每個圖像幀的圖像傳感器讀取數據,而為支持平滑、低延遲高品質的視頻,需要在給定的時間內從傳感器芯片提取幀數,這也影響了傳感器接口的選擇。

圖像傳感器接口的演進

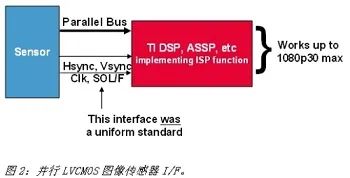

到目前為止,所有傳感器都可連接到并行LVCMOS接口,如圖2所示。傳感器分辨率和幀速率已經提高到一個水平,此時以前的主流CMOS并行接口已不能處理所要求的帶寬。

由于兆像素傳感器的問世,對更高速度的需求激增,HDR和對支持更高幀速率、新型、更高速度傳感器的需求正使用不同的接口來克服并行LVCMOS的局限性。例如,索尼和松下使用并行的子LVDS接口,OmniVision使用MIPI或串行LVDS。另一個例子是,為支持更高帶寬的需求,Aptina Imaging已經推出了稱為HiSPi(高速串行像素接口)的高速串行接口。HiSPi接口可以工作在1-4個串行數據通道,加上1個時鐘通道。每個信號是子LVDS差分信號,以 0.9V的共模電壓為中心。每個通道可以運行在高達700Mbps下。

HiSPi與并行傳感器接口橋接的需求

多個傳感器接口給標準化下游視頻處理邏輯的制造商提出了一個問題,因為用一個ASSP支持許多不同的傳感器接口非常困難。

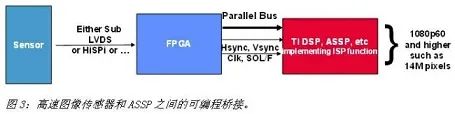

大多數ISP(圖像信號處理)器件支持傳統的CMOS并行傳感器接口,但通常缺乏對高速串行接口的支持。很多ISP并行接口的運行速度遠遠超過了傳感器的并行接口。但是,由于傳感器已遷移到不同串行接口,ISP器件需要邏輯以轉換到并行接口。因此FPGA橋接器件需要將高速串行數據轉換到并行格式。對于視頻信號處理ASSP的制造商(他們擁有支持更快的并行CMOS傳感器接口的現成產品),FPGA解決了連接至高速串行傳感器的問題。FPGA提供在高速傳感器和傳統圖像信號處理ASSP之間的簡單、具有成本效益的可編程橋接。這個概念如圖3所示。

基于FPGA的串行傳感器橋接參考設計示例

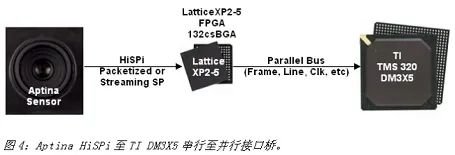

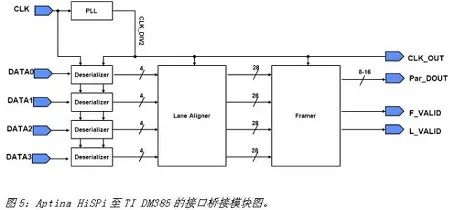

一個實際例子是,針對Aptina Imaging的HiSPi串行接口至TI DSP并行接口的橋接,LatticeXP2-5非易失性FPGA提供了高效、具有成本效益的解決方案,如圖4所示。

該參考設計在輸入端用HiSPi串行接口,在輸出端用TI TMS320DM3X5連接至Aptina傳感器。評估硬件已測試了Aptina的A-1000傳感器MT9M034/MTM024和MT9J003。該參考設計支持分組(Packetized)和Streaming SP HiSPi格式:1-4通道運行速度高達每通道700Mbps。它還模擬并行傳感器輸出,輸出總線寬度為8、10、12、14或16位。并行接口可配置為1.8V、2.5V或3.3V LVCMOS電平。參考設計的模塊圖如圖5所示。

FPGA在傳感器接口橋接上的挑戰

可編程邏輯作為圖像傳感器和ASSP之間的橋接面臨三個方面的挑戰。首先,FPGA必須為接口信號提供電信號支持。第二,FPGA的I/O必須有足夠的gearing邏輯來支持快速串行傳感器接口。第三,FPGA必須提供符合成本效益的非常小的外形尺寸,以適應現代攝像機對于緊湊外形的要求。

具有完備子LVDS文檔支持的LatticeXP2非易失FPGA系列已被證實解決了圖像傳感器橋接的電氣需求。集成PLL、專用時鐘沿和I/O gearing邏輯解決了高速串行傳感器接口。最后,萊迪思半導體(Lattice)的 XP2提供了具有成本效益的8×8mm面積。此外,由于其非易失的特性,LatticeXP2系列器件無需外部引導PROM,從而進一步節省了電路板空間,這使得他們成為傳感器接口的具有吸引力的可編程邏輯平臺。圖像信號處理(ISP)IP的可用性也使更大型的LatticeXP2器件可提供各種功能,如傳感器數據線性化、傳感器寄存器編程、去Bayering、有缺陷的像素校正、伽瑪校正和每個色通道高達24位的簡單HDR。

有你想看的精彩 至芯科技FPGA就業培訓班——助你步入成功之路、9月23號北京中心開課、歡迎咨詢! C語言算法如何移植到FPGA 基于千兆網的FPGA多通道數據采集系統設計

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:基于FPGA的攝像機傳感器接口

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21675瀏覽量

601957

原文標題:基于FPGA的攝像機傳感器接口

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AI圖像識別攝像機

無人機“智慧之眼”:光電吊艙攝像機的全面解析

防跌倒識別攝像機

深入解析CMOS傳感器在監控攝像機中的應用

客流量監測識別攝像機

基坑監測識別攝像機

TIDA-010083-適用于機器視覺攝像機和視覺傳感器的高密度隔離式PoE 和 GigE PCB layout 設計

船只監測識別攝像機

基于FPGA的攝像機傳感器接口

基于FPGA的攝像機傳感器接口

評論