為什么共漏級沒有密勒效應?

共漏級(Common Emitter Configuration)和密勒效應(Miller Effect)是兩個非常常見的電子電路中的概念,它們都是由美國電學家John M. Miller提出的。但是,它們之間卻沒有必然聯系。共漏級沒有密勒效應并不是什么奇怪的現象,這個問題需要從共漏級電路本身和密勒效應兩個角度去分析。

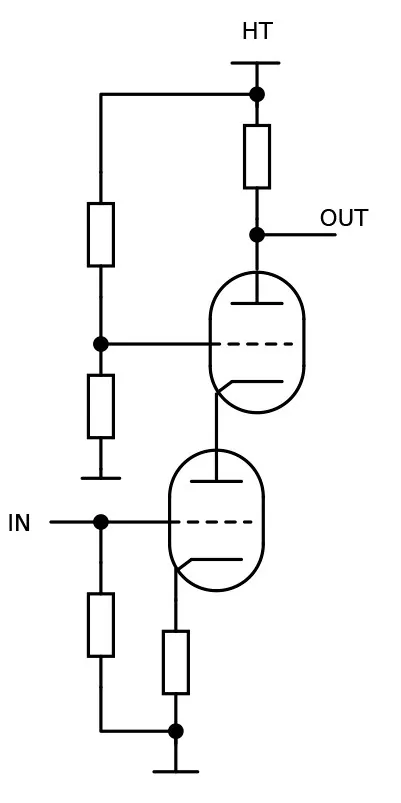

首先,我們需要先了解一下共漏級電路的基本原理。共漏級是晶體管的三種基本放大電路,它具有電流放大和電壓反相的特點。在共漏級電路中,輸入信號通過電容耦合的方式進入晶體管的基極,經過晶體管的放大作用之后被輸出到負載電阻中。在這個過程中,負載電阻的一側通過電容與晶體管的集電極相連,這個電容就是我們常說的旁路電容。旁路電容的作用是將信號進行旁路,降低電路的輸入阻抗。

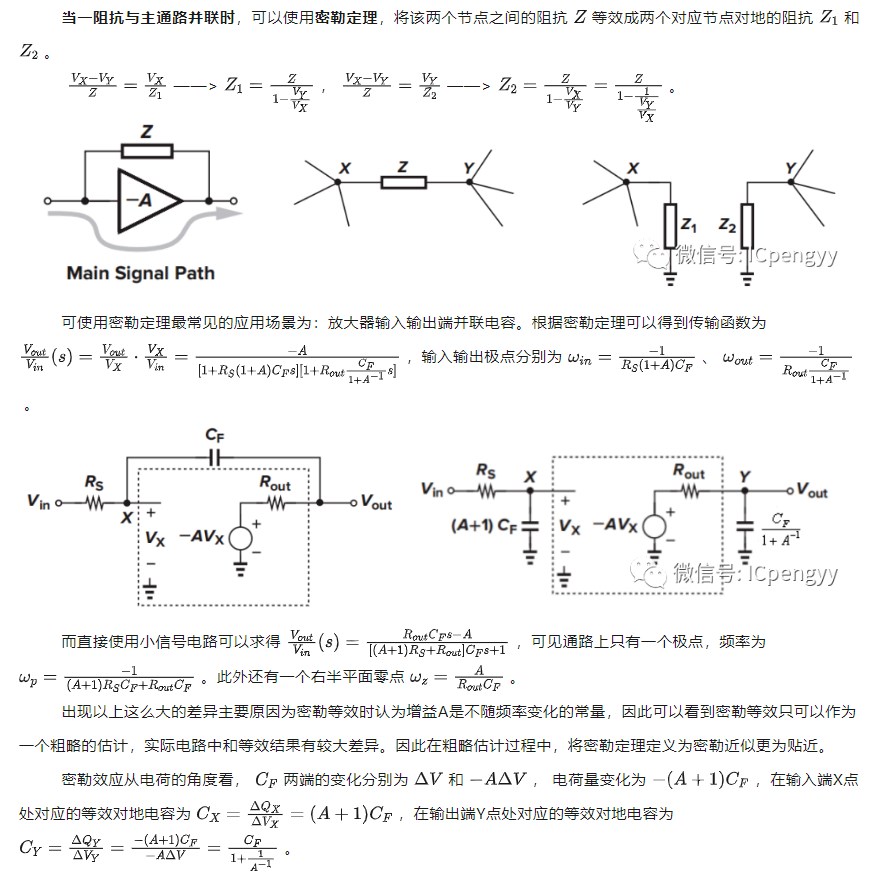

接下來,我們來簡要介紹一下密勒效應。密勒效應是指,在電子管、晶體管等電子元器件中,因信號輸入和輸出之間的電容作用而引起的放大系數下降現象。具體來說,就是當信號輸入端與地相連時,輸出端的反饋電容會對輸入端和輸出端之間的電容產生負面影響,從而降低電路的放大系數。

那么,既然以上兩個概念已經解釋清楚了,為什么共漏級沒有密勒效應呢?這是因為共漏級電路的旁路電容不會引起密勒效應。共漏級電路中,輸出信號是從旁路電容中通過的。由于集電極并沒有像共基級電路中的電容一樣,和晶體管的輸入電容串聯在一起,因此輸出信號不會被旁路電容對地形成的反饋電容所影響。因此,密勒效應對共漏級電路的影響非常微弱。

此外,由于共漏級電路的負載電阻處于集電極端,且經過負載電阻的電壓變化反向于集電極電壓變化,因此對晶體管的電容反饋系數沒有影響,進一步減弱了密勒效應的影響。綜上所述,雖然共漏級電路中存在旁路電容,但其對電路的放大系數并沒有密勒效應產生的影響那么大。

在實際的電子電路設計中,我們需要根據電路所處的實際情況來選擇合適的電路結構以及相應的參數設置。如果需要設計一個帶有高放大系數的電路,共漏級電路是一個非常好的選擇。相反,如果我們需要降低電路的輸入阻抗或者避免其他類型的信號干擾,選擇其他結構的電路則會更為合適。

在總結中,我們可以看到,共漏級電路和密勒效應是兩個不同的概念,共漏級電路不會產生密勒效應。雖然在實際的電路設計中,我們可能在共漏級電路中遇到一些信號過早失真、電路帶寬減小等問題,但與密勒效應相關的并不是其中的旁路電容。因此,我們需要對問題進行具體分析,并選擇合適的解決方案。

-

旁路電容

+關注

關注

7文章

178瀏覽量

24710 -

晶體管

+關注

關注

77文章

9502瀏覽量

136937 -

負載電阻

+關注

關注

0文章

109瀏覽量

7791

發布評論請先 登錄

相關推薦

為什么共漏級沒有密勒效應?

為什么共漏級沒有密勒效應?

評論