SiC FET(即SiC JFET和硅MOSFET的常閉共源共柵組合)等寬帶隙半導(dǎo)體開(kāi)關(guān)推出后,功率轉(zhuǎn)換產(chǎn)品無(wú)疑受益匪淺。此類器件具有超快的開(kāi)關(guān)速度和較低的傳導(dǎo)損耗,能夠在各類應(yīng)用中提高效率和功率密度。然而,與緩慢的舊技術(shù)相比,高電壓和電流邊緣速率與板寄生電容和電感的相互作用更大,可能產(chǎn)生不必要的感應(yīng)電流和電壓,導(dǎo)致效率降低,組件受到應(yīng)力,影響可靠性。此外,由于現(xiàn)在SiC FET導(dǎo)通電阻通常以毫歐為單位進(jìn)行測(cè)量,因此,PCB跡線電阻可能相當(dāng)大,須謹(jǐn)慎降低以保持低系統(tǒng)傳導(dǎo)損耗。

設(shè)定電流邊緣速率

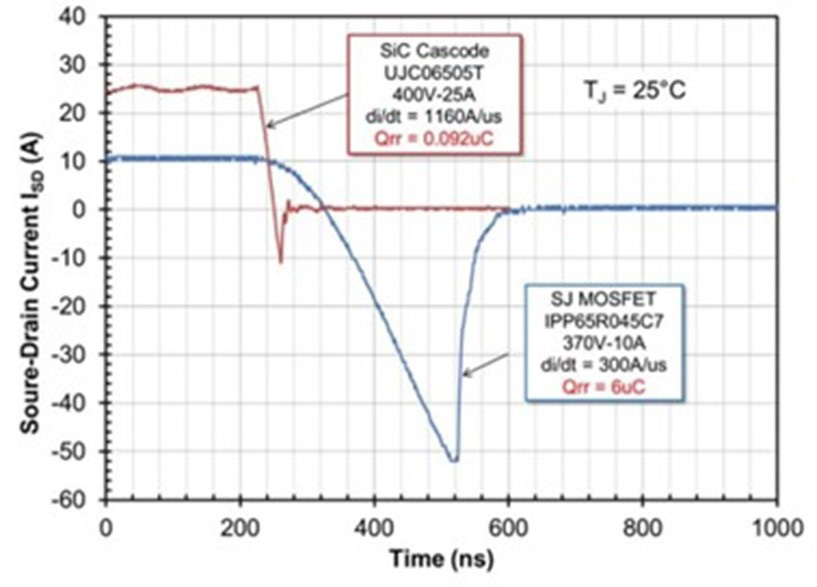

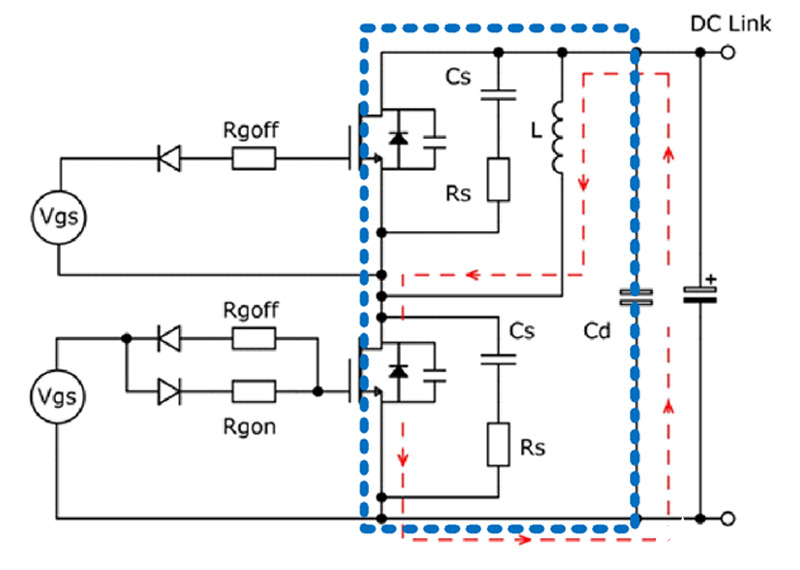

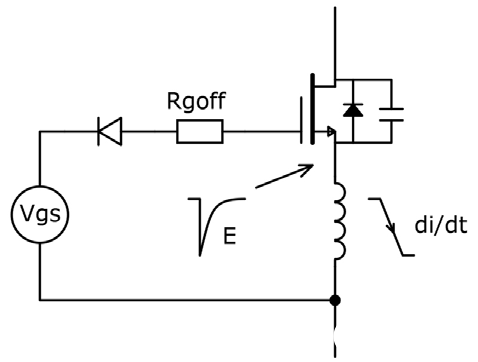

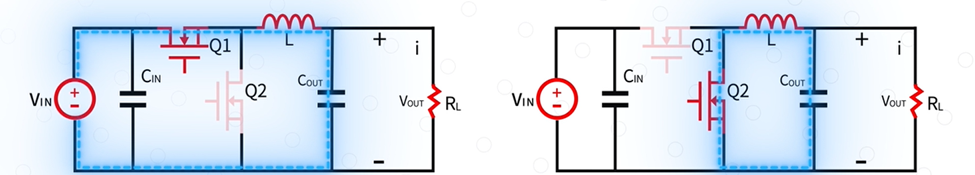

SiC FET可輕松實(shí)現(xiàn)超過(guò)1000A/μs的電流邊緣速率(圖1),這樣SiC FET、其負(fù)載和本地去耦電容之間的開(kāi)關(guān)回路周圍的電感會(huì)產(chǎn)生瞬態(tài)電壓(圖2)。例如,依據(jù)E = -Ldi/dt,100nH回路電感可產(chǎn)生100V的瞬態(tài)電壓,這會(huì)導(dǎo)致器件工作電壓提高、擊穿裕量減少且EMI增加。

圖1 :與同等級(jí)的Si SJ MOSFET相比,SiC FET開(kāi)關(guān)波形顯示 >1000A/μs 的邊緣速率

圖1 :與同等級(jí)的Si SJ MOSFET相比,SiC FET開(kāi)關(guān)波形顯示 >1000A/μs 的邊緣速率

圖2 :具有高di/dt的典型開(kāi)關(guān)回路

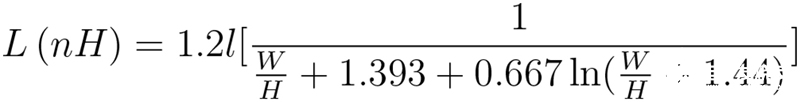

這是真實(shí)的電感值,在典型電源應(yīng)用中,考慮到組件的物理尺寸,無(wú)法將其緊密封裝在一起。例如,根據(jù)Terman的等式1計(jì)算得出,如果寬度(W)為2.5mm且銅重量(T)為2oz (0.07mm),對(duì)于每個(gè) “出發(fā)” 和 “返回” 連接,僅50mm (l) 的PCB跡線可產(chǎn)生大約100nH的總電感。

圖2 :具有高di/dt的典型開(kāi)關(guān)回路

這是真實(shí)的電感值,在典型電源應(yīng)用中,考慮到組件的物理尺寸,無(wú)法將其緊密封裝在一起。例如,根據(jù)Terman的等式1計(jì)算得出,如果寬度(W)為2.5mm且銅重量(T)為2oz (0.07mm),對(duì)于每個(gè) “出發(fā)” 和 “返回” 連接,僅50mm (l) 的PCB跡線可產(chǎn)生大約100nH的總電感。

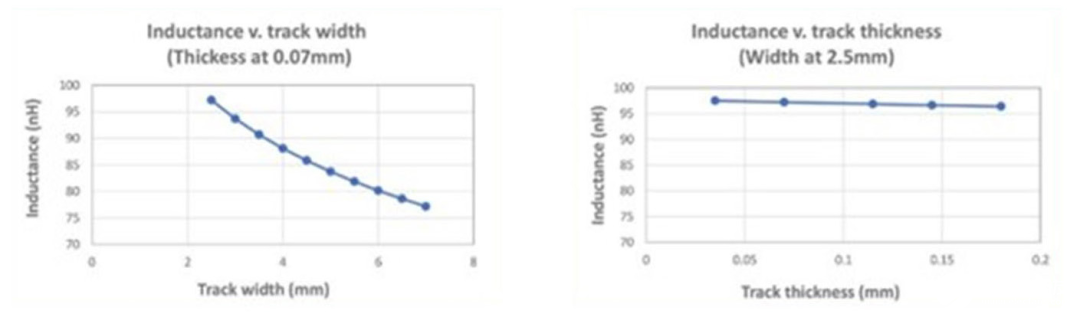

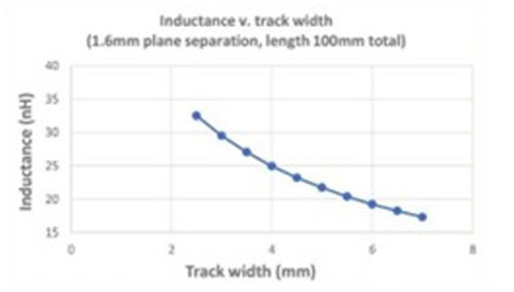

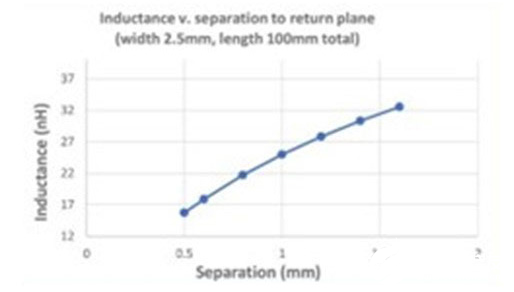

?這個(gè)關(guān)系適用于隔離的出發(fā)和返回跡線,不適用于返回平面上方的單條跡線。有趣的是,從圖中可以看出,電感與跡線寬度和厚度的關(guān)系相對(duì)較小,長(zhǎng)度是主要因素。(圖3)

?這個(gè)關(guān)系適用于隔離的出發(fā)和返回跡線,不適用于返回平面上方的單條跡線。有趣的是,從圖中可以看出,電感與跡線寬度和厚度的關(guān)系相對(duì)較小,長(zhǎng)度是主要因素。(圖3)

圖3 :根據(jù)等式1,隔離的跡線電感隨厚度和寬度的變化

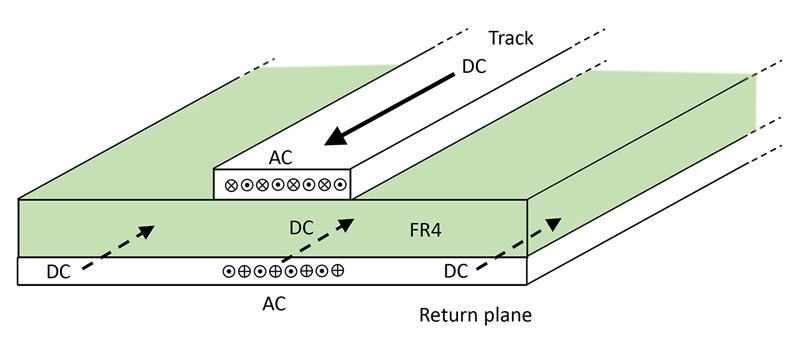

圖表顯示,通過(guò)將高頻率去耦電容(圖2中的Cd)放置在比大直流鏈路電容更靠近開(kāi)關(guān)的位置,可有效縮短長(zhǎng)度并獲得最大優(yōu)勢(shì),電容不是低電感類型時(shí)候效果更為明顯。如果出發(fā)和返回路徑十分接近,通常使用銅平面, 則電感大幅減少(圖4)。

圖3 :根據(jù)等式1,隔離的跡線電感隨厚度和寬度的變化

圖表顯示,通過(guò)將高頻率去耦電容(圖2中的Cd)放置在比大直流鏈路電容更靠近開(kāi)關(guān)的位置,可有效縮短長(zhǎng)度并獲得最大優(yōu)勢(shì),電容不是低電感類型時(shí)候效果更為明顯。如果出發(fā)和返回路徑十分接近,通常使用銅平面, 則電感大幅減少(圖4)。 圖4 :返回平面在跡線下方可顯著減少總電感

根據(jù)Clayton的等式2,現(xiàn)在,與返回平面相距1.6mm(H)的2.5mm(W) 跡線的總回路電感僅為32nH。該等式對(duì)W/H>1有效,同樣,跡線厚度不是主要因素,但現(xiàn)在,跡線寬度以及跡線與平面之間的距離可產(chǎn)生顯著影響(圖5)。如果返回平面同時(shí)位于跡線上方和下方,則電感進(jìn)一步減少,并獲得增強(qiáng)屏蔽的額外優(yōu)勢(shì)。

圖4 :返回平面在跡線下方可顯著減少總電感

根據(jù)Clayton的等式2,現(xiàn)在,與返回平面相距1.6mm(H)的2.5mm(W) 跡線的總回路電感僅為32nH。該等式對(duì)W/H>1有效,同樣,跡線厚度不是主要因素,但現(xiàn)在,跡線寬度以及跡線與平面之間的距離可產(chǎn)生顯著影響(圖5)。如果返回平面同時(shí)位于跡線上方和下方,則電感進(jìn)一步減少,并獲得增強(qiáng)屏蔽的額外優(yōu)勢(shì)。

柵極和源連接中的公共連接電感是一大問(wèn)題

如果 SiC FET 柵極驅(qū)動(dòng)回路及其源極電流共用任一長(zhǎng)度的跡線,則公共連接的電感會(huì)產(chǎn)生瞬態(tài)電壓,其中負(fù)載電流階躍作用于柵極驅(qū)動(dòng)(圖6)。最糟糕的情況是,關(guān)斷驅(qū)動(dòng)信號(hào)的幅度減小,這可能會(huì)導(dǎo)致 “幻象導(dǎo)通”,在橋式轉(zhuǎn)換器支路中產(chǎn)生 “擊穿”,帶來(lái)災(zāi)難性損壞。即使分離的柵極驅(qū)動(dòng)回路連接至三引腳TO-247器件的源極,仍有大約10nH的封裝電感,這是常見(jiàn)現(xiàn)象,無(wú)法消除,如果源極電流邊緣速率為1000A/μs,會(huì)產(chǎn)生10伏的瞬態(tài)電壓。在實(shí)際設(shè)計(jì)中,這些邊緣速率通常較為緩慢,解決方案之一是使用四引腳器件,并與源極建立單獨(dú)的內(nèi)部 “開(kāi)爾文” 連接,比如UnitedSiC (Qorvo)提供的器件。這能夠?qū)⒐策B接電感降至大約1nH的裸片數(shù)據(jù),從而實(shí)現(xiàn)更高的邊緣速率以及可能更低的動(dòng)態(tài)損耗。

圖6 :高源極 di/dt 和公共連接電感會(huì)產(chǎn)生瞬態(tài)柵極電壓

圖6 :高源極 di/dt 和公共連接電感會(huì)產(chǎn)生瞬態(tài)柵極電壓電路電容可導(dǎo)致不必要的耦合

請(qǐng)注意,較寬的跡線可有效降低電感和瞬態(tài)電壓,但也會(huì)提高對(duì)相鄰跡線、組件和地面的電容。SiC FET所具備的高dV/dt 速率能夠引起位移電流,這會(huì)導(dǎo)致高EMI水平和混亂操作。例如,邊緣速率為100kV/μs 時(shí),SiC FET可輕松開(kāi)關(guān),僅通過(guò)10pF就能產(chǎn)生1A。電流以通常難以識(shí)別的路線圍繞系統(tǒng)流動(dòng)。在高側(cè)開(kāi)關(guān)的源連接處,對(duì)主開(kāi)關(guān)節(jié)點(diǎn)的電容是一個(gè)特殊問(wèn)題。主開(kāi)關(guān)節(jié)點(diǎn)可通過(guò)物理方式隔離,以避免耦合至任何敏感的控制或反饋連接。然而,始終有路徑通過(guò)柵極驅(qū)動(dòng)器連接至系統(tǒng)其余部分,即使利用磁力或通過(guò)光耦合器將其隔離,信號(hào)路徑和提供柵極驅(qū)動(dòng)電源的DC-DC轉(zhuǎn)換器中也將存在殘余電容。為此,在指定具有低耦合電容的隔離部件時(shí),應(yīng)格外小心,最好不超過(guò)數(shù)pF。 開(kāi)關(guān)節(jié)點(diǎn)和機(jī)箱接地之間的電容是共模EMI的主要來(lái)源,可能會(huì)導(dǎo)致超出法定限制。好在SiC FET等器件的效率往往意味著它們能夠使用小型未接地散熱器操作。如果必須使用較大的接地散熱器,開(kāi)關(guān)器件和散熱器之間可使用銅箔形式的靜電屏蔽,但這勢(shì)必會(huì)提高熱阻,因此必須小心地對(duì)其進(jìn)行絕緣處理,以滿足安全標(biāo)準(zhǔn)。

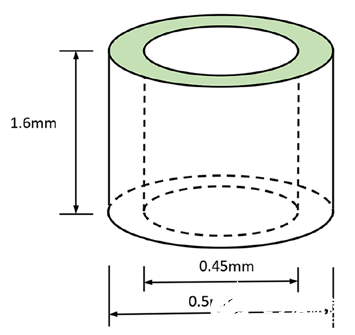

散熱考慮因素 SiC FET的損耗通常非常低,因此PCB跡線和平面可作為散熱器,將結(jié)溫保持在合理的范圍內(nèi)。由于與其他發(fā)熱組件的相互作用,此類布局的熱阻可能很難量化,因此通常使用多物理模擬軟件來(lái)預(yù)測(cè)結(jié)果。PCB材料、層數(shù)及其銅重量、氣流方向和速率、表面輻射系數(shù)和其他組件產(chǎn)生的交叉加熱都必須考慮在內(nèi)。 熱量可使用散熱孔通過(guò)PCB傳遞,憑借僅大約0.25W/m-K的核心熱導(dǎo)率,對(duì)FR4進(jìn)行改進(jìn)。直徑為0.5mm、長(zhǎng)1.6mm且壁厚為0.025mm的未填補(bǔ)散熱孔的熱阻約為100°C/W(圖7)。

PCB跡線電阻導(dǎo)致效率降低

現(xiàn)在,即使在高額定電壓下,SiC FET的導(dǎo)通電阻只有數(shù)毫歐,因此其傳導(dǎo)損耗可能非常低。然而,相關(guān)跡線電阻可能相當(dāng)大,因此應(yīng)盡可能減少跡線電阻,以維持SiC FET優(yōu)勢(shì)。為了評(píng)估影響,PCB電阻取決于銅電阻率、厚度、溫度和跡線長(zhǎng)度。一種便捷的測(cè)量方式是沿著跡線計(jì)算 “平方” 的數(shù)量,例如,在25°C時(shí),無(wú)論尺寸如何,35μm/1oz銅在每 “平方” 的電阻為0.5毫歐,所以1mm寬、 1mm長(zhǎng)的跡線和10密耳寬、10密耳長(zhǎng)的跡線一樣,電阻均為0.5毫歐。因此,正如我們?cè)谟?jì)算電感時(shí)使用的,對(duì)于長(zhǎng)度只有 100mm的2.5mm跡線,測(cè)量得出其電阻為20毫歐——通常比最低的SiC FET導(dǎo)通電阻還要多。此外,隨著溫度升高,銅電阻增加,在本例中,100°C時(shí),銅電阻增加至大約26毫歐,因此應(yīng)將這一因素考慮在內(nèi)。對(duì)于直跡線,“計(jì)算平方數(shù)” 的方法十分準(zhǔn)確,如有突然轉(zhuǎn)彎,由于電流集聚效應(yīng),拐角處的電阻率會(huì)提高。無(wú)論如何,應(yīng)避免直角,以防止出現(xiàn)局部高電場(chǎng)強(qiáng)度,避免電壓擊穿風(fēng)險(xiǎn)增加。 對(duì)于交流電,應(yīng)考慮 “趨膚效應(yīng)”,即隨著頻率增加,電流往往集中到表面流動(dòng),而不是在大部分導(dǎo)線內(nèi)流動(dòng)。但對(duì)于PCB跡線,該效應(yīng)通常較小,趨膚深度約為66/f1/2mm,因此,即使在1MHz時(shí),開(kāi)關(guān)電流流向深度為0.07mm或總厚度為2oz的銅。諧波電流不會(huì)滲透得這么深,但其幅度更小。 當(dāng)高頻率交流電通過(guò)銅平面返回時(shí),可以假設(shè)該路徑上的電阻更低。然而,由于電流集中到功率跡線下方且只有直流組件顯著分散,優(yōu)勢(shì)并不明顯(圖8)。

結(jié)論

應(yīng)了解并降低實(shí)際連接電阻,以便充分發(fā)揮SiC FET的潛在性能。在一些轉(zhuǎn)換拓?fù)浣Y(jié)構(gòu)中,寄生電感和電容可能是諧振槽的一部分,因此通常也應(yīng)該降低。在這種情況下,量化和控制電路值仍非常重要。

原文標(biāo)題:給SiC FET設(shè)計(jì)PCB有哪些注意事項(xiàng)?

文章出處:【微信公眾號(hào):Qorvo半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

Qorvo

+關(guān)注

關(guān)注

17文章

633瀏覽量

77392

原文標(biāo)題:給SiC FET設(shè)計(jì)PCB有哪些注意事項(xiàng)?

文章出處:【微信號(hào):Qorvo_Inc,微信公眾號(hào):Qorvo半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SiC外延生長(zhǎng)技術(shù)的生產(chǎn)過(guò)程及注意事項(xiàng)

LMK5B12204時(shí)間抖動(dòng)可以做到多少?有哪些注意事項(xiàng)?

SiC的離子注入工藝及其注意事項(xiàng)

繞線電感定制的注意事項(xiàng)

CC13xx/CC26xx硬件配置和PCB設(shè)計(jì)注意事項(xiàng)

Buck電路中PCB layout布局設(shè)計(jì)和注意事項(xiàng)

PCB設(shè)計(jì)的EMC有哪些注意事項(xiàng)

FMD LINK 使用注意事項(xiàng)

SMT貼片打樣的注意事項(xiàng)有哪些?

高頻高密度PCB布局設(shè)計(jì)注意事項(xiàng)

霍爾元件使用的注意事項(xiàng)

電流互感器的使用注意事項(xiàng)

數(shù)據(jù)采集設(shè)備測(cè)試有哪些注意事項(xiàng)

聯(lián)軸器使用有哪些注意事項(xiàng)?

給SiC FET設(shè)計(jì)PCB有哪些注意事項(xiàng)?

給SiC FET設(shè)計(jì)PCB有哪些注意事項(xiàng)?

評(píng)論