如今,FPGA 功能強大且管腳數目極大,可為工程師提供大量機會來提升特性和功能,同時還能降低產品成本。隨著復雜度增加,將這些器件集成到印刷電路板也成為了一項嚴峻的挑戰。數百個邏輯信號需映射到器件的物理管腳輸出,同時還需保持設計的電氣完整性。FPGA 復雜度增加也需要合成技術,如此才能更快達到時序收斂,地減少設計變更的影響以及解決特定應用要求。

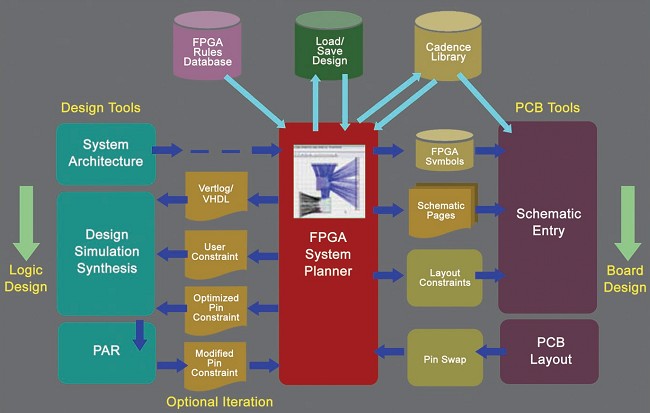

通過使用可選的 FPGA-PCB 優化技術,即將 HDL 合成和先進的 FPGA-PCB I/O 優化添加到 PADS Professional 中,便可應對這些挑戰。HDL 設計環境和 PCB 上物理實施之間的這一接口大大縮短了產品的上市時間,降低了制造成本。

直觀的邏輯合成環境包括先進的優化技術、屢獲殊榮的時序分析和先進的推論技術,適用于與供應商無關的設計中,可加快產品上市時間、消除設計缺陷以及提供的結果質量 (QoR)。

FPGA I/O 可優化管腳分配,從而提高布通率和信號完整性。

主要優勢:

通過采用并行流程縮短總設計時間

通過消除 PCB 信號層降低 PCB制造成本

消除由于 PCB 上的過期 FPGA符號所導致的 PCB 重新設計

采用高速性能優化

消除與創建和維護用于 PCB 原理圖的 FPGA 符號相關的成本

FPGA I/O Opmizaon

流程集成

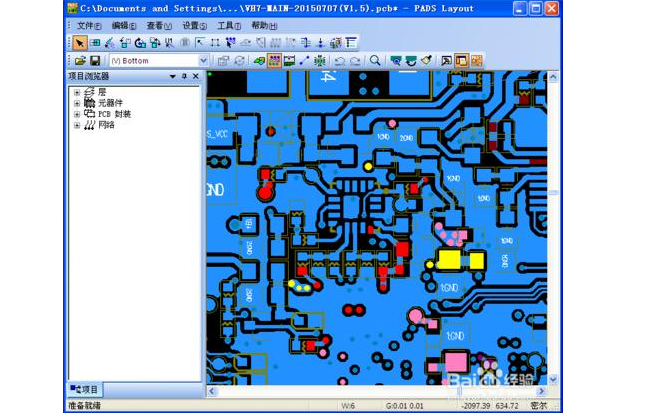

I/O 優化與 PADS Professional 設計流程緊密集成,在項目的任何階段均可訪問。原理圖、PCB Layout 和FPGA 數據庫始終保持同步,以便用戶控制項目的設計數據流。另外,原理圖用戶可決定何時將 FPGA 數據(新數據或更新數據)傳輸到 PCB 設計。

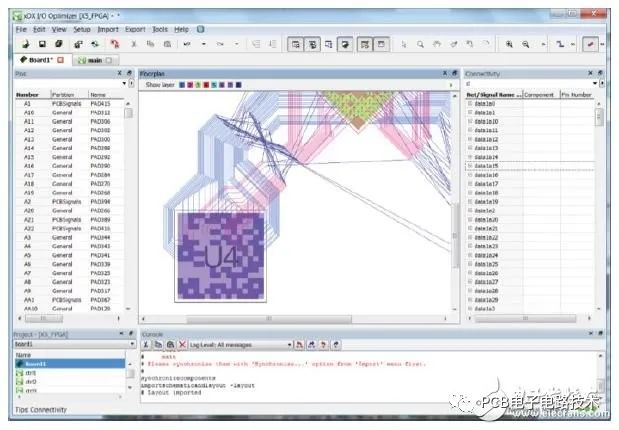

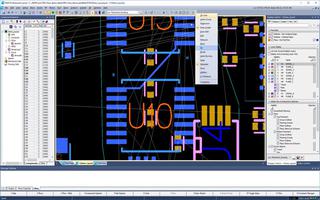

在 PCB 布局或布線開始前,I/O 優化可使用 PADS 項目數據進行疊層規劃以及優化初始分配。用戶可將結果導出到 Layout,并在項目級別或企業庫級別管理 FPGA 元件。

信號和管腳分配

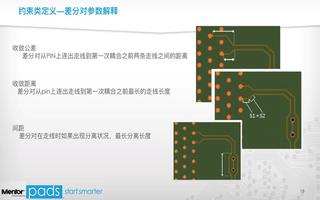

要手動將數百個 HDL 信號分配到 FPGA 管腳,同時仍嚴格遵守 FPGA 供應商規則,這一過程難度可能很大。為簡化這一流程,PADS Professional 提供簡單易用的功能,以便進行自動分配、信號標準監督、簡單拖放分配、支持操作對象集以及動態篩選。總之,其可簡化信號管腳分配操作流程。每次管腳分配更改均通過 FPGA-PCB 流程管理,無論更改了哪些地方,均可保持一致。

自動化元件和符號生成

由于 FPGA 器件自身的性質,因此需要不同的符號生成流程方法。在項目生命周期內,FPGA 邏輯通常要更改數次,而符號必須與這些更改保持一致。該 PADS 模塊功能強大,不僅可讓您輕松、快捷且無誤地創建符號,而且仍可完全控制符號創建流程。相比于手動符號創建,時間從數小時或數天降到了數分鐘。

疊層規劃

PCB 設計流程的一個重要階段是元器件布局及其在PCB 布局上的方向。您可在 PCB Layout 流程開始前或流程中進行疊層規劃。如此一來,工程師和設計人員就具有明顯優勢,可在項目的初階段進行FPGA 管腳分配更改、優化元器件布局和方向、縮短飛線以及減少飛線交互。

FPGA 多實例和優化

大多數情況下,同一個 FPGA 器件在不同項目甚至一個項目中都具有不同的邏輯功能。在項目開發期間,PADS Professional I/O 優化可自動支持這些情況。物料清單中列出了不同功能符號表示的FPGA 以及供應商元件編號。基本上無法成功手動執行兩個或多個 FPGA 器件之間的連接優化。不過使用這個 PADS Professional 模塊,優化算法即可評估所有可能的連接組合,從而獲得互連。此外,還可以地減少初始分配中產生的網絡交互,提高布線完成率。

FPGA Synthesis

優化算法

一套獨特的優化算法可自動將特定優化集中在有可能妨礙整體性能的設計領域,例如有限狀態機(FSM)、跨層次結構路徑以及具有過高組合邏輯的路徑。這些算法可提供自動化的啟發式方法,從而交付更小更快的設計,而無需迭代人工介入。

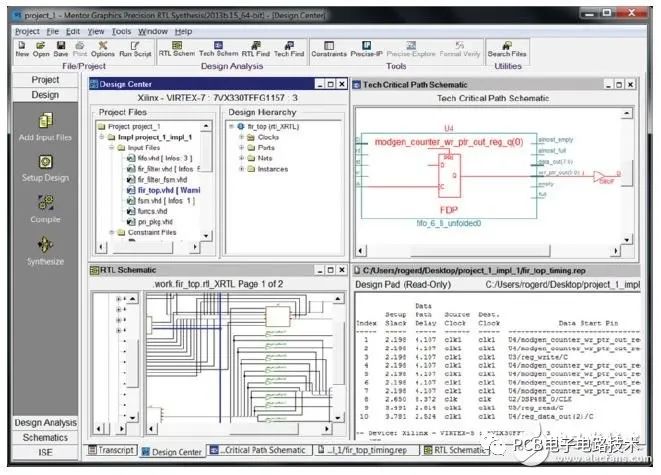

RTL 和技術原理圖查看器

編譯設計時,可使用通用門進行創建并以 RTL 原理圖形式查看。合成后,使用反映該數據庫的技術原理圖創建技術映射數據庫。原理圖查看器可協助您了解如何解讀 RTL 并將其映射到目標 FPGA 技術中。

供應商不相關性

與供應商無關的合成可支持 Altera、Latce、Microsemi和 Xilinx 的器件。因此,您可使用相同的 HDL 設計源文件和約束將任意器件作為目標對象并獲取合成網表,將其通過適當的供應商工具用于布局布線。此供應商不相關性使用戶可以輕松將任意 FPGA 器件重新作為目標對象并分析結果,從而找到適合您設計的 FPGA 器件。

在與供應商無關的環境中使用合成技術,針對每種 FPGA 器件實現特定的架構優化。

支持所有器件

除支持四大 FPGA 供應商的 FPGA 器件外,PADS FPGA-PCB 協同設計模塊還全面支持 Altera Quartus II、Latce Diamond 和 ispLEVER、Microsemi Libero 和Designer 以及 Xilinx ISE 和 Vivado 等 FPGA 供應商工具。

簡化約束流程

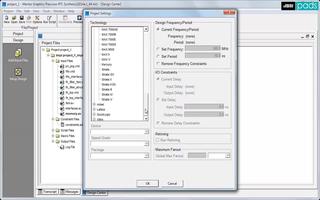

為適應當今高度復雜的 FPGA 設計流程,需要支持各種約束源,包括 HDL 代碼、SDC 文件和工具中的全局約束集等特定約束源。請務必指定時鐘頻率、輸入/輸出延遲和時序異常(如:合成中的多循環和偽路徑)等共同時序約束,以此確保從合成中獲取結果。

門控時鐘轉換

ASIC 設計人員通常使用門控時鐘進行功率管理和其他操作。但映射到 FPGA 時,這些門控時鐘會導致較大的時鐘偏移、創建假信號以及阻礙時序分析。門控時鐘使用FPGA 中適當的啟用信號自動進行轉換。

當今的 FPGA 器件除常規邏輯模塊外還包含 DSP 和 RAM嵌入式模塊。這樣一來,合成工具可了解各種 RTL 編碼樣式,將其映射到適當的 DSP或 RAM 模塊,從而充分利用資源并獲得性能。PADS Professional FPGA-PCB 協同設計模塊具有先進的推論和優化功能,可以限度地利用嵌入式資源,從而提高面積利用率和頻率。

Verilog、SystemVerilog 和 VHDL 支持

通過使用 Verilog、SystemVerilog 和 VHDL/VHDL-2008等業內語言支持,設計人員可采用這些格式的任意組合創建和合成 RTL 設計,從而獲得結果。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602043 -

pcb

+關注

關注

4318文章

23022瀏覽量

396430 -

HDL

+關注

關注

8文章

327瀏覽量

47344 -

協同設計

+關注

關注

0文章

14瀏覽量

7891

原文標題:FPGA-PCB協同設計模塊

文章出處:【微信號:PCB電子電路技術,微信公眾號:PCB電子電路技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Cadence FSP:FPGA-PCB系統化協同設計工具介紹

FPGA-PCB優化技術降低制造成本

PADS Professional如何創建軟硬結合板

PADS Professional的多線高速設計繞線模塊

protel sch(PCB) to pads(powerp

FPGA-PCB協同設計模塊

FPGA-PCB協同設計模塊

PADS Professional原理圖輸入工具的功能介紹

PADS Professional設計工具的主要功能介紹

PADS Professional的特點及應用介紹

PADS Professional的FPGA-PCB協同設計模塊

PADS Professional的FPGA-PCB協同設計模塊

評論