- TTL電路基本原理

要實(shí)現(xiàn)輸出電平在0/1之間變換,需要三極管的數(shù)量最少只需要一個(gè),而TTL電路使用了4個(gè)三極管,用較多的器件去實(shí)現(xiàn)相同的功能,必定要有性能上的提升,否則這種電路設(shè)計(jì)就是一種浪費(fèi)。對(duì)于TTL電路而言,使用成倍的器件需要換來的性能包括以下幾點(diǎn):

a. 提高開關(guān)速率

b. 提高帶載能力

c. 提高抗干擾性

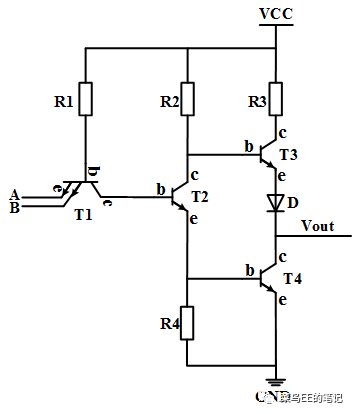

圖1

TTL電路如圖1所示,當(dāng)輸入A/B有一個(gè)為低電平時(shí)(假設(shè)為0V),T1管的基極被鉗位到0.7V,不足以使得T2、T4管導(dǎo)通,所以T2的集電極電位為高,T3導(dǎo)通,Vout輸出為高。當(dāng)A/B輸入都是高電平時(shí)(假設(shè)為3.6V),則T1的基極電壓為4.3V,該電壓可以使T2、T4飽和導(dǎo)通,從而T1的基極電位被鉗位在2.1V(三個(gè)PN結(jié)的壓降),T4導(dǎo)通后,T4的基極電位為0.7V,T2此時(shí)為飽和導(dǎo)通,導(dǎo)致T3的基極電位大概為1V左右,這個(gè)電壓不足以使得T3和二極管D同時(shí)導(dǎo)通,故Vout輸出為低電平。

在TTL電路中,使用推挽輸出目的是為了增強(qiáng)帶載能力;二極管D可以砸T4導(dǎo)通時(shí),防止T3導(dǎo)通導(dǎo)致T3、T4直通;T2的設(shè)置主要是為了給T3、T4提供驅(qū)動(dòng)。在Vout由低變高時(shí),T2的基極電荷在T1的作用下被迅速抽走,關(guān)斷比較快,T2關(guān)斷,T3即打通。但是T4的基極電荷只能通過R4放電,導(dǎo)致T4關(guān)斷得比較慢,如此以來,就有一小段T3、T4直通的時(shí)間,因此需要增加電阻R3限制短路電流。

- 為什么T2、T4為飽和導(dǎo)通

首先看T4,T4導(dǎo)通時(shí),其基極電壓為0.7V,輸出端與后級(jí)電路匹配時(shí),Vout通過下一級(jí)的R1、T1的發(fā)射結(jié)上拉到VCC,這個(gè)集電極電阻足以使其飽和導(dǎo)通(不行就設(shè)置好R1的阻值)。T2是必須要飽和導(dǎo)通的,因?yàn)門2工作在放大區(qū)會(huì)使Vout的輸出具有不確定性(影響T3的基極電位),T2的飽和導(dǎo)通是由其基極電流保證的。如前述,T2導(dǎo)通時(shí),T1的發(fā)射結(jié)反偏,集電結(jié)正偏,三極管T1工作在倒置態(tài)。此時(shí)T2基極電流與T1基極電流相當(dāng),設(shè)置R1即可保證使2飽和。

- 如何理解三極管T1的倒置工作狀態(tài)

隨便翻開一本教材或者TTL的資料,都會(huì)寫三極管T1在輸入為高電平的時(shí)候,處于倒置放大的工作狀態(tài),這種感覺好像是電路設(shè)計(jì)者精心這么設(shè)計(jì)的,故意使用三極管的倒置放大來實(shí)現(xiàn)什么目的,但對(duì)為什么這么用又沒有下文。實(shí)際上,這只是對(duì)三極管工作狀態(tài)的一種客觀描述。我建議教材不要單獨(dú)把這個(gè)狀態(tài)單獨(dú)強(qiáng)調(diào)一下,沒有什么用還容易誤導(dǎo)人,除非把龔總原理給講清楚。得出以上結(jié)論的理由如下:

首先,三極管各個(gè)級(jí)之間是有寄生電容的,當(dāng)三極管由導(dǎo)通變?yōu)榻刂箷r(shí),先要把基極的電荷給放掉,這個(gè)放電過程需要時(shí)間,直接影響三極管的開關(guān)速度,這是前提。

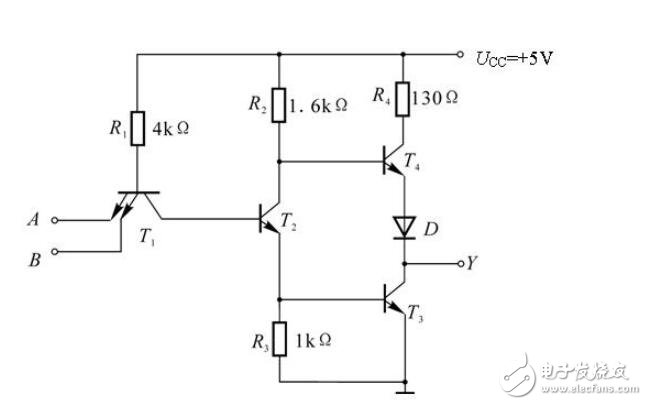

采用TTL電路的解法時(shí),當(dāng)輸入為高電平時(shí),T1倒置放大,T2的飽和由R1保證;當(dāng)輸入由高變低時(shí),T1的基極被鉗位到0.7V,由于T2、T4關(guān)斷需要時(shí)間,T1的集電極電位仍保持在1.4V,因此,T1處于放大狀態(tài),可以迅速地抽取T2基極的電荷,使T2迅速關(guān)斷。如果換一種接法,讓T1的集電極作為輸入,如圖2所示:

圖2

當(dāng)T1的輸入為高時(shí),T1的基極電位為2.1V,集電結(jié)反偏,發(fā)射結(jié)正偏,該電流可以使得T2飽和導(dǎo)通。當(dāng)T1的輸入由高變低時(shí),T1的基極電位為0.7V,發(fā)射極電位為1.4V,T1處于倒置放大狀態(tài),此時(shí)T2的基極電流顯然要小于T1處于放大區(qū)的電流,因此T2需要更長(zhǎng)的時(shí)間關(guān)斷,影響了其開關(guān)速度。

通過以上說明可以發(fā)現(xiàn),T1是否工作在倒置放大無需額外說明,哪種接法能提供更快的開關(guān)速度才是關(guān)鍵。

- 電平門限計(jì)算

TTL電平門限也是沒有標(biāo)準(zhǔn)的,因廠家而異,但也需要滿足一定的范圍,以圖1電路為例,計(jì)算如下。

輸出高電平:

如果輸入電平由高逐漸降低時(shí),降到0.7V,T4會(huì)先關(guān)閉,T2仍然導(dǎo)通,此時(shí)假設(shè)R4的電壓為臨界值0.7V,則,T3的基極電壓為:

因此,有:

輸出低電平視飽和程度,取最大不超過0.4V。

輸入低電平:

輸入為低時(shí),輸出應(yīng)為高,前面已經(jīng)分析,要使輸出為高,臨界條件為T4剛關(guān)閉時(shí),此時(shí)輸入不應(yīng)超過1.4V。假如以不以T2導(dǎo)通為標(biāo)準(zhǔn),則輸入低電平最大不應(yīng)超過0.7V。

輸入高電平:

按前述分析,輸入高電平最低不應(yīng)低于1.4V。

-

三極管

+關(guān)注

關(guān)注

142文章

3600瀏覽量

121661 -

二極管

+關(guān)注

關(guān)注

147文章

9575瀏覽量

165923 -

TTL電路

+關(guān)注

關(guān)注

2文章

65瀏覽量

15064 -

TTL電平

+關(guān)注

關(guān)注

1文章

99瀏覽量

11984

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ESP8266學(xué)習(xí)筆記相關(guān)資料下載

TTL電平 CMOS電平推挽輸出

TTL與CMOS電平轉(zhuǎn)換區(qū)別

ECL電平、LVDS電平、TTL電平_簡(jiǎn)單的比較

詳解TTL和CMOS電平

TTL電平與CMOS電平的區(qū)別,TTL & CMOS

ttl電平是什么意思

ttl電平與cmos電平的區(qū)別

什么是TTL電平、CMOS電平?區(qū)別?

TTL電平學(xué)習(xí)筆記

TTL電平學(xué)習(xí)筆記

評(píng)論