LVPECL電平是常用的一種邏輯電平,大部分資料對(duì)該電平的描述為:由ECL電平發(fā)展而來(lái),但是對(duì)其邏輯電平門限的確定、為什么要加一個(gè)偏置電平以及LVPECL電平與ECL電平在電路結(jié)構(gòu)上的差異鮮有論述。因此,對(duì)在學(xué)習(xí)該電平中遇到的困惑整理如下:

1.ECL電路的基本原理

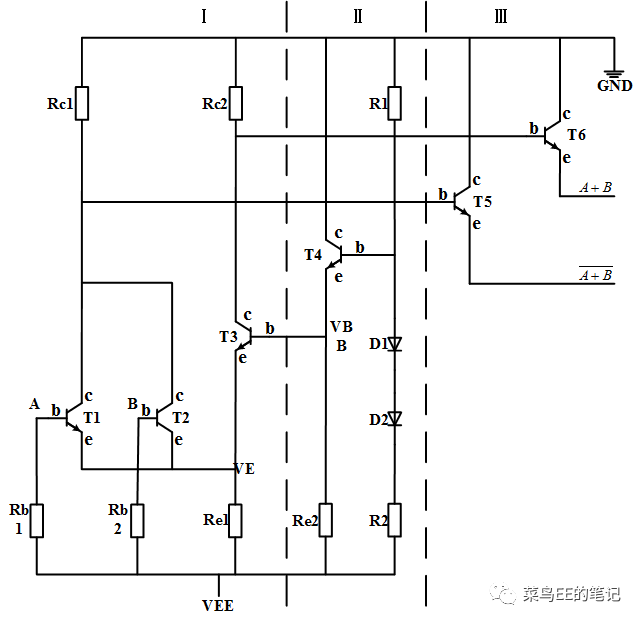

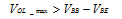

圖1 ECL電路

ECL電路如圖1所示,其分為輸入級(jí)、中間級(jí)和輸出級(jí)三部分。輸入級(jí)由T1、T2、T3三管構(gòu)成,當(dāng)A、B有一個(gè)為1時(shí),T1和T2至少有一個(gè)管開(kāi)通,VE電位將被抬高,導(dǎo)致T3截止;當(dāng)A、B都為0時(shí),T3則會(huì)開(kāi)通。輸出級(jí)由T5、T6組成的射隨器構(gòu)成,當(dāng)T1、T2至少有一個(gè)開(kāi)通時(shí),T5的截止,輸出為0,而此時(shí)T6導(dǎo)通輸出為1。即T5輸出 ~(A+B),而T6輸出A+B。中間級(jí)的作用為給T3提供合適的偏置電壓VBB,Re2有抑制溫漂的作用。

2.ECL電路為什么不直接輸出,需要經(jīng)過(guò)射隨器輸出?

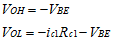

考慮直接輸出的情況,輸出高電平為:

輸出低電平為:

當(dāng)ECL電平直接耦合時(shí),設(shè)VOH直接接到T1管,則T1管的基極電位為0(邏輯1),集電極電位電位小于0(因?yàn)橛蠷c1的壓降),集電結(jié)正偏,T1管將進(jìn)入飽和區(qū)。ECL為獲得較高的開(kāi)關(guān)速度,設(shè)計(jì)時(shí)需要保證三極管不飽和,因此需要經(jīng)過(guò)射隨器輸出,降低其輸出高電平,同時(shí),經(jīng)過(guò)射隨器輸出,其輸出阻抗變小,驅(qū)動(dòng)能力也會(huì)變強(qiáng)。

3.邏輯電平門限的確定

ECL電平的邏輯電平門限是沒(méi)有標(biāo)準(zhǔn)來(lái)限定的,其門限的大小需要滿足各廠家提供數(shù)據(jù)手冊(cè)。但是,根據(jù)電路結(jié)構(gòu)分析,各電平門限以及擺幅大小也有一定的限制的條件,分析如下:

由電路結(jié)構(gòu)可知:

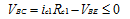

由于三極管不能進(jìn)入飽和區(qū),因此需要滿足:

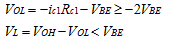

因此,擺幅滿足:

對(duì)邏輯高電平:

為保證T1、T2導(dǎo)通時(shí),T3截止,有:

對(duì)邏輯低電平,為保證T1、T2截止時(shí),T3導(dǎo)通,有:

由擺幅要求:

4.PECL與ECL電路的差異

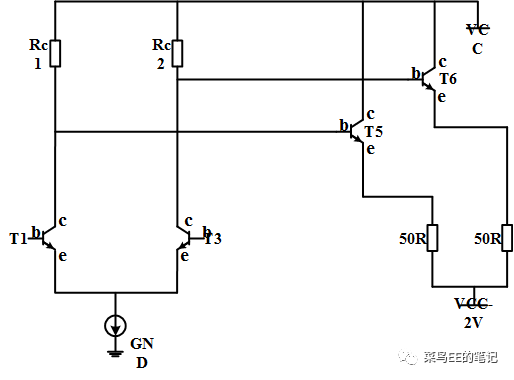

圖2 PECL電路

大多數(shù)資料對(duì)PECL電路的描述為:把ECL電路的高電平變成正電平,即得到PECL電路。但是,其給出的電路圖與ECL電路卻大相徑庭。中間級(jí)去哪了?為什么直接使用差分輸入?輸出為什么要接到到VCC-2V,一概沒(méi)有交代,看得人一頭霧水,現(xiàn)整理如下。

首先PECL為差分輸入,ECL雖然也有兩個(gè)輸入,但其輸入其實(shí)相當(dāng)于取或,和單端輸入單端效果是一樣的。在有關(guān)資料里,描述為“原理與單端輸入,雙端輸出的差分放大電路類似”。因此輸入端的差異我個(gè)人判斷是ECL/PECL的應(yīng)用場(chǎng)景不同導(dǎo)致的,ECL用于單端轉(zhuǎn)差分或者需要同時(shí)獲得其輸出的反信號(hào)的場(chǎng)合,PECL則為差分輸入、差分輸出的場(chǎng)景(未做具體考證)。由于輸入級(jí)的差異,PECL自然不需要中間級(jí)提供偏置電壓了。

5.為什么PECL的輸出需要通過(guò)50R電阻接到VCC-2V?

PECL的輸出高電平為VOH=2.4V,輸出低電平VOL=1.6V,為達(dá)到這個(gè)電平門限要求,需要給輸出電平提供一個(gè)2V(VCC-1.3)作用的共模電壓(輸出高低電平的中間,使得獲得的動(dòng)態(tài)電平范圍最大)。為滿足此要求,一般在輸入端會(huì)加一個(gè)VCC-1.3V的直流偏置,提供共模電壓,以圖2電路為例,當(dāng)T1端輸入為高,為使得T1不進(jìn)入飽和區(qū),則T1的集電極電壓最小為VCC-1.3V,如此,為了使輸出的三極管不進(jìn)入截止區(qū),則其偏置電壓不應(yīng)大于VCC-2V,同時(shí)為了避免功耗過(guò)大,終端的偏置電壓不應(yīng)取太小,故取VCC-2V。50R的電阻則是用于阻抗匹配,避免產(chǎn)生反射。

-

邏輯電平

+關(guān)注

關(guān)注

0文章

149瀏覽量

14356 -

LVPECL

+關(guān)注

關(guān)注

2文章

26瀏覽量

17861 -

PECL

+關(guān)注

關(guān)注

0文章

321瀏覽量

14275 -

射隨器

+關(guān)注

關(guān)注

0文章

8瀏覽量

8876 -

ECL電平

+關(guān)注

關(guān)注

0文章

3瀏覽量

1481

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

LVDS、CML、LVPECL不同邏輯電平之間的互連(二)

淺談LVDS、CML、LVPECL三種差分邏輯電平之間的互連

各種電平標(biāo)準(zhǔn)總結(jié)

常用電平標(biāo)準(zhǔn)及解析

請(qǐng)問(wèn)ecl差分接入的0.8v擺幅是否可以驅(qū)動(dòng)ad10242

ecl差分接入的0.8v擺幅是否可以驅(qū)動(dòng)ad10242,lvpecl電平是否可以滿足標(biāo)準(zhǔn)?

常用的電平標(biāo)準(zhǔn)

電平標(biāo)準(zhǔn)

ECL電平、LVDS電平、TTL電平_簡(jiǎn)單的比較

ECL PECL LVPECL信號(hào)都是什么?它們的優(yōu)缺點(diǎn)和電路圖詳細(xì)剖析

信號(hào)邏輯電平標(biāo)準(zhǔn)的詳細(xì)說(shuō)明

FPGA的常用電平標(biāo)準(zhǔn)

常見(jiàn)邏輯電平標(biāo)準(zhǔn)的詳細(xì)資料介紹

ADCMP551/ADCMP552/ADCMP553:?jiǎn)坞娫础⒏咚?b class='flag-5'>PECL/LVPECL比較器

詳解信號(hào)邏輯電平標(biāo)準(zhǔn):CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML資料下載

ECL/PECL/LVPECL電平學(xué)習(xí)筆記

ECL/PECL/LVPECL電平學(xué)習(xí)筆記

評(píng)論