1 介紹

此仿真實例用UltraEM來研究接地屏蔽層(PGS)以及NTN層的改變對器件Q值造成的影響。

PGS和NTN對器件起到的作用都是提高Q值。PGS是接地屏蔽層,其上結構與電感線圈垂直,通過減少金屬層與地板之間的耦合起到屏蔽作用;加NTN則會將工藝襯底的摻雜硅換成導電率更低的本征硅,減小了介質損耗角正切,從而降低了能量的損失,起到屏蔽的作用。

本次測試使用的三個實例分別是:

1. CMOS工藝的對稱螺旋電感;

2. 在1的基礎上添加一個接地屏蔽層;

3. 在1的基礎上更改襯底材料為本征硅。

將三個實例放入UltraEM仿真并對比其Q值變化。

2 仿真操作流程

2.1建立仿真算例

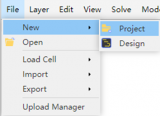

2.1.1 新建工程

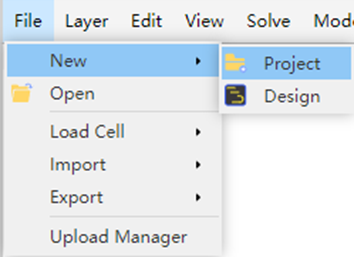

依次點擊File > New > Project新建工程,如下圖 2-1。

圖2-1新建工程 2.1.2 導入設計文件

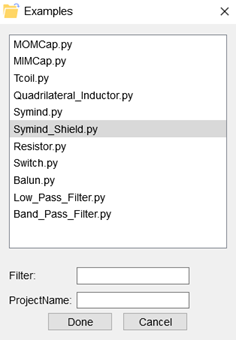

這里使用示例Examples中采用到接地屏蔽層的Symind_Shield.py工程。

圖2?2 導入設計文件

2.1.3 PGS測試算例

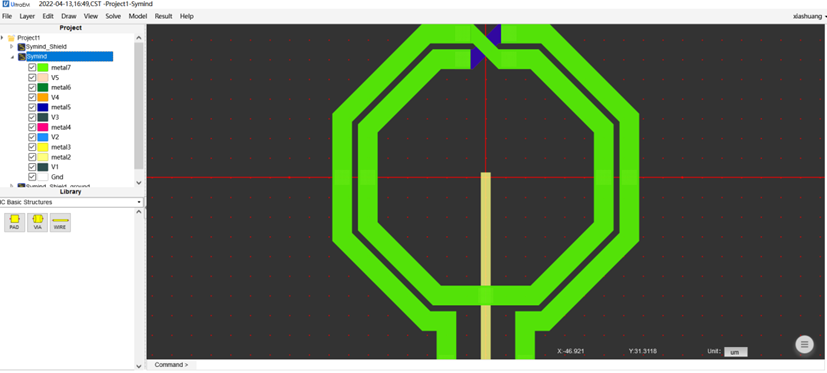

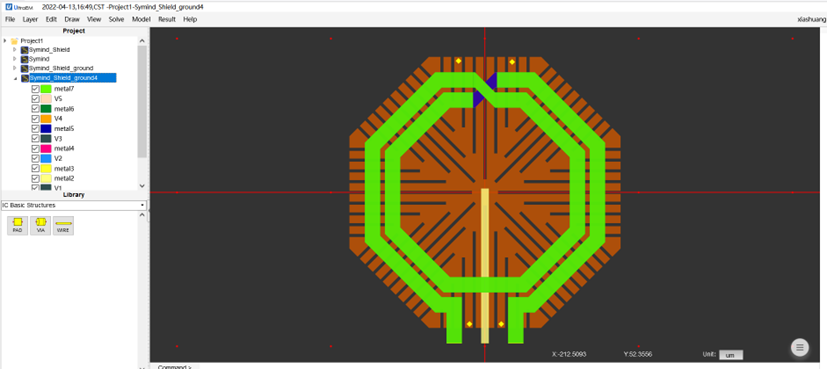

建立兩個螺旋電感算例,一個不含PGS,一個含PGS,如圖 2-3,圖 2-4。

圖2?3 無屏蔽層

圖2?4 接地屏蔽層 2.1.4 NTN層測試算例

圖2?4 接地屏蔽層 2.1.4 NTN層測試算例

建立兩個螺旋電感算例,一個使用摻雜硅襯底,一個使用本征硅襯底。

修改襯底材料參數可按如下方式操作:

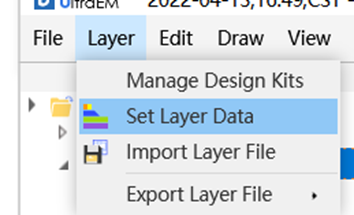

依次點擊Layer > Set Layer Data打開器件的層數據,如下圖2-5。

圖2?5 查看層數據

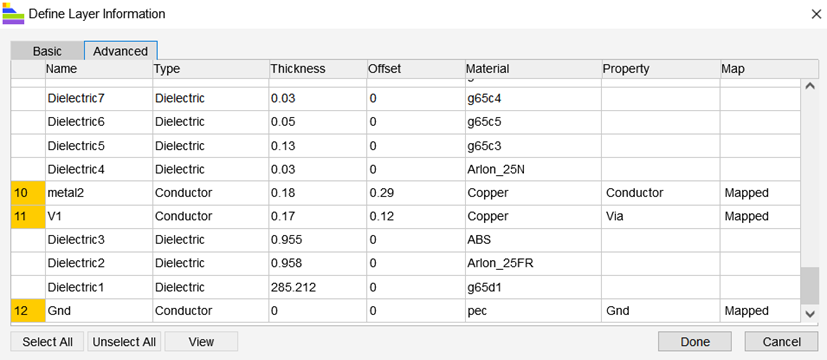

打開層數據之后,找到底部襯底層,如下圖2-6。

圖2?6 查看襯底

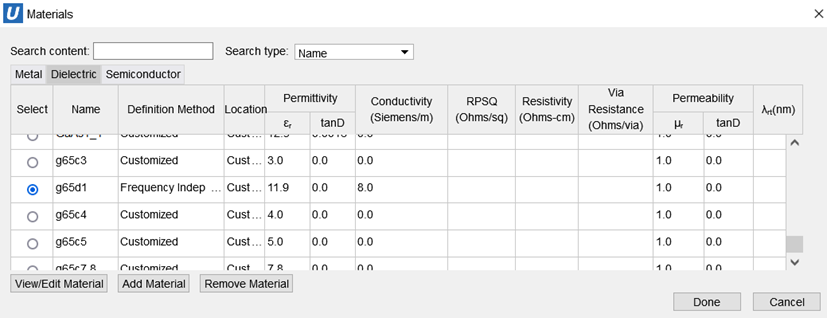

點擊Dielectric1層所用材料g65d1,即可查看該材料的信息,如下圖2-7。

圖2?7 襯底材料

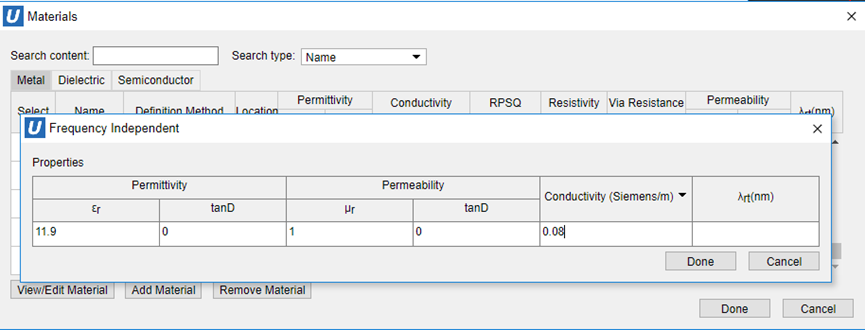

此處使用材料為摻雜硅,電導率為8.0 S/m。為對比NTN layer造成的影響,我們重新定義一個本征硅,電導率設置為0.08 S/m。點擊Add Material新建材料,如下圖2-8。  圖2-8 新建材料

圖2-8 新建材料

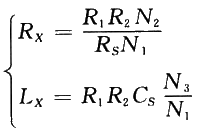

2.2 自定義參數

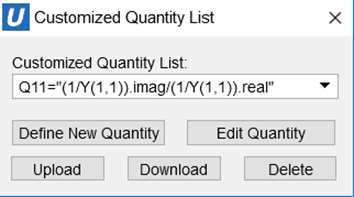

自定義參數Q值的查看需要預先定義公式,通過Result > Define Quantities建立一個新的公式,如下圖2-9。

圖2?9 定義Q參數

通過Define New Quantity,設置參數名及計算公式。

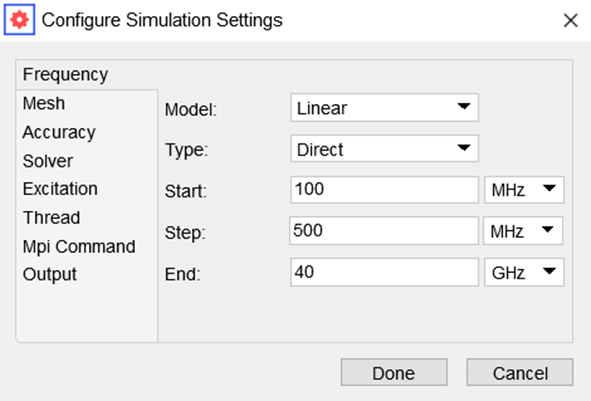

2.3 定義測試頻率

通過Solve > Settings進入頻率設置頁面,在Frequency中設置仿真的起始頻率、步長以及截止頻率。

圖2-10 設置仿真頻率

圖2-10 設置仿真頻率

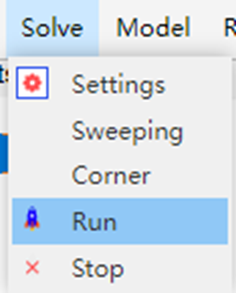

2.4 開始仿真

完成頻率設置后,點擊Solve > Run以運行仿真,如下圖2-11。

圖2-11 開始仿真

圖2-11 開始仿真

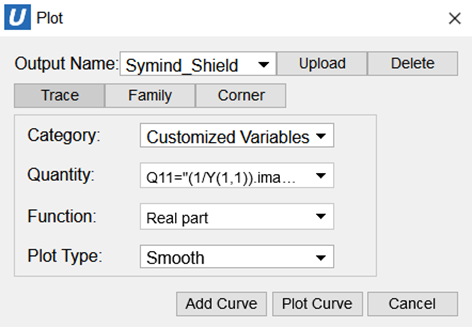

2.5 查看結果

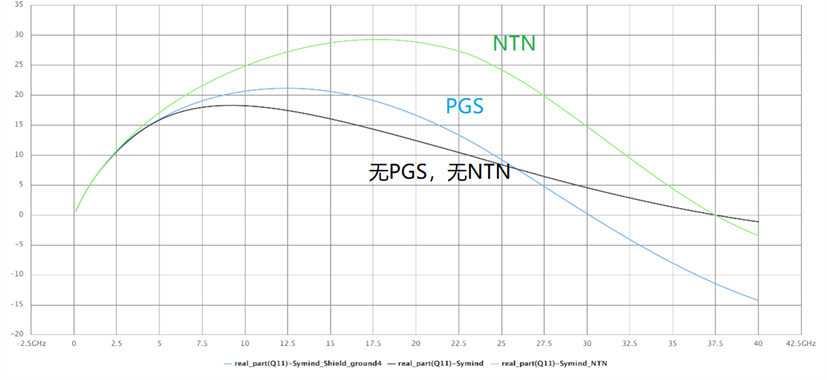

以上三個算例仿真完成后,單擊Result > Model Data,查看仿真結果。選擇Q11計算公式,查看其Real part。

圖2-12 繪圖

圖2-13 Q 值對比

Q值曲線由高到低依次是:添加NTN層的電感、添加PGS的電感、無NTN無PGS的電感。

從仿真結果來看,在頻率較低的頻段,三者幾乎重合,Q值區別很小,頻率較高時,三者差異逐步增加。

明顯可以發現有PGS的電感Q值要比沒有的高許多,使用本征硅的電感也明顯提高了Q。

此結果基本與理論相符,不論是接地屏蔽層還是減小襯底導電率,兩者都是減小了器件的損耗進而提高了Q值。

法動科技:

成立于2017年。作為擁有硅谷及斯坦福創新基因的國際一流團隊,我們專業提供射頻微波電子設計自動化(EDA)軟件,憑借自主研發的大容量、快速三維全波電磁仿真引擎和基于人工智能技術的高效系統級仿真引擎,能夠在射頻微波芯片、封裝、高速PCB等領域為用戶提供快速準確的電磁仿真、建模及優化設計方案。

同時,我們可以為包括移動通信、物聯網、5G、雷達、衛星通信系統和高速數字設計在內的產品提供高水平設計開發服務。

審核編輯:湯梓紅

-

pcb

+關注

關注

4318文章

23022瀏覽量

396424 -

接地

+關注

關注

7文章

757瀏覽量

45630 -

仿真

+關注

關注

50文章

4048瀏覽量

133431 -

雷達

+關注

關注

50文章

2904瀏覽量

117348

原文標題:UltraEM?中NTN Layer和PGS對Q影響的研究

文章出處:【微信號:FaradayDynamics,微信公眾號:法動科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何在ADS Momentum中使用PGS模擬電感器

電感q值的測量-傳感應用中

layer是什么?解析ad9中的plane與layer

UltraEM?的Corner Sweep仿真實例

UltraEM和EMCompiler對變壓器進行阻抗匹配的仿真實例

UltraEM中NTN Layer和PGS對Q值影響的研究

UltraEM中NTN Layer和PGS對Q值影響的研究

評論