15.1

多長需要端接

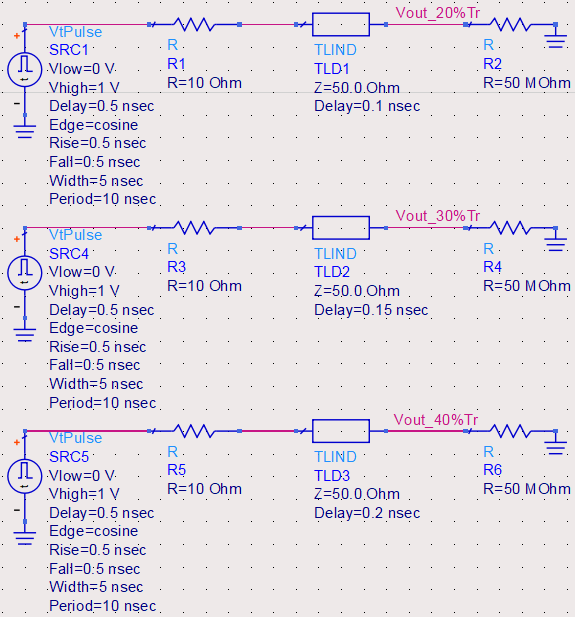

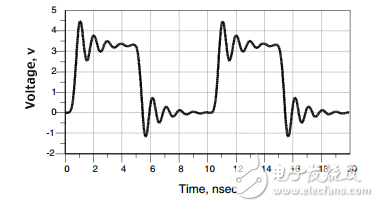

最簡單的傳輸線電路由近端驅動器、短的可控阻抗互連和遠端接收器組成。如前所述,信號將在遠端高阻抗開路端和近端低阻抗驅動器之間往返反彈。當導線很長時,多次反射會引起信號完整性問題,一般將其歸為振鈴類問題。如果導線足夠短,那么雖然依舊發生了反射,但它們卻被上升或下降沿掩蓋了,可能不會引起問題。下圖給出了傳輸線的時延分別為信號上升邊的20%、30%和40%時,接收端波形是如何變化的。

當互連時延大于0.1ns時,會發生多次反射,并且它們是以每0.2ns(即往返時間)完成一個往返振蕩的。如果時延遠小于上升邊,那么多次反射將被掩蓋在上升沿中,幾乎無法辨認,也就不會導致潛在的問題。根據上圖可以粗略地估計出,當時延小于上升邊的20%,反射幾乎是很小的,但如果超過20%振鈴就開始有明顯的影響。

經驗法則 :當傳輸線時延T_D大于信號上升邊的20%,就要開始考慮由于導線沒有終端端接而產生的振鈴噪聲。時延大于上升邊20%,振鈴噪聲會影響電路功能,必須加以控制,否則它將是造成信號完整性問題的隱患。如果T_D小于上升邊的20%就可以忽略振鈴噪聲,傳輸線無須終端端接。

如果上升邊是1ns,則無終端端接的傳輸線的最大時延約為 20%×1ns =0.2ns 。在FR4中,信號傳播速度約為6in/ns,所以無終端端接的傳輸線的最大長度約為 6in/ns×0.2ns=1.2in 。

經驗法則 :為了避免信號完整性問題,無終端端接的傳輸線的最大長度約為 Len_max 其中,len_max表示無終端端接的傳輸線的最大長度(單位為in),RT表示信號上升邊(單位為ns)。無須終端端接的傳輸線的最大長度(單位為in)是信號上升邊的納秒(ns)值。

若時鐘頻率是10MHz,則時鐘周期是100ns,上升邊約為10ns,那么無須終端端接的傳輸線的最大長度為10in。實際上這比常見主板上的所有互連都長。回憶時鐘頻率為10MHz的時代,雖然互連也相當于傳輸線,但反射噪聲一直沒有造成任何問題,因此說互連對于信號是“透明的”,那時不必擔心阻抗匹配、終端端接,以及各種傳輸線效應。

現在產品的形式沒有變,互連長度也沒有變,但信號上升邊卻變短了。今天的時鐘信號頻率已經足夠高,上升邊已經足夠短,所以電路板上的幾乎所有互連長度都不可避免地大于無須終端端接的傳輸線的最大長度,因此終端端接變得非常重要。

目前,信號上升邊下降至0.1ns,為了避免振鈴噪聲造成大的影響,無須終端端接的傳輸線的最大長度約為0.1in。幾乎所有互連長度都大于這個值,所以對于目前和今后的所有產品,必須采用端接策略。

15.2

點到點拓撲的通用端接策略

****振鈴是由源端和遠端的阻抗突變、兩端之間不斷往復的多次反射引起的,所以如果能至少在一端消除反射,就能減小振鈴噪聲。

控制傳輸線一端或兩端的阻抗以減小反射的方法稱為線的端接。典型的方法就是在重要部位放置一個或多個電阻器。

一個驅動器驅動一個接收器的情況稱為點到點的拓撲結構。下圖示例了端接點到點拓撲結構的4種方式。最常用的方法是將電阻器串聯在驅動器端,這稱為源端串聯端接。端接電阻與驅動器內阻之和應等于傳輸線的特性阻抗。

如果驅動器內阻為10Ω,傳輸線特性阻抗為50Ω,那么端接電阻器約為40Ω。假設端接電阻器已經被放好,驅動器產生的1V信號就會遇到由50Ω總電阻和50Ω傳輸線構成的分壓器。這樣,到達傳輸線的將是0.5V。

粗略一看,好像一半的電壓不足以作為觸發信號使用。然而,當0.5V信號到達開路端,即傳輸線的遠端時,它遇到又一次阻抗突變。開路端的反射系數為1,0.5V入射信號以0.5V的振幅被反射回源端。在遠端,開路處的總電壓為0.5V入射電壓與0.5V反射電壓之和,即1V。

0.5V反射信號返回源端到達串聯端接電阻器時,往源端看進去的阻抗就是40Ω串聯電阻加上10Ω內阻,即50Ω。而傳輸線的特性阻抗也是50Ω,信號受到的瞬時阻抗沒有發生改變,不會產生反射。此時,信號被端接電阻器和內阻完全吸收。

這時,在遠端看到的是1V信號而沒有振鈴。下圖給出了當有和沒有40Ω源端串聯端接電阻器時,傳輸線遠端的波形。

在從驅動器出發的近端,緊接源端串聯端接電阻器之后測得的初始電壓正是進入傳輸線的入射電壓,大約為信號電壓的一半。而在源端必須等待反射波的返回,才能使此處的總電壓達到全電壓擺幅。

等待的時間等于往返時間,所以串聯電阻器之后的源端電壓將形成臺階架形狀。相對于信號的上升邊,傳輸線的往返時延越長,臺階架形狀就持續得越長。這是源端串聯端接傳輸線的基本特性,下圖給出了源端測得的電壓。

只要在源端附近沒有其他接收器接收該臺階架形狀,就不會引發問題。當其他器件連接在源端附近時,臺階架形狀就可能會造成問題,這時就需要采用其他拓撲結構和端接匹配方案。

15.3

短串聯傳輸線的反射

電路板上的線條常常要通過過孔區域或在元件密集區域布線。此時線寬必然變窄,收縮成頸狀。如果傳輸線上有這么一小段的線寬變化,特性阻抗一般就是變大的。那么,多長的線段和多大的阻抗改變會造成問題呢?

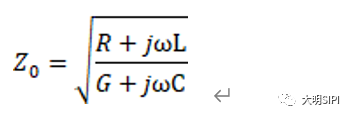

決定短傳輸線段對信號影響的3個特征是:突變引起的時延(T_D)、突變處的特性阻抗(Z_0)及信號的上升邊(RT)。如果突變時延大于上升邊,從電氣上講,突變處就算是比較長的,反射系數的作用就很明顯。反射系數的值直接影響突變處前端的反射。

阻抗突變引起了信號往返振蕩,從而形成了反射噪聲。這就要求設計特性阻抗均勻的互連。為了保持反射噪聲低于電壓擺幅5%需要保證特性阻抗的變化率小于10%。這就是為什么電路板上阻抗的典型指標為±10%。

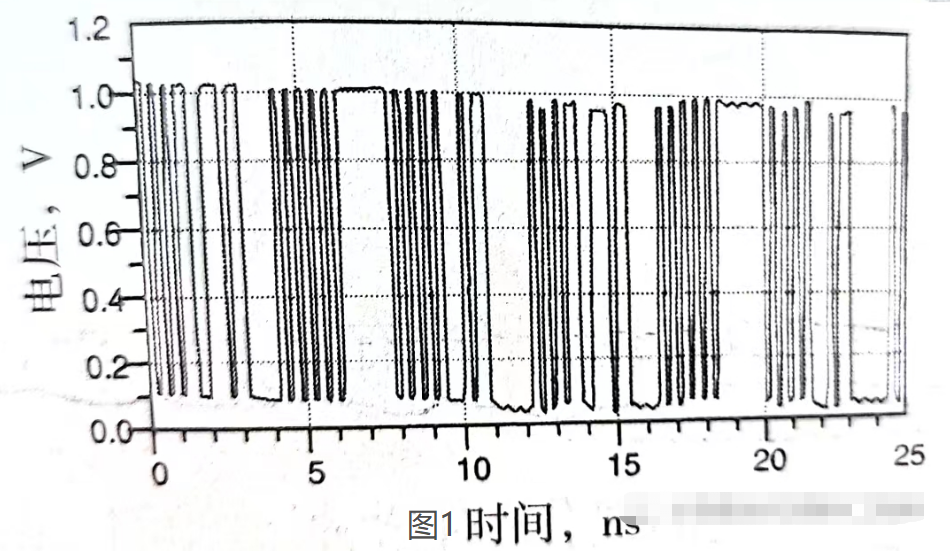

在中間插入一段異變傳輸線時,無論在第一個界面處發生的反射如何,它總是與第二個界面處發生的反射大小相等,方向相反。因為Z_1和Z_2值互換了。這樣,如果突變段長度很短,源于兩端的反射就能互相抵消,對信號完整性的影響就可以忽略。下圖為傳輸線上有25Ω短突變時的反射信號和傳輸信號。如果突變處的時延小于信號上升邊20%它就不會造成問題。從而得到了與前面相同的經驗法則,即可容許的阻抗突變的最大長度為 Len_max 。其中,len_max表示阻抗突變段的最大長度(單位為in),RT表示信號上升邊(單位為ns)。

如果突變段的時延小于信號上升邊20%則突變對信號質量造成的影響可以忽略。這就是經驗法則:突變段的長度(單位為in)應小于信號上升邊(單位為ns)。

例如,如果信號上升邊為0.5ns,則長度小于0.5in的頸狀就不會產生信號完整性問題。

15.4

短并聯傳輸線的反射

我們常常在一段均勻傳輸線上接一個分支,以使信號去往多個點扇出。如果分支很短,就稱其為樁線。樁線通常是球柵陣列封裝過程的產物。用總線排將所有的引腳匯流在一起,從而使鍵合用的壓焊塊比較容易鍍上金。制造后期再將總線排斷開,這樣就留下了一些短樁線連接到各個信號線上。

因為必須考慮到所有的反射,分析樁線的影響就變得很復雜。信號離開驅動器后,遇到了分支點。這時信號遇到的是兩段傳輸線的并聯阻抗。此阻抗較低,所以將產生的負反射返回源端。另一部分信號將沿兩個分支繼續傳播。當樁線上的信號到達樁線末端時,它將反射回分支點。然后,再從分支點反射到樁線末端,這樣就會在樁線上往返振蕩。同時,每當與分支點發生交界時,樁線中的部分信號將返回源端和遠端。每個交界處都是一個反射點。

決定樁線對信號影響程度的兩個重要特征是信號的上升邊和樁線的長度。在下面這個示例中,假設樁線位于傳輸線的中間,并且其特性阻抗和主線的相同。下圖給出了當樁線長度從上升邊的20%到60%時,仿真得到的反射信號和傳輸信號。

例如,如果驅動器的上升邊是1ns,則可以使用時延小于0.2ns的樁線,其長度約為1 in。我們又得到一條經驗法則,即 Len_stub?max 。其中,len_stub?max表示樁線可容許的最大長度(單位為in),RT表示信號上升邊(單位為ns)。

例如,若上升邊為1ns,就要確保樁線長度小于1in。如果上升邊為0.5ns,樁線就要短于0.5in。這很明顯,隨著上升邊變短,為控制樁線足夠短以使設計不影響信號質量,會變得愈加困難。

對于球柵陣列封裝,在制造中常常不可避免地使用電鍍樁線,這些樁線一般都小于0.25in。如果信號上升邊大于0.25ns,這些電鍍樁線就不會引發問題,但如果上升邊低于0.25ns,它們就必將造成問題,這時必須另選沒有電鍍樁線的封裝制造工藝。

-

驅動器

+關注

關注

52文章

8156瀏覽量

146019 -

電阻器

+關注

關注

21文章

3760瀏覽量

62042 -

接收器

+關注

關注

14文章

2458瀏覽量

71798 -

信號完整性

+關注

關注

68文章

1397瀏覽量

95385 -

時鐘信號

+關注

關注

4文章

445瀏覽量

28511

發布評論請先 登錄

相關推薦

【連載筆記】信號完整性-傳輸線物理基礎及其分類

傳輸線端接對電磁兼容的影響

信號完整 性--傳輸線與反射

信號完整性-傳輸線的反射與端接

信號完整性-傳輸線的反射與端接

評論