摘要:

本文將帶你了解高低頻的阻抗匹配電路概念及要點(diǎn),最后從阻抗匹配的角度分析高速電路的振鈴產(chǎn)生原因及解決辦法。

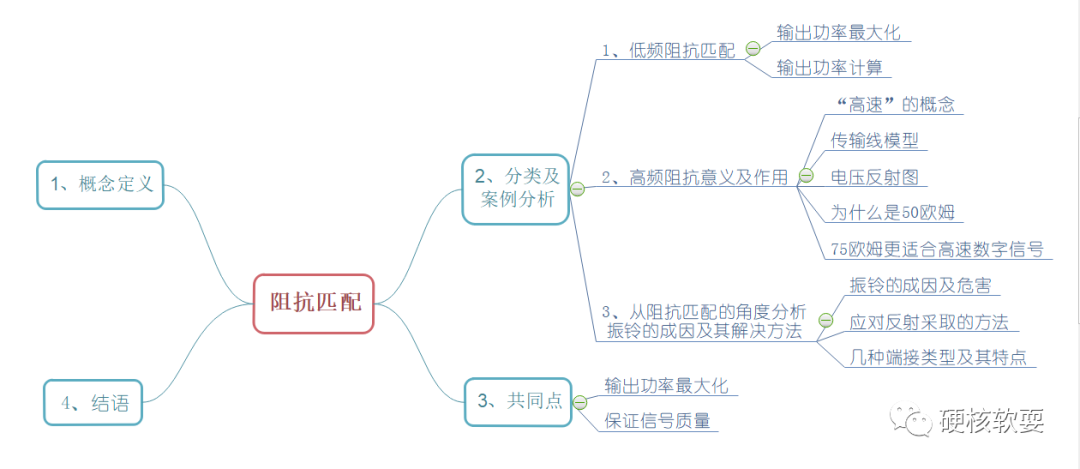

本章的思維導(dǎo)圖如下:

一、阻抗匹配相關(guān)概念

在具有電阻、電感和電容的電路里,對(duì)交流電所起的阻礙作用叫用阻抗,常用Z來(lái)表示。阻抗的大小由交流電的頻率f、電阻R、電感L、電容C共同決定。一個(gè)具體的電路,其阻抗隨交流電頻率的改變而改變。

1、輸入阻抗

輸入阻抗是指一個(gè)電路輸入端的等效阻抗。其計(jì)算方法為:在輸入端加上一個(gè)電壓源u,測(cè)量輸入端的電路i,則輸入阻抗Zi = u / i。直流情況下,輸入端等效為一個(gè)電阻,這個(gè)電阻的阻值就是輸入阻抗的大小。

輸入阻抗等同于電抗元件,反映的是對(duì)電流阻礙作用的大小。對(duì)于電壓驅(qū)動(dòng)電路,輸入阻抗越大,對(duì)電壓源的負(fù)載越輕,越容易被驅(qū)動(dòng),對(duì)信號(hào)源的影響越小;對(duì)于電流驅(qū)動(dòng)電路,輸入阻抗越小,對(duì)電流源的負(fù)載越輕,越容易被驅(qū)動(dòng),對(duì)信號(hào)源的影響越小。

對(duì)于低頻電路,一般情況下可以認(rèn)為:如果是用電壓源來(lái)驅(qū)動(dòng)的,則輸入阻抗越大越好;如果是用電流源來(lái)驅(qū)動(dòng)的,則阻抗越小越好。

對(duì)于高頻電路,過(guò)高的輸入阻抗會(huì)造成信號(hào)的反射,導(dǎo)致振鈴和過(guò)沖,造成信號(hào)完整性問(wèn)題。

無(wú)論高、低頻電路,如果要獲取最大輸出功率,都需要做阻抗匹配。

2、輸出阻抗

實(shí)際的信號(hào)源、放大器或者電源,都存在輸出阻抗(理想的電壓源輸出阻抗為零),輸出阻抗就是源的內(nèi)阻。我們常用一個(gè)理想電壓源串聯(lián)一個(gè)電阻Rs來(lái)等效一個(gè)實(shí)際的電壓源,這個(gè)Rs就是電壓源的內(nèi)阻。當(dāng)電壓源向負(fù)載供電時(shí),由于電流I經(jīng)過(guò)Rs,根據(jù)歐姆定律,Rs上的電壓為 U(Rs) = I x Rs,導(dǎo)致負(fù)載上的電壓小于電壓源電壓,即負(fù)載電壓下降了。

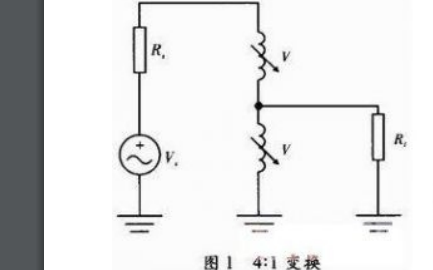

3、阻抗匹配

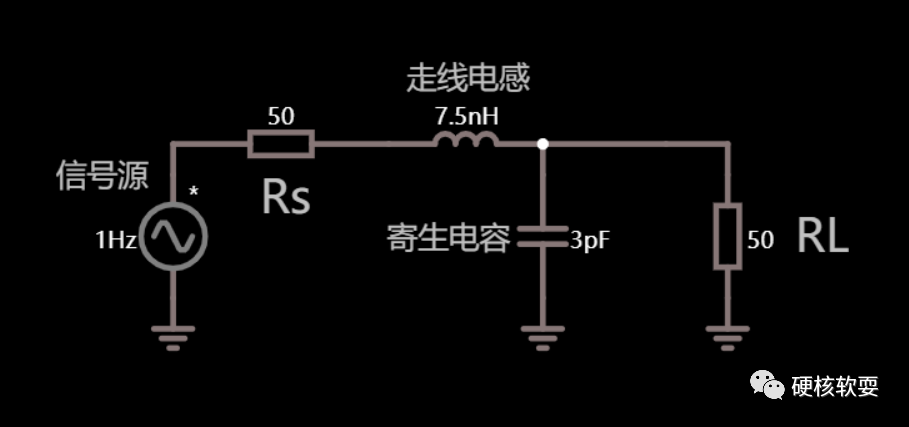

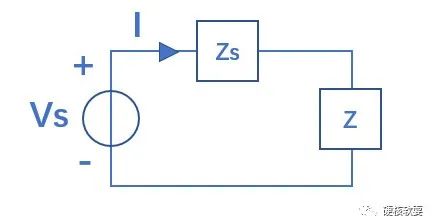

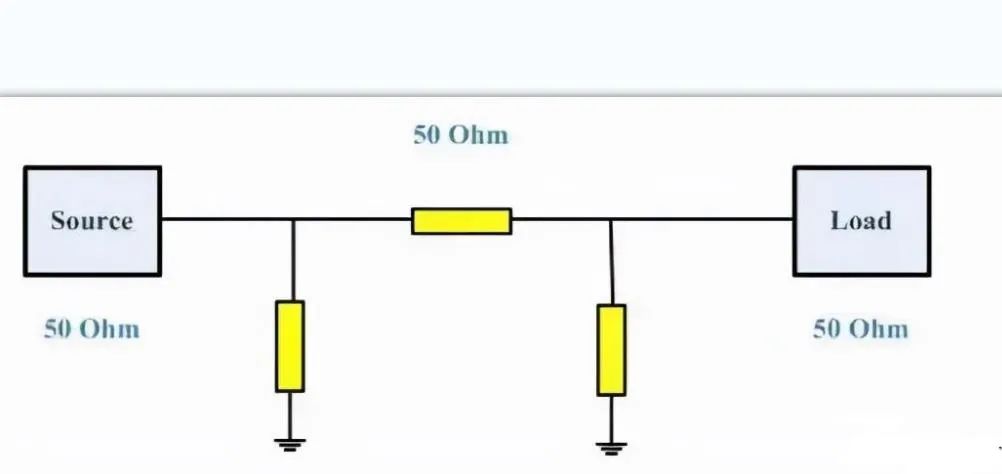

阻抗匹配是指信號(hào)源或者傳輸線跟負(fù)載之間的一種合適的搭配方式。無(wú)論高低頻電路,源與負(fù)載之間的關(guān)系均可等效于以下電路(元器件參數(shù)可變):

圖1

二、阻抗匹配分類

1、低頻下的阻抗匹配

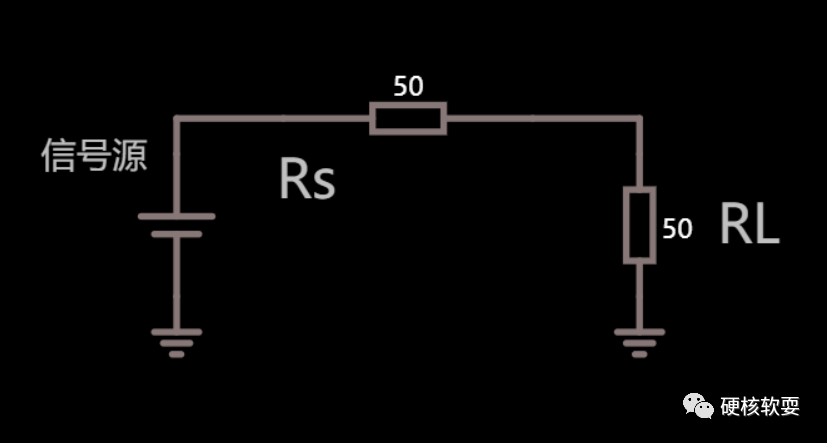

當(dāng)信號(hào)源頻率低時(shí),寄生電感阻抗極小等效于短路,寄生電容阻抗極大等同于開路,于是圖1可以簡(jiǎn)化為以下電路:

圖2

將信號(hào)源看成直流電壓源進(jìn)行分析,Rs為電壓源的內(nèi)阻,負(fù)載為RL,電壓源電動(dòng)勢(shì)設(shè)為U,則回路電流 I = U / (Rs + RL),由式子可以看出,回路電流由電壓源內(nèi)阻和負(fù)載共同決定,當(dāng)Rs一定時(shí),Rl越大,電流I越小,反之則I越大。 負(fù)載與電壓源及其內(nèi)阻構(gòu)成串聯(lián)電路,RL與Rs按照它們的電阻值比值共同分配電壓源的電壓,RL越大,則負(fù)載上的電壓越大。這里需要注意的是, 負(fù)載分到的電壓大不等于負(fù)載消耗的功率也大 ,因?yàn)楣β什粌H與電壓有關(guān),還和電流相關(guān),此處計(jì)算負(fù)載上的功率 :

P = U*I

= I^2 * RL

= [ U / (Rs + RL) ]^2 * Rl

= U^2 / { [RL-Rs]2 / RL] + 4Rs }

可以看出,當(dāng)負(fù)載電阻跟信號(hào)源內(nèi)阻相等時(shí),負(fù)載可獲得最大輸出功率,這就是我們常說(shuō)的阻抗匹配之一。當(dāng)然,如果我們想要負(fù)載電壓大,就選擇阻值大的負(fù)載。

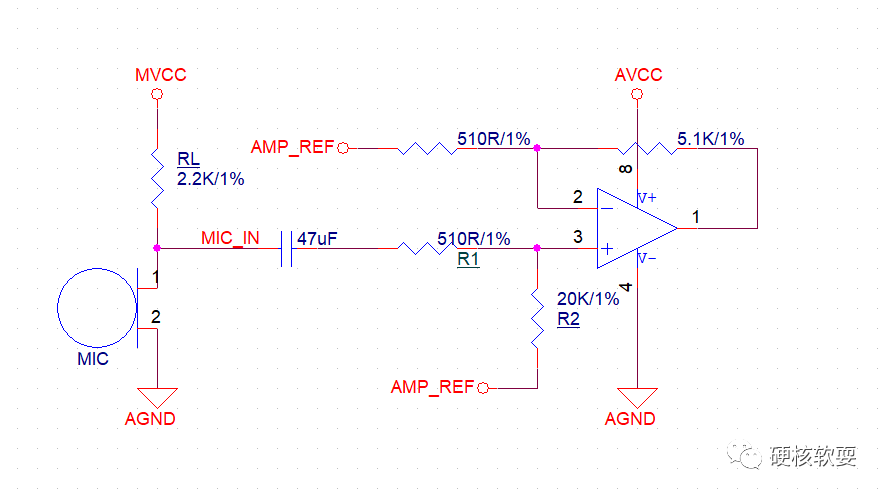

舉例麥克風(fēng)放大電路分析輸入阻抗、輸出阻抗以及阻抗匹配的關(guān)系:

圖3

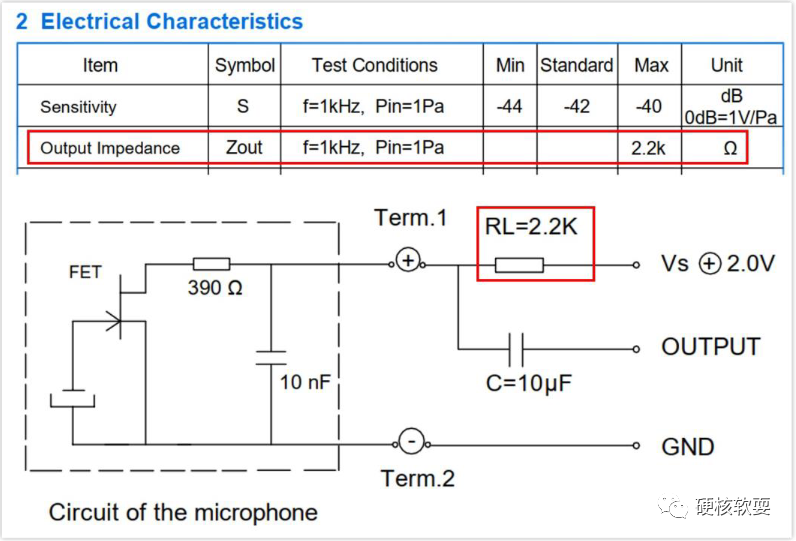

先看一下MIC的內(nèi)部電路:

圖4

如圖,芯片規(guī)格書也提供了咪頭的內(nèi)部電路,其實(shí)就是個(gè)FET管放大電路。如果好好學(xué)習(xí)的話(論大學(xué)好好學(xué)習(xí)的重要性),就知道這個(gè)FET管放大電路的輸出電阻就是那個(gè)RL,廠家這個(gè)RL是2.2KΩ,所以它就標(biāo)注輸出阻抗是2.2KΩ。

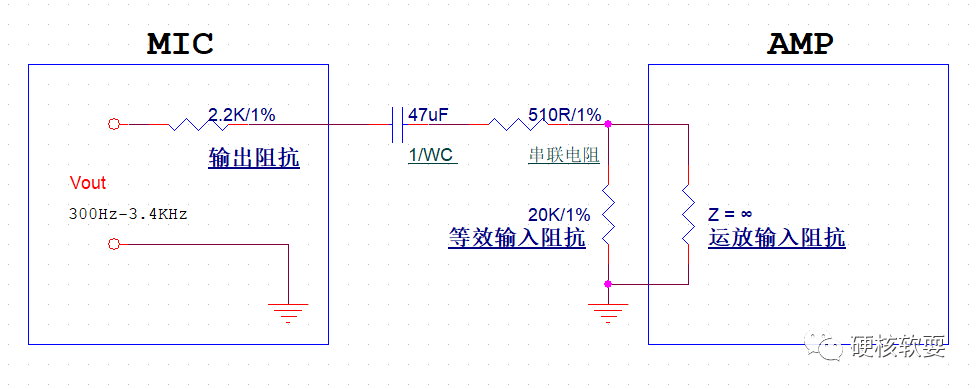

再看信號(hào)的通路,信號(hào)從咪頭出發(fā)通過(guò)電容,在兩個(gè)電阻分壓后輸入到運(yùn)放的同相端,由于運(yùn)放的同相端輸入阻抗無(wú)窮大,所以分析阻抗時(shí)可視為斷路,則信號(hào)通路可等效為以下電路:

圖5

由圖可見(jiàn),MIC的輸出阻抗、電容容抗、串聯(lián)電阻R1(510Ω)及R2(20K)構(gòu)成串聯(lián)分壓電路,信號(hào)在R2上的分壓輸入到運(yùn)放的同相端。因?yàn)檫\(yùn)放的輸入阻抗很大(MΩ級(jí)別),所以信號(hào)輸入到運(yùn)放的等效輸入阻抗為R2,即20KΩ。如果我們想要輸入信號(hào)不能過(guò)小,那么R2不能用小電阻,不然達(dá)不到設(shè)計(jì)的放大目標(biāo),這種達(dá)不到設(shè)計(jì)性能的情況,也可以叫做阻抗失配。當(dāng)然此處還有一個(gè)小細(xì)節(jié),為什么要加上R2呢?如果斷開R2,則MIC的信號(hào)幾乎是全部輸入到運(yùn)放,但是因?yàn)檫\(yùn)放的輸入阻抗很大,容易把干擾也放大,所以用外部電阻R2調(diào)節(jié)信號(hào)的輸入阻抗。

2、高頻下的阻抗匹配

當(dāng)信號(hào)源頻率極高時(shí),串聯(lián)寄生電感阻抗不可忽略不計(jì),并聯(lián)寄生電容阻抗不可視為無(wú)窮大,若僅僅考慮內(nèi)阻與負(fù)載的關(guān)系,忽略實(shí)際走線的寄生電感和寄生電容,當(dāng)源阻抗和負(fù)載為復(fù)數(shù)時(shí),則圖1可以化成以下電路:

圖6

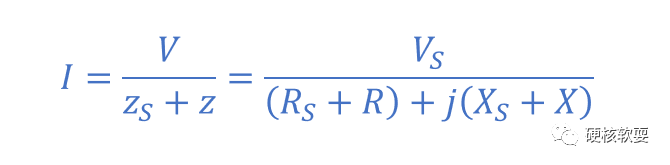

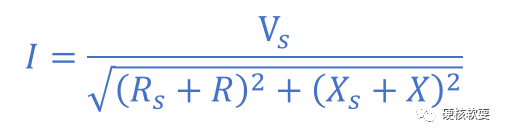

其信號(hào)源電壓為Vs,信號(hào)源內(nèi)阻為Zs = Rs + jXs,負(fù)載阻抗為Z = R +jX,電路中的電流為:

電流的幅度值為:

負(fù)載處的功率為:

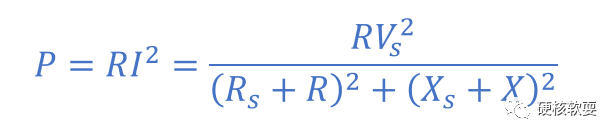

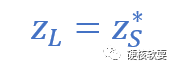

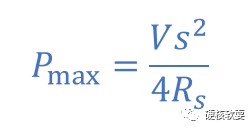

參照前文得到的結(jié)論,當(dāng)R = Rs,X = -Xs時(shí),負(fù)載的功率最大,即輸出功率最大。這時(shí)有:

即信號(hào)源內(nèi)阻與負(fù)載進(jìn)行了共軛匹配,此時(shí)負(fù)載功率為:

Q:如果負(fù)載阻抗不能滿足共軛匹配條件怎么辦?

A:很簡(jiǎn)單,在源與負(fù)載之間加匹配網(wǎng)絡(luò),將負(fù)載阻抗變換成信號(hào)源阻抗的共軛匹配。這個(gè)阻抗變換是阻抗匹配的重要方法之一。

三、高速電路的反射及阻抗匹配

1、高速電路相關(guān)概念

1.1 集總參數(shù)電路與傳輸線

隨著頻率的提高,一般到十幾兆開始,信號(hào)的傳輸不再是電壓和電流,而是依靠電場(chǎng)和磁場(chǎng)傳播,電磁場(chǎng)被鎖定在導(dǎo)線和參考地之間。由于具有這種高頻效應(yīng),若等效為電路的話,導(dǎo)線上各個(gè)位置處的電壓不同(周期重復(fù)點(diǎn)除外),各個(gè)位置的電流也不同,這是與集總參數(shù)電路的明顯區(qū)別,這種情況下稱為分布參數(shù)電路,導(dǎo)線稱為傳輸線。

若用 l表示電路本身的最大線性尺寸,用λ表示電壓或電流的波長(zhǎng),則當(dāng)不等式 λ>>l 成立,電路便可視為集總參數(shù)電路,否則便需作為分布參數(shù)電路處理。

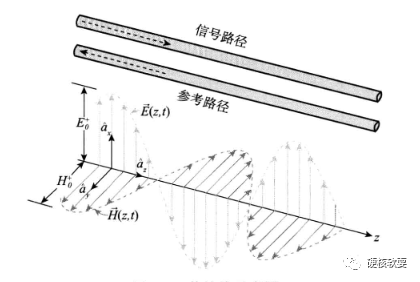

最簡(jiǎn)單的傳輸線由一對(duì)導(dǎo)體構(gòu)成,把信號(hào)以電磁波的形式從一端送到另一端。構(gòu)成傳輸線的形式多種多樣,比如,PCB上的走線、雙絞線、同軸電纜等。圖7為傳輸線結(jié)構(gòu)的簡(jiǎn)單示意圖,兩個(gè)導(dǎo)體中一個(gè)稱為“信號(hào)路徑”,另一個(gè)稱為“參考路徑”或者“返回路徑”。兩個(gè)導(dǎo)體構(gòu)成了電磁波能夠向前傳播的物理環(huán)境,圖7中同時(shí)畫出了某一特定時(shí)刻電場(chǎng)強(qiáng)度和磁場(chǎng)強(qiáng)度沿空間分布的情況。當(dāng)傳輸線上施加信號(hào)時(shí),隨著信號(hào)向前傳播,沿空間分布的電場(chǎng)和磁場(chǎng)也發(fā)生變化,信號(hào)能量以電磁波的形式傳輸?shù)侥┒恕W兓碾妶?chǎng)和磁場(chǎng)產(chǎn)生電流,外在的表現(xiàn)就像是電流端從信號(hào)路徑流入,然后從參考路徑流回到發(fā)送端一樣,這也是“參考路徑”被稱為“返回路徑”的原因。

圖7

傳輸線的行為特征和電容、電感、電阻等集總元件有非常顯著的區(qū)別,必須用“動(dòng)態(tài)”的思維才能理解傳輸線的特性。

1.2 高速與高頻的關(guān)系

高速與高頻的關(guān)系可以用兩句話概括:

- 高速不等同于高頻

- 高頻是高速的載體

隨著現(xiàn)代制程的縮小,電平跳變比以前更快,一些低頻器件也要當(dāng)成高速電路對(duì)待。舉個(gè)栗子,1MHz的方波頻率只是1MHz,但是邊沿十分陡峭,這也意味著方波中含有豐富的高次諧波,高次諧波的頻率遠(yuǎn)遠(yuǎn)大于1MHz,所以,高速的劃分不能僅僅以頻率來(lái)做界定。

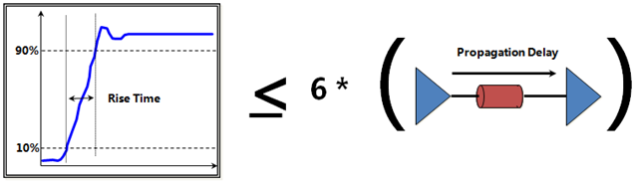

“那我們所說(shuō)的高速設(shè)計(jì)的邊界條件是什么呢?小陳認(rèn)為是分布參數(shù),傳輸線理論中的‘長(zhǎng)線’,是上升時(shí)間小于六分之一傳輸線延時(shí)”——引自《高速先生》

圖8

那么多長(zhǎng)才算長(zhǎng)線呢?

PCB上信號(hào)傳輸速度為6inch/ns,也就是0.1524m/ns,如果我們知道上升沿時(shí)間,根據(jù)公式 t < 6*L/(0.1524m) 便可算出長(zhǎng)度值。

當(dāng)前常規(guī)的時(shí)鐘芯片,上升沿通常在2ns左右,在這些信號(hào)眼中,2000mil以上叫做長(zhǎng)線。一些新的時(shí)鐘芯片,雖然速率可能只有幾十兆,但是芯片工藝有較大的改進(jìn)上升沿較快,可能會(huì)達(dá)到400ps,在這些信號(hào)眼中,400mil以上叫做長(zhǎng)線。與其上升時(shí)間相當(dāng)?shù)模€有大部分LVDS信號(hào)等。

當(dāng)前DDR3,上升沿通常在100ps左右,在這些信號(hào)眼中,100mil以上叫做長(zhǎng)線。對(duì)于10G信號(hào)來(lái)說(shuō),上升沿通常在25ps左右,這時(shí)候,25mil叫做長(zhǎng)線。

2、高速電路的反射

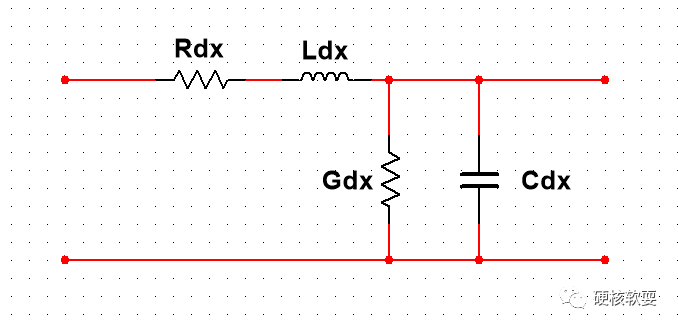

前文說(shuō)過(guò),高頻是高速的載體,在分析高速電路時(shí),從高頻信號(hào)入手,當(dāng)信號(hào)頻率極高時(shí),傳輸線上的寄生電感和寄生電容的阻抗影響不可忽略。可以用下圖模型來(lái)表示單位長(zhǎng)度的傳輸線:

圖9

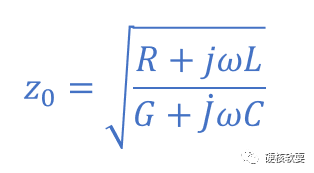

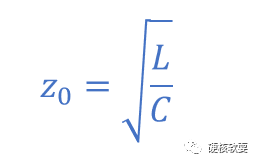

此模型下的特征阻抗表達(dá)式為:

在實(shí)際的PCB應(yīng)用中傳輸線的電阻部分,可以忽略不計(jì),即上式中的R和G為0,PCB傳輸線特征阻抗的一般表達(dá)式:

L是單位長(zhǎng)度傳輸線的固有電感,C是單位長(zhǎng)度傳輸線的固有電容。

需要注意的是,只有在傳輸線均勻的情況下才存在特征阻抗,即信號(hào)不論走到傳輸線的什么位置,感受到的阻抗都是相同的,即Z0。通常我們說(shuō)的50Ω阻抗控制就是指特征阻抗。如果傳輸線非均勻,那么信號(hào)在這個(gè)傳輸線上傳輸?shù)讲煌恢脮r(shí)感受到的瞬態(tài)阻抗不同,因此沒(méi)有特征阻抗。

反射

信號(hào)在不均勻的傳輸線上傳輸,在不同位置感受到的瞬態(tài)阻抗不同導(dǎo)致反射,即阻抗不連續(xù)導(dǎo)致反射。

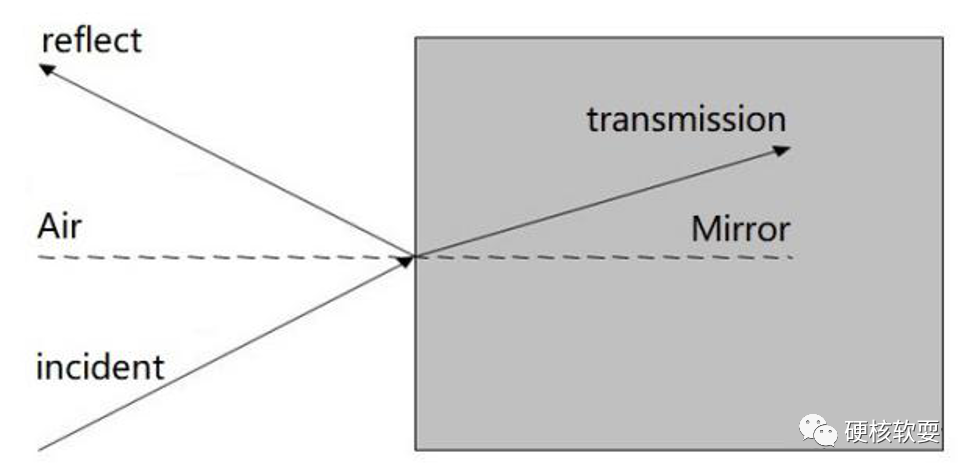

反射現(xiàn)象在自然界中普遍存在,例如光在不同介質(zhì)中傳播時(shí)發(fā)生反射,當(dāng)光從空氣射向玻璃,因?yàn)榭諝夂筒A莾煞N不同的介質(zhì)(換言之,阻力不同),有一部分光被反射,另一部分光會(huì)折射進(jìn)入另一種介質(zhì),如下圖:

圖10

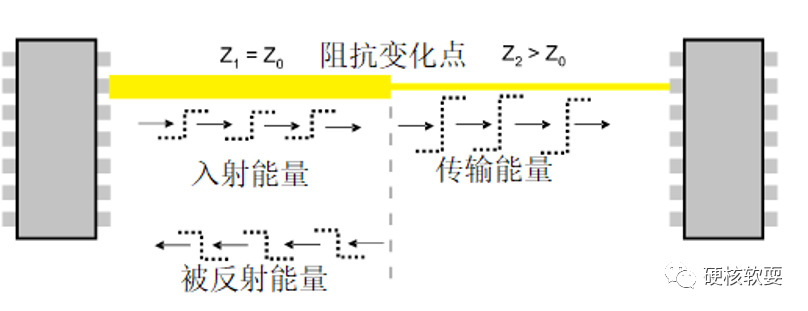

同樣地,信號(hào)也一樣,如果傳輸線的阻抗不一致,在阻抗跳變的地方,一部分能量繼續(xù)傳輸,一部分能量會(huì)被反射回去,如下圖:

圖11

下面讓我們用更嚴(yán)謹(jǐn)?shù)睦碚摵臀锢矶ɡ砉阶C明上述的觀點(diǎn)正確:

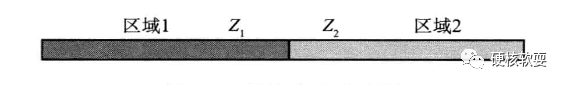

假設(shè)信號(hào)傳輸過(guò)程中,經(jīng)過(guò)兩個(gè)阻抗不同的區(qū)域,如圖12所示,區(qū)域1阻抗為Z1,區(qū)域2阻抗為Z2,現(xiàn)在我們考察在區(qū)域分界面處的電壓電流情況。

圖12 阻抗突變示意圖

很明顯,在分界面處,電壓必須是連續(xù)的,否則,在分界面處會(huì)產(chǎn)生無(wú)窮大的電場(chǎng),這在真實(shí)世界中是不可能的。同樣,分界面兩側(cè)的電流必須連續(xù),否則分界面處會(huì)產(chǎn)生無(wú)窮大的磁場(chǎng)(這聽起來(lái)是不是和“電容電壓不能突變,電感電流不能突變“有聯(lián)系,感興趣的同學(xué)可以深入研究背后的奧妙~)。

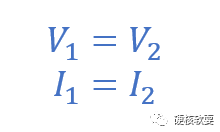

因此,下式1成立:

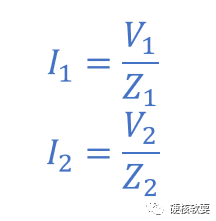

根據(jù)歐姆定律,必然有式2:

顯然如果Z1≠Z2的情況下,上面的1、2式子不可能同時(shí)成立。如何解決這一困境?反射理論提供了一個(gè)很好的答案。從電磁波的角度來(lái)理解反射,在分界面處,一部分正向傳播,另一部分反向傳播。從電壓電流角度,我們可以把區(qū)域1的電壓V1分成兩部分,一部分以電壓Vinc正向傳輸,另一部分以電壓Vreflect反向傳輸。其中Vinc稱為入射電壓,Vreflect稱為反射電壓。而V2記為Vtrans,稱作傳輸電壓。

由于分界面兩側(cè)電壓相等,所以有式3:

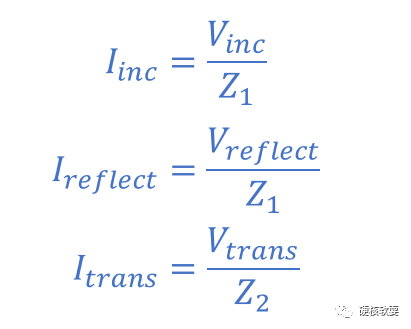

同理,入射電壓Vin產(chǎn)生一個(gè)正向電流Iinc,反射電壓Vreflect產(chǎn)生一個(gè)反向電流Ireflect。區(qū)域2的電流記為Itrans,要使分界面兩側(cè)電流相等,必有式4:

由此可得,任一截面處的電壓或者電流都是入射波和反射波疊加的結(jié)果。

根據(jù)歐姆定律,有式5:

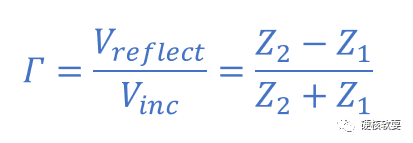

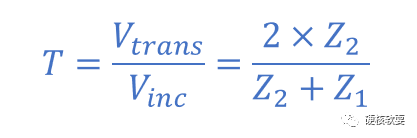

聯(lián)合3、4、5式可得式4、式5:

Γ稱為反射系數(shù),T稱為傳輸系數(shù)。

當(dāng)反射系數(shù)Γ ≠ 0,必然存在阻抗不連續(xù)點(diǎn)并引起信號(hào)反射。

3、反射的危害

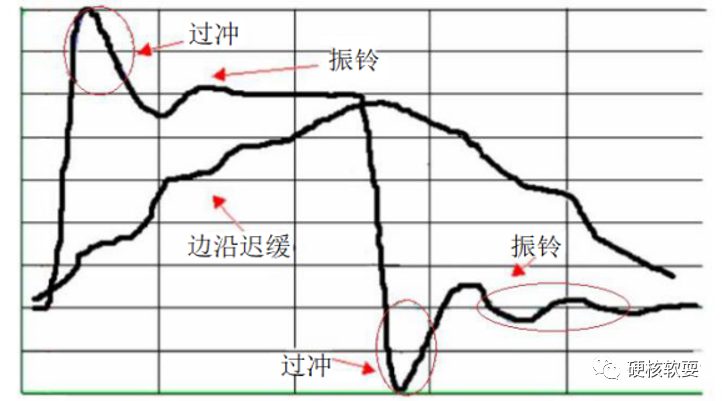

反射會(huì)造成信號(hào)出現(xiàn)過(guò)沖(Overshoot)、振鈴(Ringing)、邊沿遲緩(回勾現(xiàn)象)。過(guò)沖是振鈴的欠阻尼狀態(tài),邊沿遲緩是振鈴的過(guò)阻尼狀態(tài)。下圖為信號(hào)反射的三種表現(xiàn)形式:

圖13

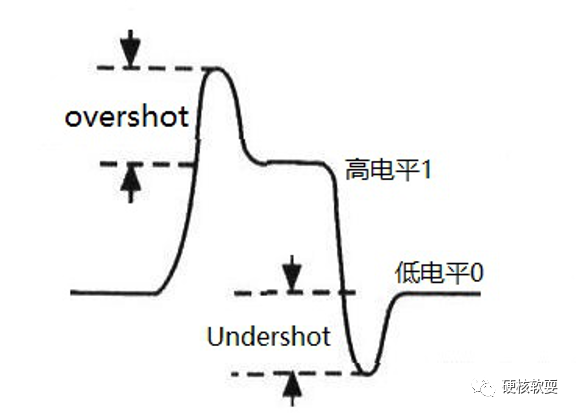

3.1 過(guò)沖和下沖

過(guò)沖指的是第一個(gè)峰值或谷值超過(guò)設(shè)定電壓值,下沖是指下一個(gè)谷值或峰值,對(duì)于上升沿來(lái)說(shuō),過(guò)沖是指最高電壓;對(duì)于下降沿來(lái)說(shuō),過(guò)沖是指最低電壓。如下圖所示:

圖14

過(guò)沖嚴(yán)重時(shí)會(huì)引起保護(hù)二極管工作,導(dǎo)致過(guò)早地失效,嚴(yán)重時(shí)還會(huì)損壞器件。而過(guò)分的下沖,能夠引起假的時(shí)鐘或數(shù)據(jù)的錯(cuò)誤,這樣可能會(huì)給器件帶來(lái)潛在的累積性傷害,縮短其工作壽命,從而影響產(chǎn)品的長(zhǎng)期穩(wěn)定性。一般信號(hào)的發(fā)送端的阻抗較低,信號(hào)接收端的阻抗較高,如果發(fā)送端的與接收端的阻抗不匹配,發(fā)送的信號(hào)會(huì)在發(fā)送端和接收端之間來(lái)回反射,從而導(dǎo)致信號(hào)的反射出現(xiàn)過(guò)沖和下沖。

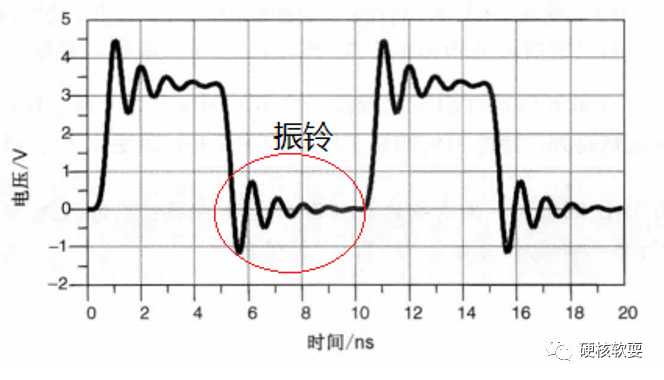

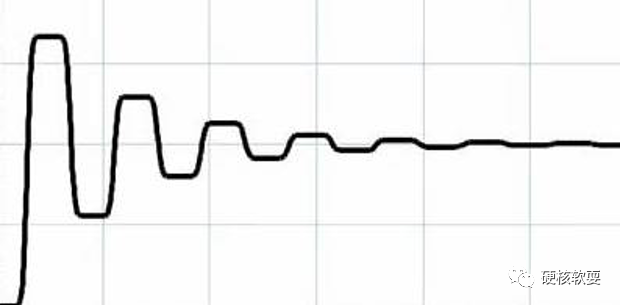

3.2 振鈴

過(guò)沖和下沖反復(fù)就會(huì)出現(xiàn)振鈴現(xiàn)象,過(guò)沖往往伴隨有振鈴,或者說(shuō),過(guò)沖是振鈴的一部分。振鈴產(chǎn)生的第一次峰值電壓,就是過(guò)沖。為什么要將過(guò)沖和振鈴分開來(lái)講,是因?yàn)樗麄兊奈:Σ煌疋彸司哂羞^(guò)沖的危害之外還有它的波動(dòng)可能會(huì)多次超過(guò)閾值判定電壓造成誤判,并且會(huì)急劇地增加功耗,影響器件壽命。下面是振鈴的表現(xiàn)形式:

圖15

4、深入探究反射的過(guò)程及解決方法

4.1 理想的源->負(fù)載傳輸模型

最理想模型是希望源端(Source)的輸出阻抗為50歐姆,傳輸線的阻抗為50歐姆,負(fù)載端(Load)的輸入阻抗也是50歐姆,一路50歐姆下去,這是最理想的。

圖16

至于為什么是50歐姆,這里有個(gè)故事……

我們知道射頻的傳輸需要天線和同軸電纜,射頻信號(hào)的傳輸我們總是希望盡可能傳輸更遠(yuǎn)的距離,為了傳輸更遠(yuǎn)的距離,我們往往希望用很大的功率去發(fā)射信號(hào)便于覆蓋更大的通信范圍。可是實(shí)際上,同軸電纜本身是有損耗的,和我們平常使用的導(dǎo)線一樣,如果傳輸功率過(guò)大,導(dǎo)線會(huì)發(fā)熱甚至熔斷。這樣,我們就有一種期望,試圖尋找一種能夠傳輸大功率,同時(shí)損耗又非常小的同軸電纜。

圖17

大概在1929年,貝爾實(shí)驗(yàn)室做了很多實(shí)驗(yàn),最終發(fā)現(xiàn)符合這種大功率傳輸,損耗小的同軸電纜其特征阻抗分別是30歐姆和77歐姆。其中,30歐姆的同軸電纜可以傳輸?shù)墓β适亲畲蟮模?7歐姆的同軸電纜傳輸信號(hào)的損耗是最小的。30歐姆和77歐姆的算術(shù)平均值為53.5歐姆,30歐姆和77歐姆的幾何平均值是48歐姆,我們經(jīng)常所說(shuō)的50歐姆系統(tǒng)阻抗其實(shí)是53.5歐姆和48歐姆的一個(gè)工程上的折中考慮,考慮最大功率傳輸和最小損耗盡可能同時(shí)滿足。而且通過(guò)實(shí)踐發(fā)現(xiàn),50歐姆的系統(tǒng)阻抗,對(duì)于半波長(zhǎng)偶極子天線和四分之一波長(zhǎng)單極子天線的端口阻抗也是匹配的,引起的反射損耗是最小的。

我們常見(jiàn)的系統(tǒng)中,比如電視TV和廣播FM接收系統(tǒng)中,其系統(tǒng)阻抗基本上都是75歐姆,正是因?yàn)?5歐姆射頻傳輸系統(tǒng)中,信號(hào)傳輸?shù)膿p耗是最小的,TV和廣播FM接收系統(tǒng)中,信號(hào)的傳輸損耗是重要的考慮因素。而對(duì)于帶有發(fā)射的電臺(tái)而言,50歐姆是很常見(jiàn)的,因?yàn)樽畲蠊β蕚鬏斒俏覀兛紤]的主要因素,同時(shí)損耗也比較重要。這就是為什么我們的對(duì)講機(jī)系統(tǒng)中,經(jīng)常看到的都是50歐姆的參數(shù)指標(biāo)。

雖然50歐姆的指標(biāo)比較常見(jiàn),但75Ω電纜更適合于高頻數(shù)字信號(hào),因?yàn)?5Ω同軸電纜的電容比50Ω同軸電纜的電容低(同軸傳輸線結(jié)構(gòu)決定),而更低的電容有利于避免與邏輯低和邏輯高之間的快速過(guò)渡相關(guān)的高頻內(nèi)容過(guò)度衰減。

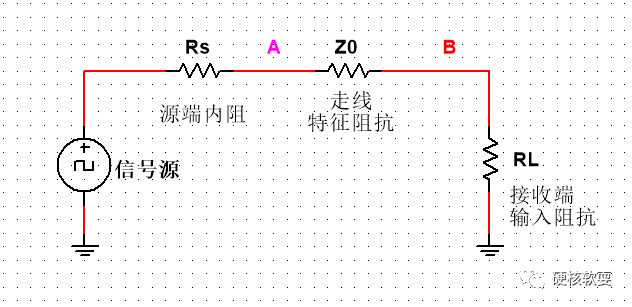

4.2 實(shí)際的傳輸模型

然而實(shí)際情況是:源端阻抗不會(huì)是50ohm,負(fù)載端阻抗也不會(huì)是50ohm。常見(jiàn)的驅(qū)動(dòng)端(源端)輸出阻抗Rs比較低,一般在幾十歐姆以內(nèi),而接收端(負(fù)載端)輸入阻抗RL很高,通常在幾百KΩ以上,PCB的特征阻抗Z0一般和源端Rs、終端RL都不相同,實(shí)際的信號(hào)通路等效模型如下圖:

圖18

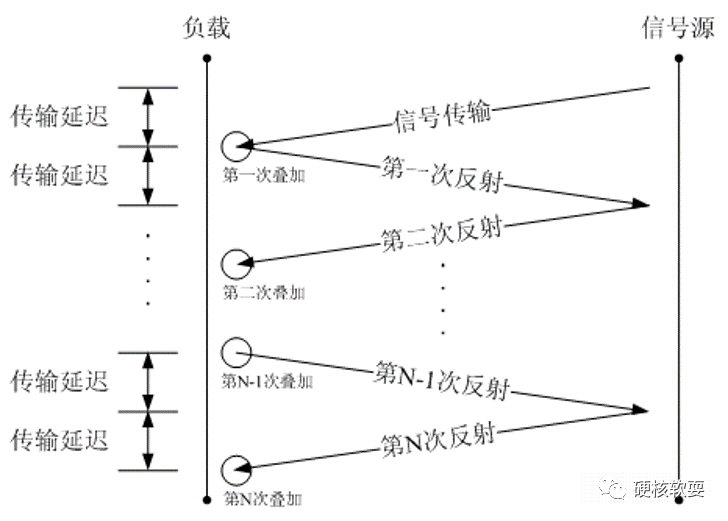

一般情況下,接收端(負(fù)載端)輸入阻抗RL很高,在分析時(shí)可看成開路。圖18中,A、B是阻抗不連續(xù)點(diǎn),信號(hào)將在這兩點(diǎn)多次反射,疊加,最終改變信號(hào)的形狀。3.1小節(jié)所闡述的過(guò)沖和下沖是由信號(hào)第一次反射導(dǎo)致,3.2小節(jié)的振鈴則是信號(hào)多次反射形成。下圖是振鈴產(chǎn)生的原因(B點(diǎn)表示負(fù)載,A點(diǎn)表示信號(hào)源):

圖19

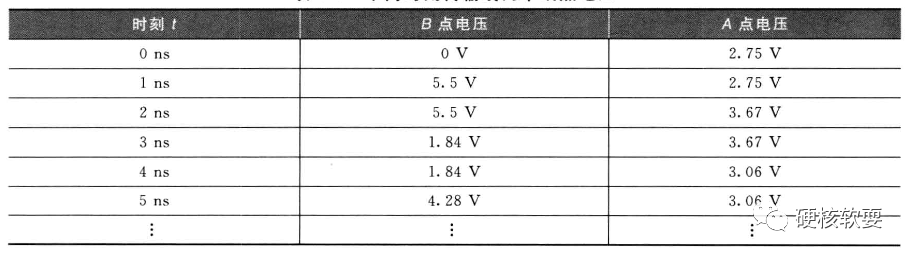

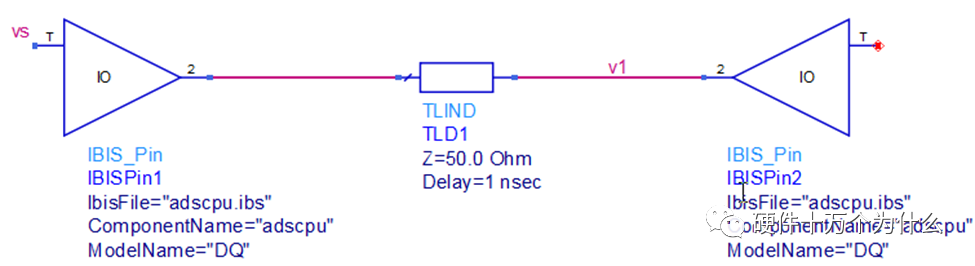

4.3 使用反彈圖計(jì)算反射波形

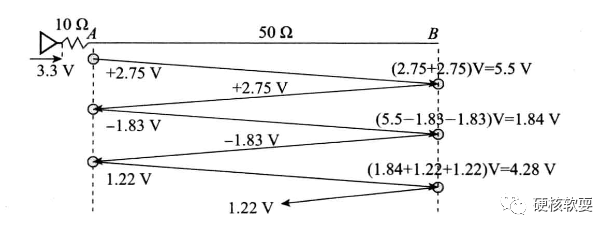

在4.2中,我們知道振鈴的產(chǎn)生來(lái)源于信號(hào)的多次反射,在這小節(jié)中,我們通過(guò)一個(gè)實(shí)例來(lái)計(jì)算反射對(duì)波形的影響。這個(gè)例子中,我們使用特征阻抗Z0為50Ω的傳輸線,信號(hào)上升時(shí)間0ns,即理想方波信號(hào),傳輸線延時(shí)1ns,傳輸線末端開路(RL=+∞),并且假定驅(qū)動(dòng)器輸出阻抗Rs為10Ω,如下圖所示:

圖20

第1次反射:信號(hào)在0ns時(shí)從芯片內(nèi)部發(fā)出,經(jīng)過(guò)10Ω輸出阻抗和50ΩPCB特征阻抗的分壓,實(shí)際加到PCB走線上的信號(hào)為A點(diǎn)電壓[3.3×50/(10+50)]V = 2.75V。1ns后信號(hào)傳輸?shù)皆炊薆點(diǎn),由于B點(diǎn)開路,阻抗無(wú)窮大,反射系數(shù)Γ=1,反射信號(hào)電壓為Γ?2.75V = 2.75V。此時(shí)B點(diǎn)測(cè)量電壓是(2.75+2.75)V = 5.5V。這里需要注意的一點(diǎn)是,在t=1ns這一時(shí)刻,B點(diǎn)的測(cè)量電壓是入射電壓與反射電壓的疊加。

第2次反射:2.75V的反射電壓在t=2ns時(shí)刻回到A點(diǎn),阻抗從50Ω變?yōu)?0Ω,發(fā)生負(fù)反射(注意此時(shí)從B點(diǎn)反射回來(lái)的2.75V信號(hào)向A點(diǎn)傳播,對(duì)于A點(diǎn)來(lái)說(shuō)相當(dāng)于入射電壓),反射系數(shù)為Γ = (10-50)/(10+50) = -2/3。所以A點(diǎn)反射電壓為2.75V×(-2/3) = -1.83V。此時(shí)A點(diǎn)測(cè)量電壓同樣是入射電壓和反射電壓的疊加,即(2.75+2.75-1.83)V = 3.67V。

第3次反射:-1.83V反射電壓向B點(diǎn)傳輸,t=3ns時(shí)刻到達(dá)B點(diǎn),再次發(fā)生全反射,反射電壓-1.83V。此時(shí)B點(diǎn)測(cè)量電壓為(5.5-1.83-1.83)V = 1.84V。

第4次反射:從B點(diǎn)反射回的-1.83V電壓在4ns時(shí)到達(dá)A點(diǎn),再次發(fā)生負(fù)反射,反射電壓1.22V。此時(shí)A點(diǎn)測(cè)量電壓為(3.67-1.83+1.22)V = 3.06V。

第5次反射:1.22V反射電壓在5ns時(shí)刻到達(dá)B點(diǎn)再次發(fā)生全反射,反射電壓1.22V。此時(shí)B點(diǎn)測(cè)量電壓為(1.84+1.22+1.22)V = 4.28V。

第6次反射:……

第7次反射:……

……

圖21

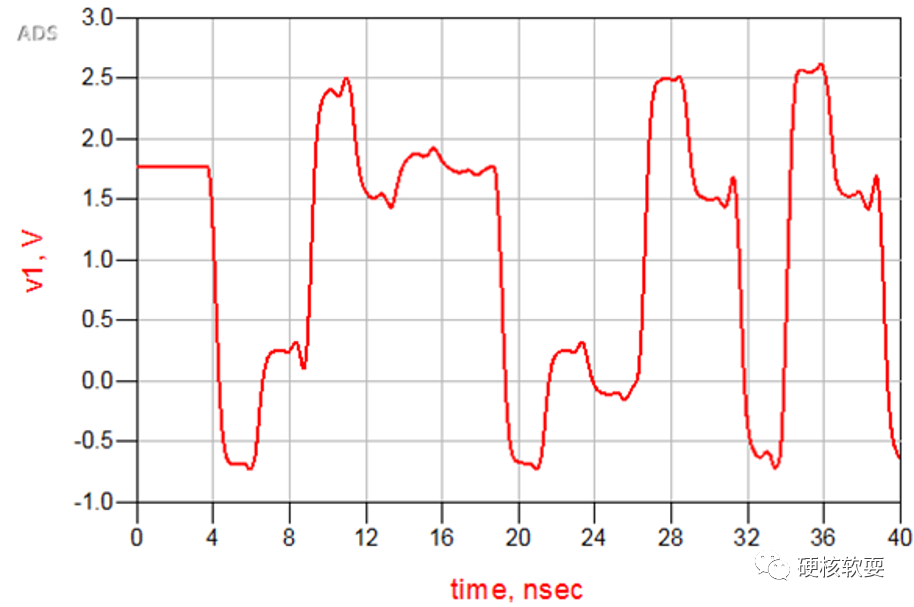

對(duì)于任何一個(gè)端點(diǎn),一旦發(fā)生反射,該點(diǎn)電壓就發(fā)生跳變,跳變的電壓會(huì)一直持續(xù)到信號(hào)在該點(diǎn)再次發(fā)生發(fā)射為止。觀察A、B點(diǎn)電壓,存在上下波動(dòng),這就是振鈴現(xiàn)象。它們的電平波動(dòng)可由下圖所示:

圖22

4.3 解決信號(hào)反射的方法

由前文可知,振鈴現(xiàn)象的原因是由信號(hào)反射引起的,而信號(hào)反射的根本原因就是阻抗不匹配,所以要減小乃至消除信號(hào)反射,必須進(jìn)行阻抗匹配。

端接

高速電路常見(jiàn)的阻抗匹配方法是端接,通過(guò)采用電阻端接匹配來(lái)實(shí)現(xiàn)阻抗一致性。常見(jiàn)的端接方式有源端端接、終端并聯(lián)端接、戴維寧端接、RC端接、差分端接等。那么端接電阻要使用多少?端接電阻怎么放置?阻值選擇多大呢?

1)點(diǎn)對(duì)點(diǎn)拓?fù)浣Y(jié)構(gòu)

在介紹端接之前,先來(lái)了解電路的拓?fù)浣Y(jié)構(gòu)。電路的拓?fù)涫侵鸽娐分懈鱾€(gè)元件之間的連接關(guān)系。常見(jiàn)的電路拓?fù)浣Y(jié)構(gòu)包含點(diǎn)對(duì)點(diǎn)的拓?fù)洹⑿切屯負(fù)洹型拓?fù)洹⒕栈ㄦ溚負(fù)涞龋詈?jiǎn)單的拓?fù)渚褪屈c(diǎn)對(duì)點(diǎn)拓?fù)浣Y(jié)構(gòu)的連接設(shè)計(jì)。點(diǎn)對(duì)點(diǎn)設(shè)計(jì)也是最常見(jiàn)的電路拓?fù)湓O(shè)計(jì),尤其是在高速電路中幾乎都是點(diǎn)對(duì)點(diǎn)的連接設(shè)計(jì)。點(diǎn)對(duì)點(diǎn)雖然簡(jiǎn)單,但是這種拓?fù)湓O(shè)計(jì)限制了帶負(fù)載的數(shù)量。點(diǎn)對(duì)點(diǎn)設(shè)計(jì),由于驅(qū)動(dòng)端的內(nèi)部阻抗與傳輸線的阻抗常常不一樣,很容易造成信號(hào)反射,使信號(hào)失真,造成信號(hào)完整性問(wèn)題。

如圖所示是點(diǎn)對(duì)點(diǎn)的拓?fù)浣Y(jié)構(gòu),由驅(qū)動(dòng)端、傳輸線和接收端組成。

圖23 點(diǎn)對(duì)點(diǎn)無(wú)端接拓?fù)浣Y(jié)構(gòu)——圖來(lái)自硬十

在這個(gè)電路拓?fù)渲校浣邮斩说男盘?hào)波形如圖所示。

圖24 點(diǎn)對(duì)點(diǎn)無(wú)端接拓?fù)湫盘?hào)波形

從波形上可以看出,信號(hào)在高電平時(shí)穩(wěn)定電壓在1.8V,最大值卻達(dá)到2.6V,有800mV;最低值低于0V,達(dá)到了-700mV。這么大的過(guò)沖很容易損毀芯片,即使不損毀,也存在可靠性的問(wèn)題。所以,在設(shè)計(jì)中需要把過(guò)沖降低,盡量保證電壓幅值在電路可接受的范圍內(nèi),如此案例盡量保證滿足信號(hào)幅值在1.8V的±5%內(nèi),這時(shí)就需要通過(guò)端接電阻來(lái)改善信號(hào)質(zhì)量。

2)源端端接

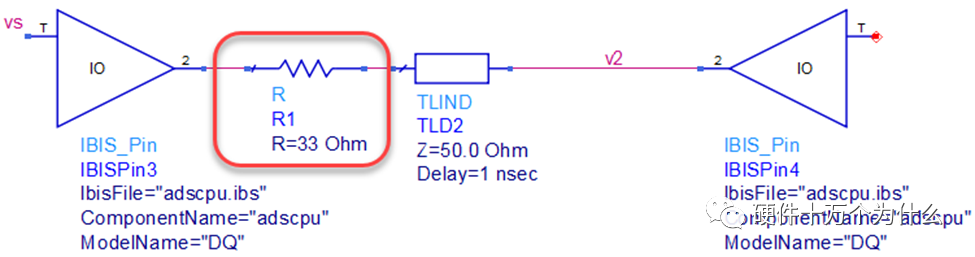

源端端接設(shè)計(jì)也叫做串聯(lián)端接設(shè)計(jì),是一種常用的端接設(shè)計(jì)。端接方式是在芯片端出來(lái)之后添加一顆端接電阻,這顆電阻盡量靠近芯片輸出端,此時(shí)芯片內(nèi)阻和這顆電阻可視為一體。在這種電路結(jié)構(gòu)中,端接多大的電阻是關(guān)鍵。前文我們說(shuō)過(guò),一般源端輸出阻抗比較小,通常在幾十歐姆以內(nèi),如果線路特征阻抗設(shè)計(jì)為50Ω,那么源端串聯(lián)電阻可以設(shè)計(jì)為33Ω,后面根據(jù)實(shí)際信號(hào)波形再細(xì)調(diào)端接電阻的阻值。如果需要更精確的端接電阻值,可以根據(jù)電路的實(shí)際情況進(jìn)行仿真或計(jì)算獲得。串聯(lián)端接的原則是端接電阻盡量靠近源端,源端阻抗Rs與端接電阻R的值相加等于傳輸線的阻抗Z0。在前面的點(diǎn)對(duì)點(diǎn)拓?fù)浣Y(jié)構(gòu)中,加入電阻值為33Ω的端接電阻,其電路拓?fù)浣Y(jié)構(gòu)如圖所示:

圖25 源端端接拓?fù)浣Y(jié)構(gòu)——圖來(lái)自硬十

此時(shí)接收端的信號(hào)波形如圖所示:

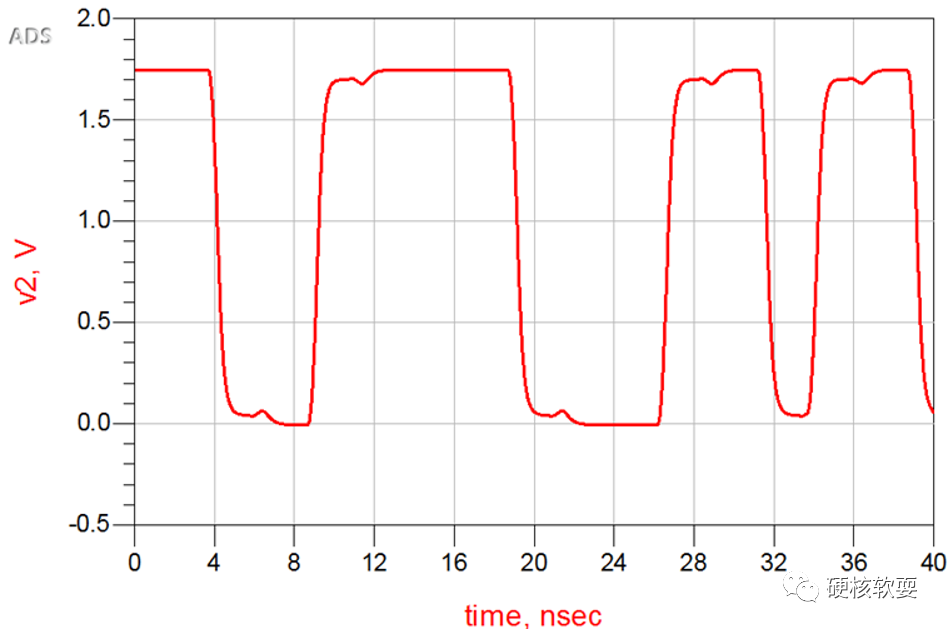

圖26 點(diǎn)對(duì)點(diǎn)源端端接拓?fù)湫盘?hào)波形

使用源端端接后,過(guò)沖基本消除,信號(hào)質(zhì)量得到極大的改善。另一方面,加入端接電阻后,信號(hào)的上升沿變緩,上升沿時(shí)間變長(zhǎng)。

源端端接在電路匹配時(shí),可以使電路匹配匹配得非常好,但是并不是適合每一種電路設(shè)計(jì)。源端端接有自身的一些特性,大致歸納如下:

(1)源端端接十分簡(jiǎn)單,只需要使用一顆電阻即可完成端接。

(2)當(dāng)驅(qū)動(dòng)器器件的輸出阻抗與傳輸線特征阻抗不匹配時(shí),使用源端端接在開始就可以使阻抗匹配;當(dāng)電路不受終端阻抗影響時(shí),十分適合使用源端端接;如果接收端存在發(fā)射現(xiàn)象(如容性反射),就不適合使用源端端接。

(3)適用于單一負(fù)載設(shè)計(jì)時(shí)的端接。

(4)當(dāng)電路信號(hào)頻率比較高,或者信號(hào)上升時(shí)間比較短(特別是高頻時(shí)鐘信號(hào)),不適合使用源端端接。因?yàn)榧尤攵私与娮韬螅瑫?huì)使電路的上升時(shí)間變長(zhǎng)(即RC時(shí)間常數(shù)變大)。

(5)合適的源端端接可以減少電磁干擾(EMI)輻射(前文說(shuō)過(guò),阻抗不連續(xù)時(shí),會(huì)產(chǎn)生反射波,反射的能量有部分變成電磁波散發(fā)出去)。

細(xì)心的同學(xué)會(huì)發(fā)現(xiàn),源端端接拓?fù)涞哪P停邮斩说淖杩挂廊豢梢钥醋鳠o(wú)窮大(即信號(hào)到達(dá)接收端時(shí)無(wú)處釋放),則信號(hào)達(dá)到接收端時(shí)會(huì)產(chǎn)生全反射,但由于源端阻抗+端接電阻=傳輸線阻抗,所以初始時(shí)刻在傳輸線上的電壓為信號(hào)電壓的一半,根據(jù)反彈圖可知,信號(hào)達(dá)到接收端并產(chǎn)生全反射之后,在接收端的電壓即為信號(hào)電壓,所以源端端接拓?fù)鋵?shí)際上是利用了信號(hào)的一次反射。

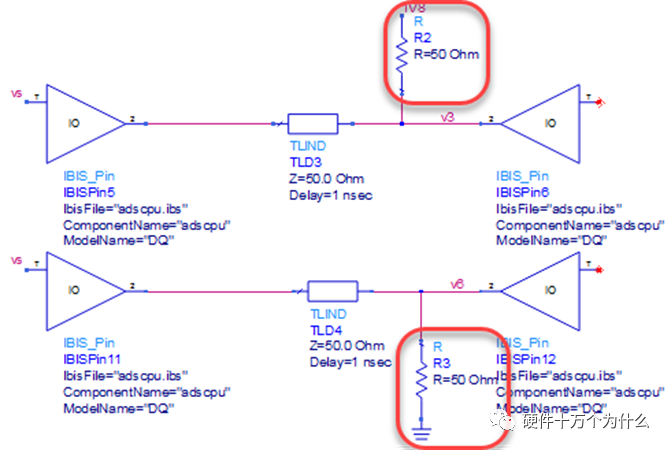

3)并聯(lián)端接

并聯(lián)端接即把端接電阻并聯(lián)在線路中,一般把端接電阻在靠近信號(hào)接收端的位置,并聯(lián)端接分為上拉電阻并聯(lián)端接和下拉電阻并聯(lián)端接。并聯(lián)端接拓?fù)浣Y(jié)構(gòu)如圖所示:

圖27 并聯(lián)端接拓?fù)浣Y(jié)構(gòu)——圖來(lái)自硬十

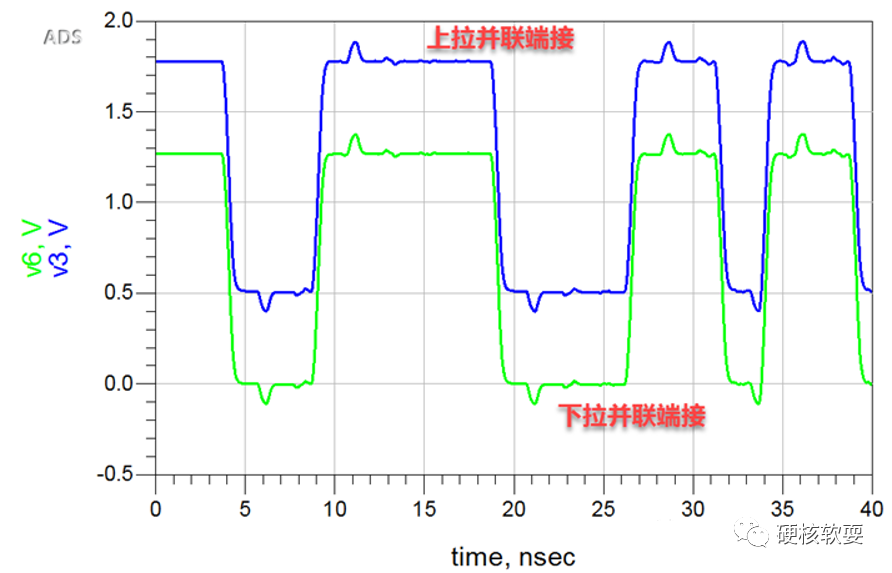

并聯(lián)端接拓?fù)浣Y(jié)構(gòu)中,端接電阻值R0與傳輸線的阻抗一致,接收端的信號(hào)波形如圖所示:

圖28 并聯(lián)端接拓?fù)湫盘?hào)波形

從波形上看,過(guò)沖基本被消除。上拉并聯(lián)端接的波形低電平有很明顯的上移,下拉并聯(lián)端接的波形高電平有很明顯的下移。無(wú)論是上拉并聯(lián)端接還是下拉并聯(lián)端接,信號(hào)波形的峰峰值都比使用源端端接的峰峰值要小一些。

并聯(lián)端接放在接收端,能很好地消除反射,使用的元件也只是電阻。

從電路結(jié)構(gòu)可以看出,即使電路處于靜態(tài),端接電阻也會(huì)消耗電流,所以驅(qū)動(dòng)電流需求比較大,很多時(shí)候驅(qū)動(dòng)端無(wú)法滿足并聯(lián)端接的設(shè)計(jì),特別是在多負(fù)載下,驅(qū)動(dòng)端更難滿足并聯(lián)端接需要消耗的電流。所以,一般并聯(lián)端接不用于TTL和CMOS電路。同時(shí),因?yàn)榉当唤档停娐返脑肼暼菹抟脖唤档土恕?/p>

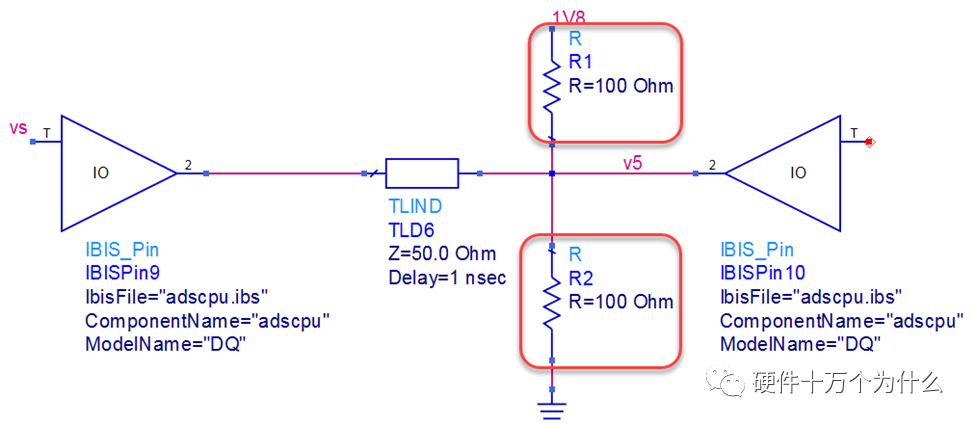

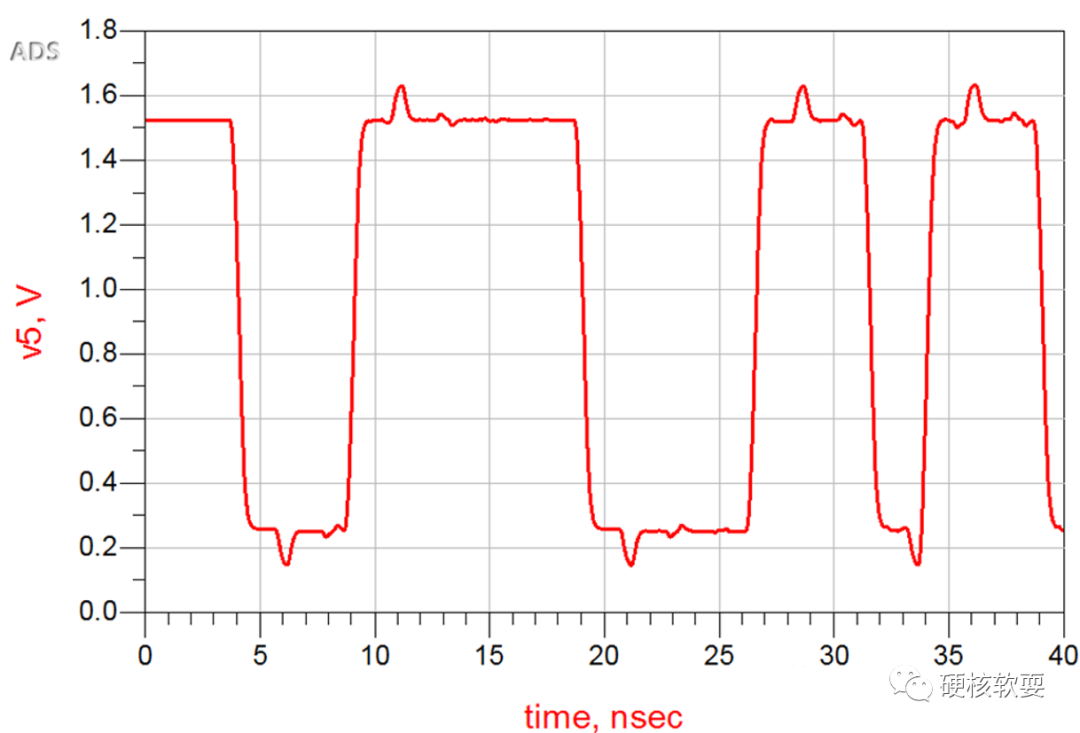

4)戴維寧端接

戴維寧端接就是使用兩顆電阻組成分壓電路,即使用上拉電阻R1和下拉電阻R2構(gòu)成端接,通過(guò)R1和R2吸收反射能量。戴維寧端接的等效電阻(R1||R2)必須等于走線的特征阻抗。戴維寧端接拓?fù)浣Y(jié)構(gòu)如圖所示:

圖29 戴維寧端接拓?fù)浣Y(jié)構(gòu)——圖來(lái)自硬十

使用戴維寧端接后,接收端的信號(hào)波形如圖所示:

圖30 戴維寧端接拓?fù)湫盘?hào)波形

從波形上看,戴維寧端接匹配的效果也很好,基本能消除過(guò)沖的影響。戴維寧端接可以看成上拉并聯(lián)端接和下拉并聯(lián)端接的合體,前者信號(hào)波形的低電平等于后兩者信號(hào)波形低電平的平均值,前者信號(hào)波形的高電平等于后兩者信號(hào)波形高電平的平均值,波形峰峰值相等。因?yàn)槭褂昧藘深w電阻,所以戴維寧端接比并聯(lián)端接的直流功耗少,但由于也一直存在直流功耗,所以對(duì)電源的功率要求比較多,對(duì)源端的驅(qū)動(dòng)能力要求也高。同樣地,因?yàn)樾盘?hào)波形的幅度降低了,所以噪聲容限也被降低。同時(shí),因?yàn)槭褂昧藘深w分壓電阻,電阻的選型也相對(duì)更麻煩些,使很多電路設(shè)計(jì)工程師在使用這類端接時(shí)總是非常謹(jǐn)慎。在實(shí)際應(yīng)用中,DDR2和DDR3的數(shù)據(jù)和數(shù)據(jù)選通信號(hào)網(wǎng)絡(luò)的ODT端接電路就采用了戴維寧端接。

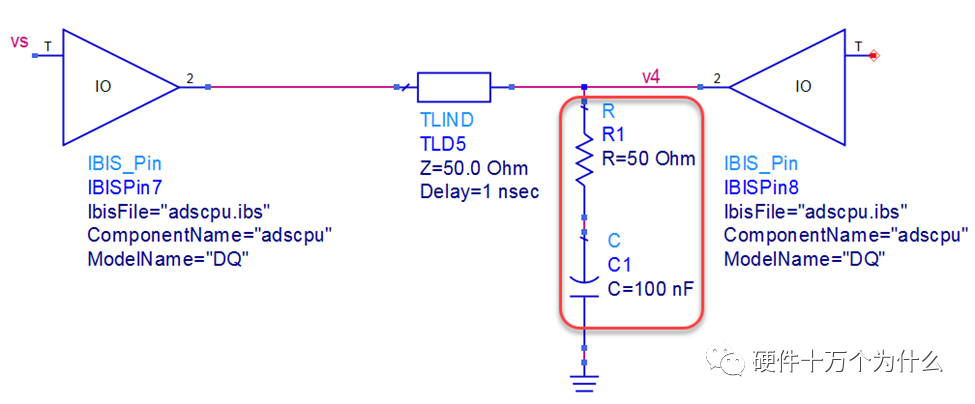

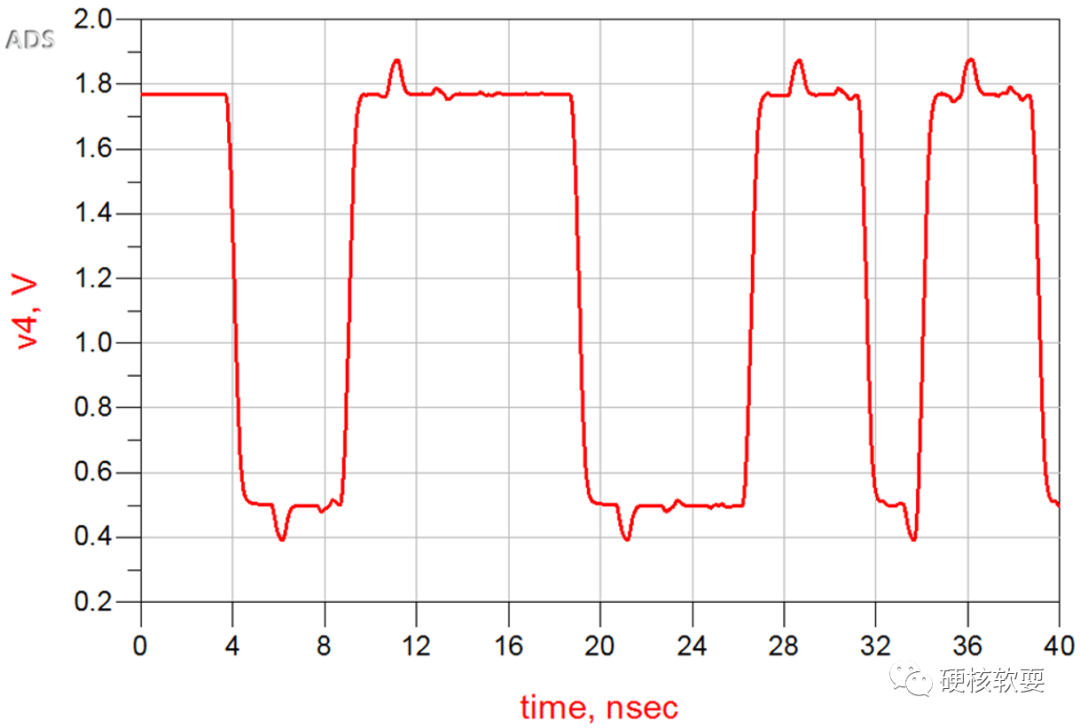

5)RC端接

RC端接在并聯(lián)下拉端接的電阻下面串聯(lián)一顆電容到地,即RC端接是由一顆電阻和一顆電容組成的端接。RC端接也可以看作是一種并聯(lián)端接。電阻值的大小等于傳輸線的阻抗,電容值通常取值比較小。RC端接拓?fù)浣Y(jié)構(gòu)如圖所示:

圖31 戴維寧端接拓?fù)浣Y(jié)構(gòu)——圖來(lái)自硬十

使用RC端接后,接收端的信號(hào)波形如圖所示:

圖32 RC端接拓?fù)湫盘?hào)波形

從波形上看,RC端接基本能消除過(guò)沖的影響。RC端接信號(hào)接收端的波形和上拉并聯(lián)信號(hào)接收端的波形相似,在信號(hào)為高電平時(shí),C被充電,充滿電后可以看作直流電源。RC端接能很好地消除源端帶來(lái)的反射影響,但是也可能導(dǎo)致新的反射。由于RC端接拓?fù)渲杏须娙荽嬖冢噪娐返撵o態(tài)直流功耗非常小。

同樣地,信號(hào)波形的低電平提升了很多,所以RC端接后電路的噪聲容限被降低。由于引入了RC延時(shí),所以RC端接拓?fù)渲行盘?hào)波形邊沿也明顯變緩慢,其變化程度與RC端接的時(shí)間常數(shù)τ有關(guān)(τ=RC)。所以,RC端接并不適合十分高速的信號(hào)和時(shí)鐘電路端接。同時(shí),RC端接需要使用電阻和電容兩顆元件。

上面分析的幾種端接類型基本都能達(dá)到電路匹配的效果,使信號(hào)在傳輸過(guò)程中不失真,滿足信號(hào)完整性的設(shè)計(jì)要求。從電氣性能的角度看,端接匹配不僅可以改善信號(hào)質(zhì)量,還可以用于控制信號(hào)邊沿變化的速率,即控制信號(hào)的上升時(shí)間,也可以改變信號(hào)電平的類型,起到轉(zhuǎn)換的作用。電子產(chǎn)品設(shè)計(jì)是一個(gè)系統(tǒng)工程,涉及方方面面,其中包括信號(hào)完整性和電源完整性,也包括電磁兼容性、電路可靠性、可加工性、成本等,在使用端接來(lái)解決反射問(wèn)題時(shí),也要考慮這些方面的因素。在實(shí)際應(yīng)用中,需要根據(jù)項(xiàng)目工程的應(yīng)用選擇端接類型。

四、高低頻阻抗匹配共同點(diǎn)

前文說(shuō)過(guò),阻抗匹配是指信號(hào)源或者傳輸線跟負(fù)載之間的一種合適的搭配方式。怎么才算合適則取決于我們的設(shè)計(jì)目的。而高低頻電路中,阻抗匹配的共同點(diǎn)有以下兩個(gè)點(diǎn):

(1)功率最大化

在低頻電路中,我們通過(guò)阻抗匹配來(lái)獲取最大的輸出功率。而在高頻電路中,阻抗不匹配會(huì)導(dǎo)致反射,反射也會(huì)導(dǎo)致?lián)p耗。我們總是希望有用的射頻信號(hào)能夠無(wú)衰減或者小衰減的傳輸?shù)截?fù)載,如果阻抗不匹配的話,反映到系統(tǒng)的就是該器件的回波損耗差。回波損耗也是損耗。這個(gè)反射回去的射頻信號(hào),會(huì)對(duì)系統(tǒng)造成很大的影響,甚至燒壞某些器件。阻抗匹配就是為了電磁波能夠更好的傳播,同時(shí)也是讓輸出功率最大化。

(2)保證信號(hào)質(zhì)量

在低頻電路中,如果輸出功率太小,則容易受到外界的干擾,嚴(yán)重影響信號(hào)質(zhì)量,特別是傳感器類的微弱信號(hào),如果阻抗不匹配,更容易受到干擾,產(chǎn)生失真。

而在高頻電路中,如果阻抗不匹配,就會(huì)產(chǎn)生反射,信號(hào)出現(xiàn)過(guò)沖(Overshoot)、振鈴(Ringing)、邊沿遲緩(回勾現(xiàn)象),造成嚴(yán)重的信號(hào)完整性問(wèn)題。阻抗匹配則是保證信號(hào)質(zhì)量的有效手段。

五、結(jié)語(yǔ)

本篇從阻抗匹配的概念定義開始,闡述了高低頻下阻抗匹配的意義、匹配方法以及阻抗匹配對(duì)于高低頻電路的共同作用,其中夾帶著高低頻電路的相關(guān)知識(shí)點(diǎn),旨在讓讀者對(duì)阻抗匹配有足夠的了解以及遇到相關(guān)的信號(hào)完整性問(wèn)題時(shí)能找到有效的對(duì)策。對(duì)于阻抗匹配,本文只是拋磚引玉,遠(yuǎn)遠(yuǎn)沒(méi)有結(jié)束,特別是在本文沒(méi)有提及的射頻電路中,阻抗匹配還有很多種方式,其中寬帶阻抗匹配更有利于整個(gè)系統(tǒng)設(shè)計(jì),而最為高級(jí)的一個(gè)阻抗匹配方式是濾波器的設(shè)計(jì),限于篇章和知識(shí)儲(chǔ)備,本文不一一展開,對(duì)此有興趣的讀者可自行查閱。

-

阻抗匹配

+關(guān)注

關(guān)注

14文章

348瀏覽量

30753 -

高速電路

+關(guān)注

關(guān)注

8文章

157瀏覽量

24226 -

振鈴

+關(guān)注

關(guān)注

0文章

27瀏覽量

17771 -

輸入阻抗

+關(guān)注

關(guān)注

0文章

124瀏覽量

15657 -

輸出阻抗

+關(guān)注

關(guān)注

1文章

102瀏覽量

12316

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電子大神傳授的經(jīng)驗(yàn):阻抗匹配原理及負(fù)載阻抗匹配

什么是阻抗匹配原理?什么是負(fù)載阻抗匹配?

如何在stm32外部接入阻抗匹配電路?

分立元件組成的阻抗匹配電路

阻抗匹配電路的原理及其應(yīng)用介紹

一文看懂阻抗匹配電路原理與應(yīng)用

阻抗匹配的基本原理和負(fù)載阻抗匹配的方法說(shuō)明

PCB設(shè)計(jì)阻抗匹配問(wèn)題的解決辦法

怎樣理解阻抗匹配?

高低頻的阻抗匹配電路概念及要點(diǎn) 高速電路的振鈴產(chǎn)生原因及解決辦法

高低頻的阻抗匹配電路概念及要點(diǎn) 高速電路的振鈴產(chǎn)生原因及解決辦法

評(píng)論