隨著能源效率和環保的日益重要,人們對開關電源待機效率期望越來越高,客戶要求電源制造商提供的電源產品能滿足BLUEANGEL、ENERGYSTAR、ENERGY2000等綠色能源標準,有滿載空載等幾個測試點都有很高的要求。而目前大多數開關電源由額定負載轉入輕載和待機狀態時,電源效率急劇下降,待機效率不能滿足要求。這就給電源設計工程師們提出了新的挑戰。

二、開關電源功耗分析

開關穩壓電源從原理上是由主電路、控制電路、檢測電路、輔助電源四大部分組成,其中主電路是指從交流電網輸入、直流輸出的全過程,包括:輸入濾波器、整流與濾波、逆變、輸出整流與濾波。它們的作用分別是首先將電網存在的雜波過濾,同時也阻礙本機產生的雜波反饋到公共電網。其次是將電網交流電源直接整流為較平滑的直流電,以供下一級變換。再將整流后的直流電變為高頻交流電,這是高頻開關電源的核心部分,頻率越高,體積、重量與輸出功率之比越小。

最后根據負載需要,提供穩定可靠的直流電源。控制電路的作用一方面從輸出端取樣,經與設定標準進行比較,然后去控制逆變器,改變其頻率或脈寬,達到輸出穩定,另一方面,根據測試電路提供的數據,經保護電路鑒別,提供控制電路對整機進行各種保護措施。檢測電路除了提供保護電路中正在運行中各種參數外,還提供各種顯示儀表數據。輔助電源提供所有單一電路的不同要求電源。

據開關電源的內部原理,要減小開關電源待機損耗,提高待機效率,首先要分析開關電源損耗的構成。以反激式電源為例,其工作損耗主要表現為:MOSFET導通損耗,MOSFET寄生電容損耗,開關交疊損耗,PWM控制器及其啟動電阻損耗,輸出整流管損耗,箝位保護電路損耗,反饋電路損耗等。其中前三個損耗與頻率成正比關系,即與單位時間內器件開關次數成正比。在待機狀態,主電路電流較小,MOSFET導通時間ton很小,電路工作在DCM模式,故相關的導通損耗,次級整流管損耗等較小,此時損耗主要由寄生電容損耗和開關交疊損耗和啟動電阻損耗構成。

三、提高待機效率的方法

根據損耗分析可知,切斷啟動電阻,降低開關頻率,減小開關次數可減小待機損耗,提高待機效率。具體的方法有:降低時鐘頻率;由高頻工作模式切換至低頻工作模式,如準諧振模式(QuasiResonant,QR)切換至脈寬調(PulseWidthModulation,PWM),脈寬調制切換至脈沖頻率調制(PulseFrequencyModulation,PFM);可控脈沖模(BurstMode)

(一)切斷啟動電阻

對于反激式電源,啟動后控制芯片由輔助繞組供電,啟動電阻上壓降為300V左右。設啟動電阻取值為47kΩ,消耗功率將近2W。要改善待機效率,必須在啟動后將該電阻通道切斷。如TOPSWITCH,ICE2DS02G內部設有專門的啟動電路,可在啟動后關閉該電阻。若控制器沒有專門啟動電路,也可在啟動電阻串接電容,其啟動后的損耗可逐漸下降至零。缺點是電源不能自重啟,只有斷開輸入電壓,使電容放電后才能再次啟動電路。

(二)降低時鐘頻率

時鐘頻率可平滑下降或突降。平滑下降就是當反饋量超過某一閾值,通過特定模塊,實現時鐘頻率的線性下降。現在市面上有非常多的電源管理芯片內置了這樣的模塊,能根據負載大小調節頻率。

(三)切換工作模式

1.QR→PWM

對于工作在高頻工作模式的開關電源,在待機時切換至低頻工作模式可減小待機損耗。例如,對于準諧振式開關電源(工作頻率為幾百kHz到幾MHz),可在待機時切換至低頻的脈寬調制控制模式PWM(幾十kHz)。

2.PWM→PFM

對于額定功率時工作在PWM模式的開關電源,也可以通過切換至PFM模式提高待機效率,即固定開通時間,調節關斷時間,負載越低,關斷時間越長,工作頻率也越低。顯而易見,在輕載時采用PFM模式的電源效率明顯大于采用PWM模式時的效率,且負載越低,PFM效率優勢越明顯。將待機信號加在其PW/引腳上,在額定負載條件下,該引腳為高電平,電路工作在PWM模式,當負載低于某個閾值時,該引腳被拉為低電平,電路工作在PFM模式。實現PWM和PFM的切換,也就提高了輕載和待機狀態時的電源效率。

通過降低時鐘頻率和切換工作模式實現降低待機工作頻率,提高待機效率,可保持控制器一直在運作,在整個負載范圍中,輸出都能被妥善的調節。即使負載從零激增至滿負載的情況下,能夠快速反應,反之亦然。輸出電壓降和過沖值都保持在允許范圍內。

(四)可控脈沖模式(BurstMode)

可控脈沖模式,也可稱為跳周期控制模式(SkipCycleMode)是指當處于輕載或待機條件時,由周期比PWM控制器時鐘周期大的信號控制電路某一環節,使得PWM的輸出脈沖周期性的有效或失效。這樣即可實現恒定頻率下通過減小開關次數,增大占空比來提高輕載和待機的效率。該信號可以加在反饋通道,PWM信號輸出通道,PWM芯片的使能引腳。

這種芯片在工作時,當反饋檢測腳FB的電壓低于一個閥值(如1.2V)(該值可編程)時,跳周期比較器控制Q觸發器,使輸出關閉若干時鐘周期,也即跳過若干個周期,負載越輕,跳過的周期也越多。為免音頻噪音,只有在峰值電流降至某個設定值時,跳周期模式才有效。

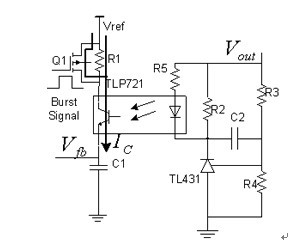

而有些芯片則是通過控制內部驅動器實現可控脈沖模式,即將腳的反饋電壓與0.6V/0.5V遲滯比較器比較,由比較結果控制門出。我們可根據此原理用分立元件實現普通芯片的BurstMode功能。控制反饋通道是實現一般PWM控制器的可控脈沖模式一。

另外對于有使能腳的PWM控制器,用可控脈沖信號控制使能腳使控制芯片有效或失效,也可以實現Burs式的遲滯比較器產生。

(五)存在的問題

以上介紹的切斷啟動電阻、降低開關頻率,減小開關次數等方法均可減小待機損耗,提高待機效率,但也帶來一些問題 ,首先是頻率降低導致輸出電壓紋波的增加,其次如果頻率降至20kHz以內,可能有音頻噪音。

而在BurstMode的OFF時期內,如果負載激增,輸出電壓會大大降低,如果輸出電容不夠大,電壓甚至可能降低至零。如果增大輸出電容,以減小輸出電壓紋波,則會導致成本增加,并會影響系統動態性能。因此在采取相關措施來減小開關電源待機損耗,提高待機效率的同時,也必須綜合考慮相關因素。

四、提高電源整機效率的一般方法

以下是提高開關電源效率的電路和系統方法:

(1)ZVS(零電壓開關)、ZCS(零電流開關)等利用諧振開關來降低開關損耗的方法。

(2)運用以有源箝位電路為代表的邊緣諧振(Edge Resonance)來降低開關損耗。

(3)通過延展開關元件的導通時間以抑制峰值電流的方法來減少固定損耗。

(4)在低電壓大電流的場合通過改善同步整流電路的方法來減少固定損耗。

(5)利用轉換器的并聯結構來減少固定損耗。

其中,第一種方法對于降低開關損耗極為有效,但問題是因峰值電流和峰值電壓所導致的固定損耗將會增加。第二種方法是為解決該問題而開發的有源緩沖器(Active Snubber),是一種極為實用的ZVS方式;但是,由輕負載條件下的無功電流所引發的效率下降問題卻是其一大缺陷。第三種方法中,采用抽頭電感器(Tap Inductor)的方式是比較有效的,它能夠應付由漏感所引起的浪涌現象。

關于第四種方法,兩段式結構是實現同步整流電路高效工作的方法之一,它采用接近0.5的固定時間比率(Time Ratio),并由前段的轉換器來進行輸出電壓控制。它一反“兩段式結構將導致效率下降”這一傳統思維模式,在低電壓大電流的場合非常有效。至于第五種方法,既可將整個轉換器電路進行并聯,也可像電流倍增器(Current Doubler)那樣部分采用并聯結構。下面將對利用轉換器的并聯操作所實現的效率提升情況進行簡要闡述。

-

開關電源

+關注

關注

6448文章

8289瀏覽量

480722 -

保護電路

+關注

關注

45文章

886瀏覽量

101581 -

控制電路

+關注

關注

82文章

1704瀏覽量

135793

原文標題:開關電源功耗分析、提高待機效率的方法

文章出處:【微信號:電子技術控,微信公眾號:電子技術控】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

怎么提高開關電源的待機效率

開關電源功耗分析和提高待機效率的方法

開關電源功耗分析、提高待機效率的方法

開關電源功耗分析、提高待機效率的方法

評論