盡早確定芯片性能規格可以縮短工藝成熟所需的時間,并降低制造中的總體測試成本。

在半導體下線時測試半導體的性能和功率流程的進步,扭轉了在發貨前評估芯片的長期趨勢。雖然這聽起來很簡單,但這是一個艱巨的挑戰,如果成功,將對整個設計到制造流程產生廣泛的影響。

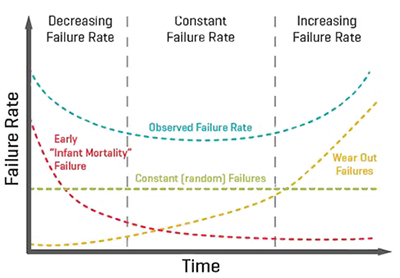

制造商通常在發貨前對芯片進行分級。并非所有芯片都是一樣的,而且這種差距通常會隨著新制造工藝的引入而擴大。減少誤差和推動流程成熟需要時間。過去,晶圓廠會在新工藝中考慮到這一點。但是,由于添加到先進芯片中的新功能數量已經將它們推到了標線的大小之外。因此,盡早識別任何潛在的缺陷或不規則性至關重要,它們可能會影響這些日益復雜和昂貴的芯片的生命周期。

同時,這些數據可用于微調新工藝,以更快地提高產量。它還可用于提高測試效率,而測試效率一直受到晶圓廠和最終客戶的壓力。過去,測試成本被牢牢固定在芯片制造總成本的2%至2.5%。這些數字一直在穩步增長,原因如下: 芯片變得越來越復雜,在先進節點上測試它們也更加困難。它們需要更多時間在整個流程的多個插入點進行測試、檢查和計量。

另外,測試探針需要定制,每個新設計的測試需要更多的探針,這進一步增加了成本。 對可靠性的需求,特別是在任務關鍵型和安全關鍵型應用中,需要更高的測試覆蓋率。 測試設備本身的復雜性不斷增加,需要更多的設備來完成工作。有更多的傳感器、人工智能/機器學習來分析這些傳感器生成的數據,以及更多的整體測試,因為每個芯片有更多的功能,每個封裝有更多的芯片。

“我們正在研究的是如何優化整個價值鏈,特別是當你有更復雜的問題需要解決2.5D和3D設備,異構集成在一個封裝中,并且你無法訪問該封裝中的所有內容,”愛德萬測試美國應用研究和技術副總裁Ira Leventhal說。“對于 HPC 設備,您會發現測試成本從傳統的收入 2.5% 上升到 3% 或 4%。那么如何才能恢復呢?你不能只是不斷地添加測試。

與其看每一次插入,不如問:“我在這里做什么,如何優化它們?從長遠來看,并行做更多的事情是解決這個問題的唯一途徑。”

更早的數據和更好的反饋可以幫助以其他方式直接或間接地抵消這些成本。

“我們看到從經典的基于性能的分級越來越多地轉向基于應用程序的分級,”Leventhal 說。“過去,設備要簡單得多。它們被映射到非常具體的應用程序中。現在,有了AI芯片,你可能會有很多應用。它們的設備中有許多不同的單元和多個內核,因此將該設備與應用程序的分檔變得比處理器芯片的速度分檔復雜得多。更具預測性的模型將真實地告訴您這些設備可以持續使用多長時間。”

其中大部分內容越來越針對特定領域,這只會增加復雜性。對于一種應用或使用模型來說足夠好的東西在另一種應用或使用模型中可能會非常不同,其中預期壽命可能更長或更短,規格可能更寬松或更嚴格。

NI首席解決方案營銷人員 James Guilmart 表示:“這確實不僅僅是查看參數數據和通過/失敗標準就能夠實現。”“這更多的是關于復雜的動力學和多變量分析,這種獨特的組合已經接近邊緣,當我們查看這些更先進的特定于應用程序的應用時,將需要更多的多變量分析來更精細地對這些芯片進行分類,以了解它們在現場的表現如何。然后,您需要確保這符合該設備的預期用例。”

定制測試過程

所有這些步驟也都需要花錢,無論是因為測試花費更多時間,整個制造過程中插入點更多,還是需要新設備來探測更多芯片并評估結果。

關鍵始終在于插入的目標是什么,”Teradyne 戰略應用軟件解決方案經理 Michelle Evans說道。“根據設備的類別,您可以在一次插入過程中進行中間合并。并且您可以進行條件分支。對于移動應用程序處理器,您可以將它們分到不同的階段。”如今,移動應用處理器就做到了這一點。然而,當你進入醫療領域時,那就是另一種不同的分類。它要么有效并滿足要求,要么不有效。

隨著芯片被組合在一個封裝中,這變得更具挑戰性。引線并不總是暴露的,這就是為什么人們對片上監控的遙測類型數據如此感興趣。首先是挑戰提取必要的數據,然后能夠在整個流程的適當點使用它。

proteanTecs測試和分析副總裁 Alex Burlak 表示:“在測試儀上,您需要正確的信息來幫助您決定和執行分檔策略”。“您分檔所依據的物理測量參數是什么?這就是我們的代理組合的用武之地。您需要從芯片內的多個位置對芯片內的參數數據、晶體管工藝分級、泄漏特征、RC 延遲、實際邏輯路徑的路徑延遲等有精細的可視性。這種方法可以在比現在更早的階段提供準確的性能分級——甚至在晶圓分類時也是如此。這是每個芯片在線完成的。這意味著您現在可以保留模具庫而不是成品庫存。您可以在選擇封裝之前進行分類,您可以根據此數據配對性能相似的芯片。”

僅僅因為芯片/小芯片在集成到封裝中之前通過了測試,并不意味著它們在封裝密封后將保持良好狀態。

“芯片可以單獨測試,但封裝和互連部分從未測試過,但它存在于最終產品中,”Teradyne 的 Evans 說。“第一步是消除嚴重缺陷,然后進入關鍵任務領域。如果它處于最高速度、最高功率或任何使其成為關鍵任務的部件的標準,您首先要對其進行測試。這使您可以創建我所說的“真值表”。您已經創建了一個中間標志,允許您繼續或走流程中的不同路線,所有這些都在一次插入中完成。總會有一些條件分支。”

在系統中進行測試

并非所有內容都必須以最佳性能運行。隨著先進封裝成為前沿設計的標準,一些新方法正在被催生。

“考慮這個問題的傳統方法是,您不想將高速部件和低速部件放入兩芯片模塊中,因為您會受到最差部件的限制,”高級工程師 Mark Laird 說道。Synopsys的資深應用工程師。“但我也看到了一個更有趣的用例,他們關心總功率。因此,您試圖平衡同一模塊上的高功率和低功率,都是一種不同的優化。”

這里的轉變是性能和功耗的系統級視圖,而不是單個芯片。我們正在使用 Vmin數據集,但不僅僅是預測ATE 上的V min 。我們還在系統中進行預測,因為ATE 與 SLT 測試儀上的Vmin可能會有相當大的變化。有時 ATE 的 V min 值會低于SLT,但我也看到過 V min 值更高在 SLT 上,因此它取決于產品。您可以為臺式機和服務器使用相同的部件,但是它們將具有不同的封裝,這兩種產品的引腳排列不同。您希望能夠預測晶圓分類時的最終分級,然后將該數據轉發給我們說,我認為這不僅會是服務器部件,而且是服務器部件的分類——例如,高速服務器部件,萊爾德說。

使用更好的數據實現自動化

所有這一切的基礎是向更好的數據轉變,以及利用這些數據的更好方法。EDA 供應商一直在與代工廠和設備制造商合作,統一從概念到現場的數據。這種端到端數據流現在開始整合來自各個工藝步驟的數據,基本上將 DFT 和其他工藝從實驗室轉移到晶圓廠再到現場。從測試的角度來看,最大的轉變是從一開始就制定良好的測試計劃,因為許多前沿設計都是高度定制的且極其復雜。例如,任何元件中的時序不匹配都可能對封裝中其他元件的性能產生廣泛影響。然而,一旦解決了所有問題并設置了參數,那么測試過程的其余大部分都可以自動化。

NI 的 Guilmart 表示:“盡管查看這些變量時很復雜,但一旦理解了它,添加了歷史背景,并知道數據指向什么,那么它就會變得自動化。”“關鍵推動因素之一是數據模型。我們如何獲取這些數據以及如何存儲它?我們的數據模式的結構是什么?我們確實優先考慮產品的生命周期。對于每個芯片,您希望將所有數據流及其經歷的數據和測試結果關聯起來。您擁有它的整個生產過程數據。當我們獲得最終測試數據并開始分析它并尋找偏差時,我們可以將所有這些放在一起并開始對它們進行聚類并開始找出導致異常的原因。”

反過來,這些數據與片上/封裝內數據集成,以提供芯片在晶圓廠、封裝內部以及最終在現場的行為的可見性。其中一些與proteanTecs的Burlak所謂的“邊緣庫”有關,后者是可以集成到測試程序中的軟件。所有的建模和分析都是在分析平臺中完成的。我們的邊緣庫部署在ATE上,處理來自代理的所有信息和其他客戶數據,運行模型,并在芯片仍在測試儀上時預測什么是正確的芯片。

結論

在制造過程中盡早進行分檔是提高可靠性和降低測試成本的重要一步。但這只是可靠性等式的一個方面,其中還包括計量和檢測。評估芯片在特定應用和易于理解的用例中隨時間推移的行為變化,大大增加了成功實施和可靠性能的機會。

Advantest 的 Leventhal 說,“現在,我們正在進一步預測影響可靠性的因素。這不是一個容易解決的問題。你需要預先做好基礎工作,收集這些數據并將其整合在一起,然后能夠利用這些信息為你帶來優勢并對其進行預測。”

對于設備制造商和芯片公司來說,這帶來了許多新的機遇。隨著各地的復雜性不斷增加,理解交互和正確解釋大量數據的能力正在迫使更多的自動化和設備升級。對于芯片制造商以及整個制造和封裝生態系統來說,成功的數據集成可以為顯著提高設備質量、穩定多個流程的成本以及減少現場故障。

審核編輯:劉清

-

傳感器

+關注

關注

2548文章

50698瀏覽量

752048 -

處理器

+關注

關注

68文章

19169瀏覽量

229158 -

半導體

+關注

關注

334文章

27026瀏覽量

216365 -

芯片封裝

+關注

關注

11文章

479瀏覽量

30567 -

HPC

+關注

關注

0文章

311瀏覽量

23686

原文標題:?定制IC測試以提高良率和可靠性

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

KLA發布全新汽車產品組合以提高芯片良率及可靠性

?定制IC測試以提高良率和可靠性嗎?

?定制IC測試以提高良率和可靠性嗎?

評論