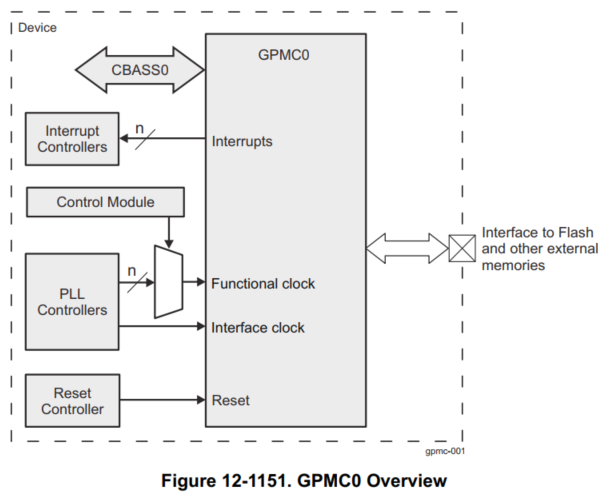

GPMC并口簡介

GPMC(General Purpose Memory Controller)是TI處理器特有的通用存儲器控制器接口,支持8/16bit數據位寬,支持128MB訪問空間,最高時鐘速率133MHz。 GPMC是AM62x、AM64x、AM437x、AM335x、AM57x等處理器專用于與外部存儲器設備的接口,如:

(1)FPGA器件

(2)ADC器件

(3)SRAM內存

(4)NOR/NAND閃存

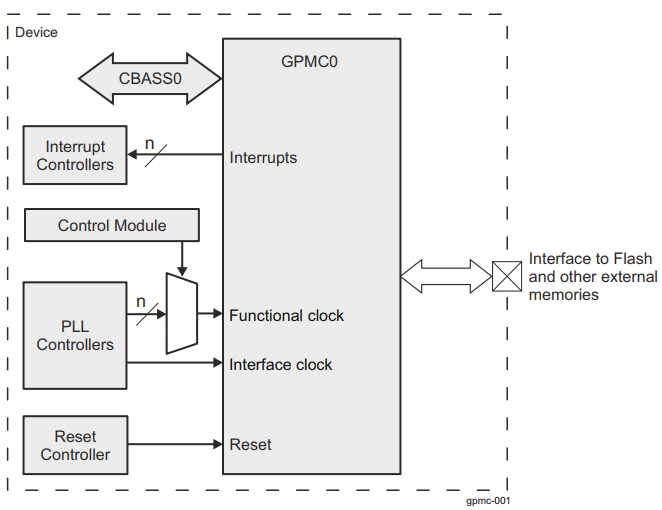

圖 1 GPMC功能框圖

GPMC并口3大特點

(1)小數據-低時延

在工業自動化控制領域中,如工業PLC、驅控一體控制器、運動控制器、CNC數控主板、繼電保護設備、小電流接地選線等,極其注重精確性與快速性,GPMC并口“小數據-低時延”的特點顯得格外耀眼,能夠很好地提高數據傳輸效率,降低傳輸成本。

(2)大數據-高帶寬

大數據時代對能源電力領域的數據量傳輸、數據處理等方面提出了更高的要求。GPMC提供了最大的靈活性,以支持四個可配置片選中不同的時序參數和位寬配置。可根據外部設備的特點,使用最佳的片選設置。可通過配置GPMC接口的時序參數和不同工作模式,最大速率可超過100MB/s。因此,GPMC“大數據-高帶寬”的特點在能源電力領域扮演著重要角色。

(3)低成本-低功耗

“低成本、低功耗、高性能”是如今智能設備發展趨勢,GPMC并口相對于PCIe串行接口,成本更低、功耗更低。兩者都為常用的通信接口,均可滿足高速通信要求,但在與FPGA通信的時候,用戶往往更喜歡選用GPMC并口,因為:

1、使用低成本FPGA即可實現高速通信,而具備PCIe接口的FPGA成本則成倍增長。

2、具備PCIe接口的FPGA功耗往往較大,而低成本FPGA功耗較小。一般而言,低功耗器件的使用壽命也將更長。

AM62x基于GPMC的ARM+FPGA通信方案

(立即點擊,1分鐘了解AM62x最新工業處理器平臺)

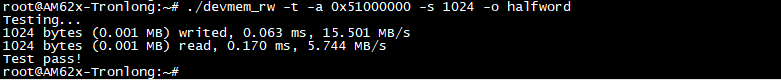

基于CPU直接訪問方式

以AM62x為例,通過GPMC接口與FPGA連接,采用CPU直接訪問方式讀取FPGA端的數據,寫速度可達15.501MB/s,讀速度可達5.744MB/s。

此方式適合“小數據-低時延”場合。

圖 2 CPU直接訪問方式測試結果

程序流程說明:

(1)ARM端通過GPMC總線將數據寫入FPGA BRAM;

(2)ARM端通過GPMC總線從FPGA BRAM讀取數據;

(3)判斷寫入與讀取數據的正確性,并計算讀寫速率。

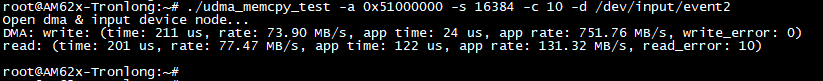

基于UDMA訪問方式

以AM62x為例,通過GPMC接口與FPGA連接,采用UDMA的方式讀取FPGA端的數據,寫速度可達73.90MB/s,讀速度可達77.47MB/s,實際上通過配置GPMC接口的時序參數和不同工作模式,最大速率可超過100MB/s。

此方式適合“大數據-高帶寬”場合。

圖 3 UDMA訪問方式測試結果

備注:由于測試受線材限制影響,因此測得誤碼率會過高。

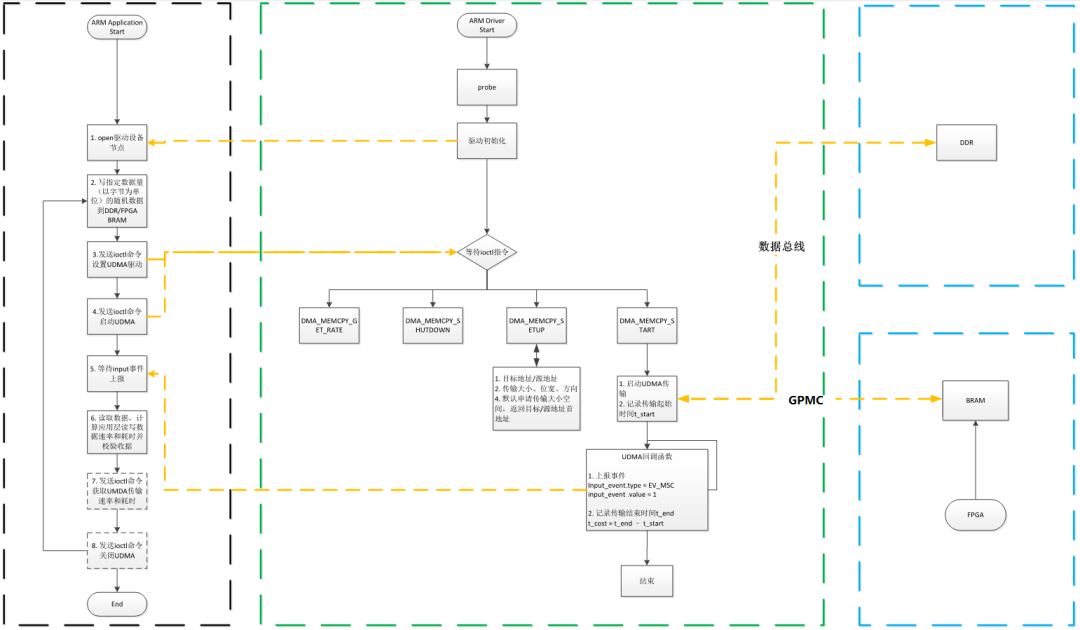

程序流程說明

ARM端:

(1) 采用UDMA方式;

(2)將數據寫入至dma_memcpy驅動申請的連續內存空間(位于DDR);

(3)配置UDMA,如源地址、目標地址、傳輸的數據大小等;

(4)寫操作:通過ioctl函數啟動UDMA,通過GPMC總線將數據搬運至FPGA BRAM;

(5)程序接收驅動上報input事件后,將通過ioctl函數獲取UDMA搬運數據耗時,并計算UDMA傳輸速率(即寫速率);

(6)讀操作:通過ioctl函數啟動UDMA,通過GPMC總線將FPGA BRAM中的數據搬運至dma_memcpy驅動申請的連續內存空間;

(7)程序接收驅動上報input事件后,將數據從內核空間讀取至用戶空間,然后校驗數據,同時通過ioctl函數獲取UDMA搬運數據耗時,并計算UDMA傳輸速率(即讀速率)。

FPGA端:

(1)根據ARM端GPMC時序解析數據,對FPGA內部BRAM資源進行訪問。BRAM的地址位寬為10bit,數據位寬為16bit,內存空間大小為2KByte(1024 x 16bit)。

圖 4 程序流程圖

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19159瀏覽量

229112 -

FPGA

+關注

關注

1626文章

21665瀏覽量

601802 -

ARM

+關注

關注

134文章

9045瀏覽量

366799 -

接口

+關注

關注

33文章

8496瀏覽量

150831 -

adc

+關注

關注

98文章

6430瀏覽量

544074

原文標題:分享ARM+FPGA低成本通信方案!輕松實現GPMC并口“小數據-低時延,大數據-高帶寬”

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

GPMC并口多通道AD采集案例,基于TI AM62x四核處理器平臺!

AM62x相比AM335x,到底升級了什么?

AM62x GPMC并口如何實現“小數據-低時延,大數據-高帶寬”—ARM+FPGA低成本通信方案

沒搶到?米爾AM62x開發板限量5折又來了

GPMC并口多通道AD采集案例,基于TI AM62x四核處理器平臺!

AM62x基于GPMC的ARM+FPGA通信方案

AM62x基于GPMC的ARM+FPGA通信方案

評論