主要介紹幾種邏輯電路的高速特性包括 ITL 邏輯電路、 CMOS 邏輯電路、 ECL 邏輯電0路,和 LVDS 器件的基本結構、 工作原理和特點,以及邏輯門電路的使用規則 。

1 高速TTL電路

由于TTL電路的基本組成單元為三極管,先復習下三極管的一些知識。

1.1 三極管的動態開關特性

晶體三極管在飽和與截止兩種狀態轉換過程中具有的特性稱為三極管的 開關特性 。三極管的內部也存在著電荷的建立與消失過程。

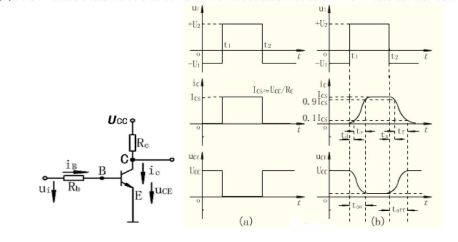

飽和與截止兩種狀態的轉換也需要一定的時間才能完成。假如下圖所示電路的輸入端輸入一個理想的矩形波電壓,在想情況下, iC 和 UCE 的波形應該如圖 (a)所示 。

但實際轉換過程中 iC 和 UCE 的波形如圖(b)所示 , 無論從截止轉向導通還是從導通轉向截止都存在一個逐漸變化的過程。

開通時間: 三極管從截止狀態到飽和狀態所需要的時間。

三極管處于截止狀態時,發射結反偏,空間電荷區比較寬。當輸入信號Ui 由-U1 跳變到+U2時,由于發射結空間電荷區仍保持在截止時的寬度,故發射區的電子不能立即穿過發射結到達基區 。這時發射區的電子進入空間電荷區,使空間電荷區變窄,然后發射區開始向基區發射電子,晶體管開始導通。這個過程所需要的時間稱為延遲時間句。

經過延遲時間 tct 后,發射區不斷向基區注入電子,電子在基區積累,并向集電區擴散,形成集電極電流 ic。隨著基區電子濃度的增加,ic 不斷增大 。ic 上升到最大值的 90%所需要的時間稱為上升時間 tr。則開通時間為 ton=td+tr, 開通時間的長短取決于晶體管的結構和電路工作條件 。

關閉時間: 三極管從飽和狀態到截止狀態所需要的時間。

進入飽和狀態后,集電極收集電子的能力減弱,過剩的電子在基區不斷積累起來,稱為量存儲電荷,當輸入電壓 ui 由+U2 跳變到-U1 時,存儲電荷不能立即消失,而是在反向電壓用下產生漂移運動,使集電極電流維持 lcs 不變,直至存儲電荷全部消散,晶體管才開始退出飽和狀態,ic 開始下降。

在反向的基極電壓的作用下,集電極電流 iC 不斷減小,并逐漸近于零。集電極電流由 0.9Ics 降至0.1Ics 所需的時間稱為下降時間tf。則關閉時間為 toff=ts+tf。 關閉時間的長短取決于三極管的結構和運用情況。ton和toff的大小反映了三極管由截止到飽和與從飽和到截止的開關速度,它們是影響電路工作速度的主要因素。

2 TTL基本電路的工作原理

2.1 TTL的反相器結構域工作原理

反相器TTL典型的電路如下圖:由三部分組成,T1 、R1 和 D1組成的輸入, T2、R2 和 R3組成的倒相級,T4、T5、D2和R4組成的輸出級 。

工作原理:

輸入信號 A 的高、低電平分別為:VIH=3.4V , VIL=0.2V 且 Vbc=0.7V, Ec=+5V。

(1) 輸入信號 A 為低電平 VIL=0.2V

T1 的發射結導通 ,并將 T 1 的基極電位鉗在 VIL+Vbe1=0.9V,因為T1的集電極回路電阻為R2和T2的b-c結反向電阻之和,阻值非常大,所以 T1 工作在深度飽和區,Vces1≈0, Vc1=VIL+Vces1=0.2V 。

顯然,T2 的發射結不導通,T2 截止,Vc2 為高電平,Ve2 為低電平,使 T5截止,故 R2上的壓降很小,Vc2≈Ec,T4 管導通。因此,輸出為高電平 VoH=Ec-Vbe4-VD2=3 .6V。

(2)輸入信號 A 為 高電平 VIH=3 .6V

T1導通時其基極電壓 Vb1=VIH+0.7=4.3V,集電極電壓大于發射極電壓,使T1和T5管飽和導通,Vo=VoL=Vces5=0.3V,Vc2=Vces2+Vbe5=0.3+0.7=1V,則 T4和 D2 管截止。

綜上所述, TTL 反相器輸入端輸入低電平,輸出即為高電平:當輸入端輸入高電平時,輸出為低電平,實現了非邏輯功能也稱為非門 。

2.2 肖特基 TTL C STTL) 結構及原理

BJT工作在飽和狀態時,發射結和集電結都處于正向偏置,集電結正向偏置電壓越大,表明飽和程度越深。為了限制 BJT 的飽和深度,在 BJT 的基極和集電極上并聯一個導通閾值電壓較低的肖特基二極管,如下圖所示。

當沒有 SBD 時, 隨著基極電壓的升高,電流直接沿著基極和集電極方向流動 。由于 SBD作用 ,當基極電壓大于 0.4V 時, SBD 首先電導通, 電流沿著 SBD 方向流動, 從而使 T 的基極電流不會過大(而且 T 的集電結正 向偏壓將被鉗制在 0.4V 左右) , 因SBD 起到抵抗過飽和的作用,因而又將這種電路稱為抗飽和電路,使電路的開關時間大為縮短。

-

三極管

+關注

關注

142文章

3561瀏覽量

120876 -

反相器

+關注

關注

6文章

307瀏覽量

43043 -

信號完整性

+關注

關注

68文章

1380瀏覽量

95166 -

CMOS電路

+關注

關注

0文章

49瀏覽量

11463 -

高速邏輯電路

+關注

關注

0文章

3瀏覽量

5657

發布評論請先 登錄

相關推薦

信號完整性學習筆記之高速邏輯電路介紹

信號完整性學習筆記之高速邏輯電路介紹

評論