隨著領先的芯片制造商繼續將finFET以及很快的納米片晶體管縮小到越來越小的間距,使用銅及其襯墊和阻擋金屬,較小的金屬線將變得難以維持。接下來會發生什么以及何時發生,仍有待確定。

自從IBM在20世紀90年代向業界引入采用雙鑲嵌工藝的銅互連以來,半導體行業一直在利用銅的高導電性、低電阻率和可靠互連的優勢。但隨著電阻和電容的增加,RC延遲將繼續顯著影響器件性能。

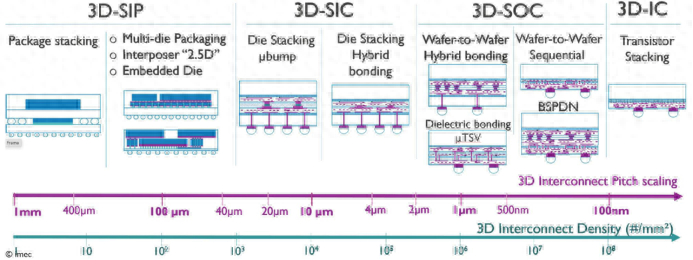

與此同時,系統性能驅動因素使得在可能的情況下將存儲設備移至生產線后端變得有吸引力。如果業界開始引入具有較低熱預算的互連工藝,那么存儲器或其他設備集成之類的事情就變得可行。但首先,必須解決延伸銅線和引入背面配電方案的直接工程挑戰。

銅的里程更長

在2nm邏輯節點,銅線和通孔正在通過創造性的方式延伸。一些吸引力的選擇包括限制阻擋層和襯墊材料的電阻率影響,要么通過使這些薄膜更薄——從化學氣相沉積(CVD)到原子層沉積(ALD)——要么消除它們,例如沿著通孔和線路之間的垂直路徑。

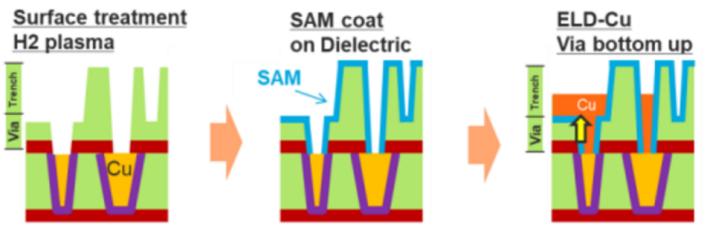

圖1

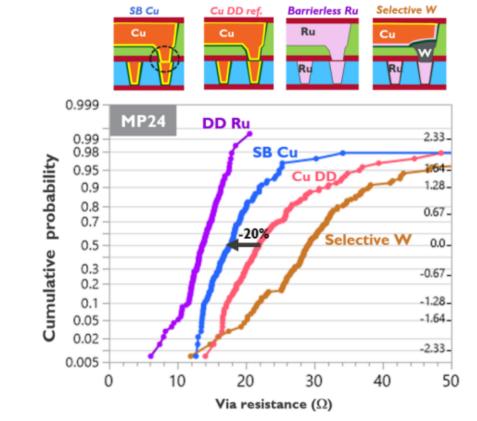

圖2

英思特測試了預通孔填充工藝,該工藝在銅填充下不使用阻擋層(TaN),而是在無電沉積(ELD)后進行沉積。微小過孔是互連鏈中的薄弱環節(圖2),關鍵工藝步驟是在對通孔底部暴露的銅進行原位界面工程之后,僅在電介質上進行選擇性ALD TaN阻擋層沉積,通過消除勢壘,通孔電阻可降低20%。在較小的尺寸下,減少量會更大。

連接背面電源

背面供電(BPD)是一種從晶圓背面向晶體管供電的創新方法,從而釋放正面互連以僅傳輸信號。這緩解了擁塞,利用晶圓背面進行配電,可以有效增加芯片的功能面積,而無需增加其占地面積。

背面電源集成的較大挑戰之一是如何以電氣方式連接晶圓正面和背面。較具挑戰性的方案涉及到源外延的直接背面接觸。通孔將很小且縱橫比很高,還需要與外延層進行低電阻接觸,就像正面的源極/漏極接觸一樣。因此,鎢填充物或可能是鉬將是可能的選擇。

結論

如今,雙鑲嵌銅的間距已擴展到20納米,但涉及釕或其他替代金屬的減材方案即將發生根本性變化。就電阻率而言,隨著尺寸降至17 x 17nm以下,釕變得有吸引力。公司可以使用無障礙通孔底部來獲得額外收益,同時為偉大的轉型做好準備。

審核編輯 黃宇

-

半導體

+關注

關注

334文章

27064瀏覽量

216504 -

晶圓

+關注

關注

52文章

4851瀏覽量

127817 -

晶體管

+關注

關注

77文章

9641瀏覽量

137877

發布評論請先 登錄

相關推薦

小馬智行IPO規模擴大,籌資額增至4.52億美元

可用于大規模量產的新型雙面銅鍍膜技術, 王璐博士團隊最新WILEY發文

集成電路的互連線材料及其發展

銅包銀和無氧銅網線哪個好

全球儲能新增規模持高速增長

無氧銅和銅包鋁的網線哪個好用

銅互連,尚能飯否?

在被超60億美元收購后,日本光刻膠巨頭JSR尋求擴大規模

中國電信研究院攜手中興通訊與長飛光纖,實現單纖單向超120Tbit/s突破

SiC功率器件先進互連工藝研究

晶圓到晶圓混合鍵合:將互連間距突破400納米

EMS能效管理平臺降低銅電解單耗的應用

研究銅互連的規模能擴大到什么程度

研究銅互連的規模能擴大到什么程度

評論