1 容性分支在傳輸線中間引起的反射影響

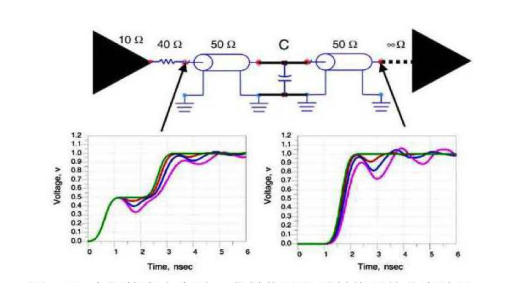

附著在走線中間的測試點 , 通孔, 封裝引線,甚至一小段分支,作用就像一個集總電容 。下圖所示就是一個電容加在走線中間時,發射電壓和反射電壓的仿真結果。

圖為電容最初的阻抗較低,反射回源端的信號將有輕微的負極性偏向。下圖所示的情況是上升時間為 0.5ns,容分別為 0,2, 5, 10pF 的情況 。

發射信號最初不會受到影響,但是當它從走線末端返回到源端時,就會受到影響 。返問信號再次遇到電容, 其中一些信號將帶有負號,反射回遠端 。這些反射回到接收端就為負電壓,使接收到的信號下降,導致下沖。

輸線中間理想電容的影響依賴于信號的上升時間和電容的大小。電容越大,阻抗越小 ,會產生更大的負極性反射電壓,導致接收端出現更大的下沖。

在時域內,電容的阻抗為:

如果信號是線性傾斜的,帶有上升時間為 RT, dV/dt 變為 V/RT,電容的阻抗為:

在上升時間的時間間隔內,信號線與返回路徑間的電容是分流阻抗 Zcap, 跨越傳輸線的分流阻抗會導致反射。如下圖所示。為了使該阻抗的存在不產生嚴重問題, 希望這個阻抗比傳輸線的阻抗大的多,即希望 Zcap>>Z0 作為起始位置,Zcap>5*Z0則電容和上升時間約束條件為 :

Cmax =反射噪聲可能成問題之前,可接受的電容的最大值,單位為 nF。

2 短分支傳輸線的反射影響

分析短線的影響是比較復雜的,因為要考慮很多反射的問題。當信號離開驅動端,首先會遇到分支點 。這里我們會看到兩段傳輸線并聯產生一個低的阻抗,則一個負反射將會返回到源端 。兩個重要的因素可決定分支對信號完整性的影響,即信號的上升時間和分支的長度。

設分支位于傳輸線的中間,并且與傳輸線有相同的阻抗 。下圖所示了在分支長度從上時間的 20 %增加到 60% 時,對發射信號和反射信號仿真的結果 。

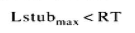

根據經驗規則, 分支的長度保持小于上升時間延展的 20%,則分支的影響就不重要。反之對信號就會產生影響。經驗規則用式子來表示:

其中 Lstubmax 為可接受的分支長度的最大值,單位為 inch; RT 為信號的上升時間,單位為s;

例如,對于1ns 的上升時間,應保持分支長度小于 1inch。很明顯 , 當上升時間變短時,將分支長度減小,使其不影響到信號的完整性,就變得越來越困。

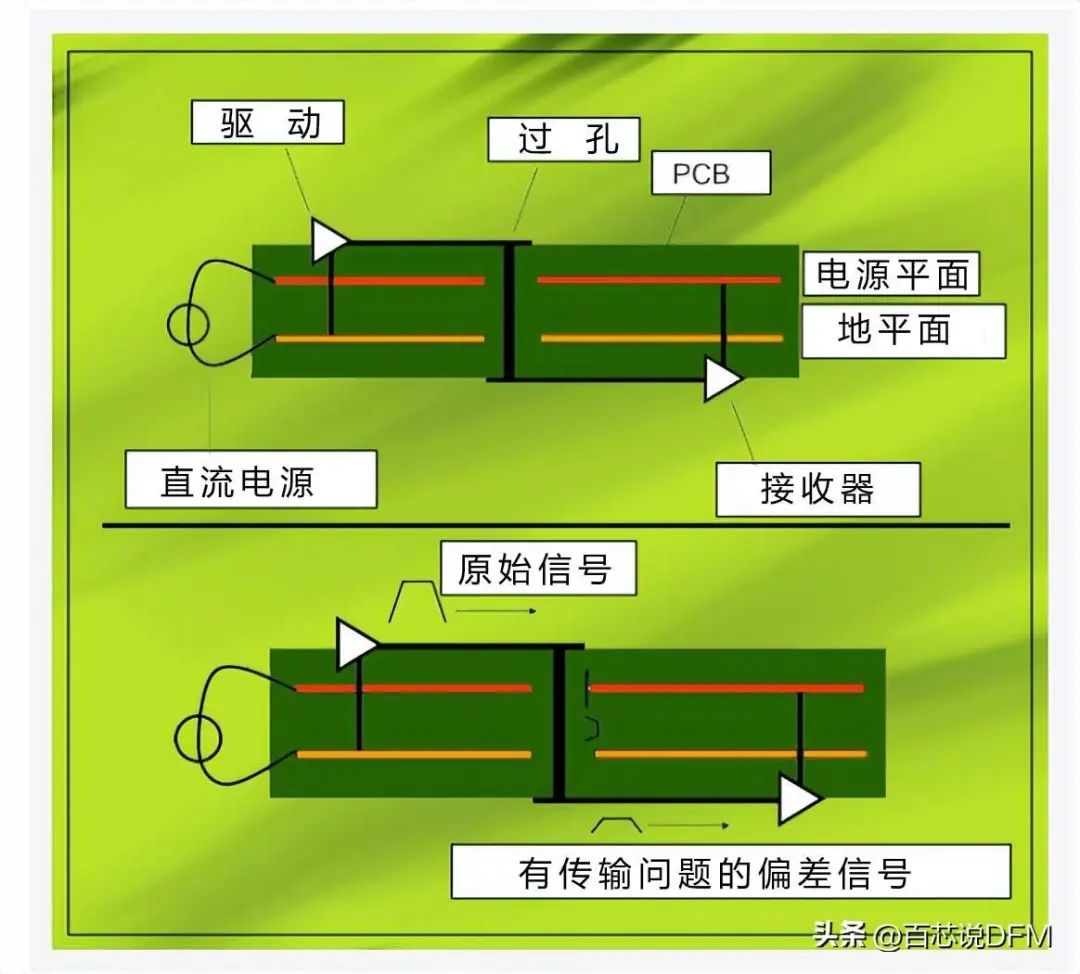

3 拐角和通孔的影響

當信號沿著均勻的互連線傳輸時,發射信號不存在反射及失真。如果均勻互連線存在 90的彎曲,就有阻抗的改變,則發生反射及信號的失真。90度的拐角導致了均勻互連線阻抗的不連續性,影響了信號的完整性。

下圖所示是對上升時間為50psec 的信號所作的 TDR響應,附近有2個90 度的拐角,阻抗不連續性而導致反射,線寬為 65mil,阻抗為50歐姆。

將 90 度的拐角轉換為 45 度的彎曲將會減小這種影響,如果改用常寬的圓弧狀彎曲,影會進一步減小。

拐角對信號傳輸線的唯一影響是由于走線彎曲處的額外寬度 。這個額外的線寬作用就像個容性的不連續性。這個容性的不連續性導致了信號的反射和時延 。

如果走線的彎曲處是常寬的,走線寬度沒有改變,信號在拐彎的每一點遇到的阻抗都是

相同的, 那么就不會有反射。下圖表明了拐角代表了正方形的一部分,粗略的估計,有正方形的一半。

拐角的電容可從正方形的電容以及走線單位長度的電容來估算:

走線單位長度的電容與走線的特性阻抗有關:

對拐角電容的估計為:

我們可以把這個估算概括成為一個方便記憶的經驗規則,在 50 歐姆的傳輸線中,拐角所帶來的相關電容為2 ×線寬 。線寬單位為 mil,電容單位為 fF。

若仍然保持 50 歐姆的阻抗,而線寬變窄,則拐角所帶來的電容將變小,影響就不明顯 。對于高密度電路板上的標準信號線, 5mils的線寬,管腳的電容為 10fF。

10fF的電容所帶來的反射噪聲信號的上升時間,根據公式

上升時間為 0.010pF/4~3ps.

10fF的電容所帶來的信號的時延,根據公式

時延為 0. 5× 50× 0.01pF=0.25ps 。

如果用通孔來連接一根信號線與測試點,或是與相鄰板層的另一根信號線相連,通孔會對于電路板的不同層具有過多的電容。這時,通孔可看作是一個集總的電容負載 。

通孔的電容大小依賴于孔的大小,隔離孔,板的表層及底層焊點的大小 。它的大小可從 0. 1pF 到超過1pF 的范圍 。信號線上的任一通孔都可看作是容性的不連續性,在高速互連中,是影響信號完整性的主要因素 。

4 載重線的反射影響

當傳輸線上有一個容性負載時,信號會發生失真,并且上升時間下降。如果有多個負載布在傳輸線上,如果間隔與信號上升時間的空間延展相比要短,則從每個電容性不連續的反射會消除 。帶有均勻間隔分布的容性負載的傳輸線叫做載重線 。

每個不連續段都可看作是較低阻抗的區域。如果上升時間與電容間的時延相 比要短時,每個間斷的作用對信號來講就像離散的不連續性 。如果上升時間與電容間的時延相比要長,低阻抗區域疊加, 整個線的平均阻抗更低。

對于三個不同的上升時間,載重線的反射信號如圖示。在該例中,5個3pF的電容每隔1inch 分布在50歐姆的傳輸線上,走線的最后10inch沒有負載。

對于開始的幾個電容,可看到明顯的不連續性,但是后幾個的電容帶來的不連續性被消 。當上升時間與電容間時延相比要長時,均勻分布的容性負載產生的效果,即走線的表面來的特性阻抗降低。在這種負載線中,單位長度的阻抗增加意味著特性阻抗更低,時延更。

在均勻的,未加電容負載的傳輸線中,特性阻抗和時延與單位長度的電容和電感有關:

如果有均勻分布的電容負載,每個負載為 C1間隔為d1, 走線上單位長度分布的電容從C0L增加到(C0L+C1/d1).特性阻抗和響應的時延為:

可見,當增加分布的電容負載時,走線的特性阻抗降低,則端接電阻也應降低 。

-

電容器

+關注

關注

64文章

6205瀏覽量

99331 -

信號完整性

+關注

關注

68文章

1398瀏覽量

95389 -

TDR

+關注

關注

1文章

69瀏覽量

19893

發布評論請先 登錄

相關推薦

信號完整性(五):信號反射

信號完整性簡介及protel信號完整性設計指南

信號完整性與電源完整性分析 第三版 pdf_反射、串擾、抖動后,我的信號變成什么鬼?...

信號完整性的反射因素詳解

信號完整性的反射因素詳解

評論