作者:Jeff Shepard

隨著電子設備的集成度越累越高、使用數量越來越多,設計人員不斷面臨著提高效率,同時降低成本、減小尺寸和電磁干擾 (EMI)的壓力。雖然電源在功率密度和效率方面也有所提高,但設計人員現在還面臨著為異構處理架構開發多軌電源解決方案的難題,這些架構可能由 ASIC、DSP、FPGA和微控制器組成。

傳統上,降壓式 DC/DC 轉換器用于為此類架構供電,但隨著電源軌數量的不斷增加,使用傳統分立降壓式 DC/DC 轉換器與、控制 IC、內部或外部功率MOSFET,再加上外部電感器和電容器,可能會變得既復雜有耗時。相反,設計人員可以使用具有多軌和可編程定序的自足式降壓 DC/DC轉換器模塊。這種模塊可以更好地控制 EMI,發熱更少,且所需面積更小。

本文將回顧嵌入式設計的電源系統需求,討論各種方法和設計人員需要考慮的問題,然后介紹自足式降壓 DC/DC 模塊的概念。然后,以 MonolithicPower Systems 的器件為例,簡要回顧設計人員需要牢記的設計和布局考慮因素,以便最大限度地發揮這些模塊的性能優勢。

為什么嵌入式系統需要很多電源軌

諸如 5G基站等嵌入式設計旨在支持智能手機、智能互聯設備不斷增加的數據要求,其應用涵蓋家居和工業自動化、自主駕駛車輛、醫療保健和智能可穿戴設備等。這類基站通常使用 48伏輸入電源,經 DC/DC 轉換器降至 24 伏或 12 伏,然后進一步降至 3.3 伏至 1 伏以下的許多子電源軌,為基帶處理階段的

ASIC、FPGA、DSP 和其他設備供電。通常,電源軌需要對啟動和關斷進行排序,這會進一步增加電源系統的復雜性。

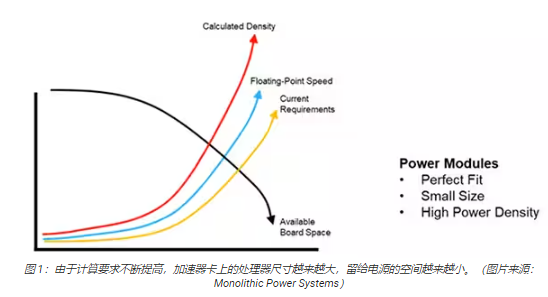

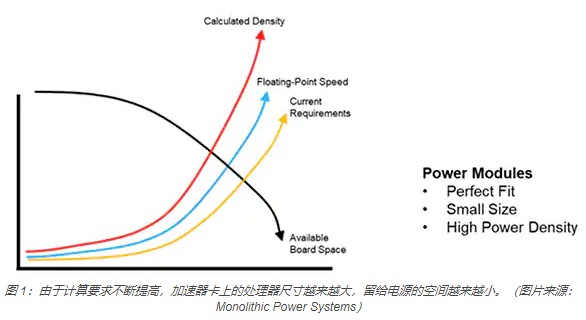

以 5G 基站為例,傳統的 CPU 本身已經不能滿足處理要求。但是,使用加速卡與 FPGA配合使用,在系統可重構性、靈活性、開發周期短、高度并行計算、低延遲等方面都占有優勢。但 FPGA 電源的空間越來越小,而且對電源軌的性能要求也很復雜(圖1)。

輸出電壓失調:電壓軌的輸出電壓偏差必須小于 ±3%,設計時應留有足夠裕量。通過優化控制回路,提高帶寬,保證其穩定性,應謹慎使用和設計去耦電容器。

單調啟動:所有電壓軌的初始值必須單調上升,在設計上應阻止輸出電壓回到起始值。

輸出電壓紋波:穩態運行時,所有電壓軌的輸出電壓紋波(模擬電壓軌除外)必須最高達到 10 毫伏(mV)。

時序:FPGA 在啟動和關斷期間必須滿足特定的時序要求。

隨著數據處理帶寬要求越來越高,處理器對電流和功率的要求也愈加苛刻。加速器卡的計算密度和浮點速度的要求也越來越難以滿足。加速器卡槽一般都采用 PCIe標準,所以板卡的尺寸是固定的。由于計算要求不斷提高,處理器尺寸不斷增大,留給電源的空間已經變得很小。

電源系統設計替代方案

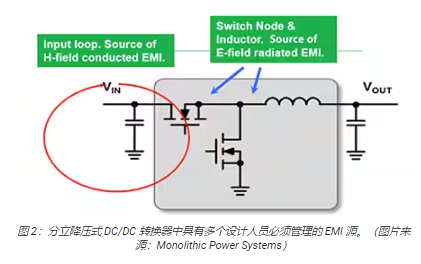

使用傳統的分立降壓式 DC/DC 轉換器,配以控制 IC、內部或外部功率MOSFET,再加上外部電感和電容,組成了嵌入式系統供電的一種方法。如上所述,當需要多軌電源解決方案時,對設計人員來說是一個復雜、耗時的過程。除了考慮效率最大化和解決方案尺寸最小化外,設計人員還必須謹慎對待濾波器元件的布局和放置,以最大限度地減少轉換器和電感電路中的開關電流引起的傳導和輻射EMI(圖 2)。

DC/DC 轉換器通常會通過輸出功率 MOSFET 開關節點對地和輸入電容對地之間形成的電流環路的磁場產生傳導 EMI。同時,這種轉換器還通過MOSFET 開關節點到電感連接處產生輻射電場 EMI,因為該器件連續從高輸入電壓水平切換到地,所以具有很高的dV/dt,同時會通過電感內產生的電磁場產生輻射電場 EMI。如果設計不當,往往會導致耗時的 EMI 實驗室重新測試和多次設計迭代。

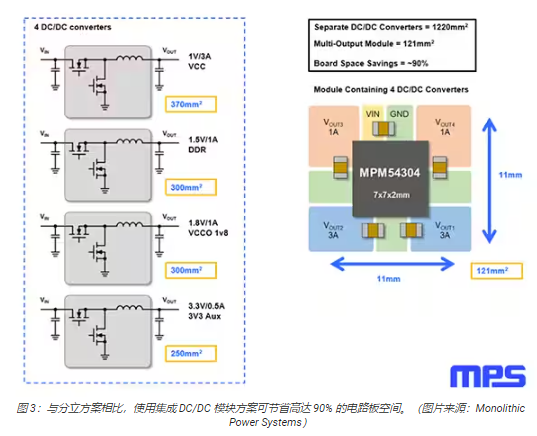

使用分立降壓式 DC/DC 轉換器向 ASIC 或 FPGA 供電的四軌解決方案可占用 1220 平方毫米 (mm2)(圖 3)。使用基于電源管理 IC(PMIC) 的解決方案可以將這一數字降低至約 350mm2。作為替代方案,設計人員可以使用獨立的四輸出 DC/DC 轉換器模塊,將解決方案的尺寸縮小到只有121 mm2,同時還可以簡化設計流程,加快產品上市速度。半導體工藝技術和封裝結構的進步意味著最新一代的 DC/DC模塊在較小的外形內實現了非常高的功率密度、高效率和良好的 EMI 性能。

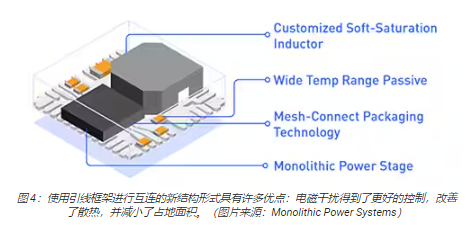

新的構建技術,如封裝內倒裝芯片和“網狀連接”引線框架技術,意味著 IC、電感器和無源器件可以直接安裝在引線框架上,而不需要導線鍵合或額外的內部 PC板(圖 4)。與使用內部 PC 板基板或導線鍵合的老式結構相比,這些新技術可以最大限度地減少印制線長度,并且與無源元件直接連接可以保持低電感,從而最大限度地減少EMI。

使用接點柵格陣列 (LGA) 封裝形式,直接貼裝至目標 PC 板上,比起其他引線可輻射 EMI 的單線 (SIL) 或 SIL 封裝 (SIP)式轉換器具有更低的 EMI 曲線。

四路輸出可編程集成 DC/DC 模塊

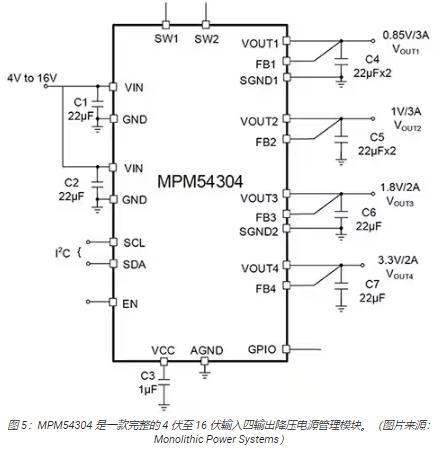

為了滿足嵌入式系統的多軌、高功率密度需求,設計人員可以使用 Monolithic Power Systems 的 MPM54304(圖 5)。MPM54304 是一個完整的電源管理模塊,集成了 4 個高效率、降壓式 DC/DC 轉換器、電感器和一個靈活的邏輯接口。MPM54304 在 4 伏至16 伏的輸入電壓范圍內工作, 可支持 0.55 伏至 7 伏輸出電壓。四條輸出軌分別可以支持高達 3 安培 (A)、3 A、2 A 和 2 A的電流。其中,兩條 3 A 軌和兩條 2 A 軌可以并聯,分別提供 6 A 和 4 A電流。設計人員應注意,并聯模式下的最大輸出電流也受到總功率耗散的限制。這樣,我們就可靈活地選擇幾種輸出配置(但受總功率耗散限制)。

3 A、3 A、2 A、2 A

3 A、3 A、4 A

6 A、2 A、2 A

6 A、4 A

MPM54304 還提供了啟動和關斷的內部排序。可以通過多時可編程 (MTP) 電子保險絲或通過 I2C 總線對導軌配置和排序進行預編程。

這款固定頻率恒定時間 (COT) 控制式 DC/DC 轉換器可具有快速瞬態響應能力。其默認 1.5 兆赫 (MHz)開關頻率大大減小了外部電容器的尺寸。在連續電流模式 (CCM) 工作期間,開關時鐘鎖定并從降壓 1 到降壓 4 移相。輸出電壓可通過 I2C 總線調節或 MTP電子保險絲預設。

該器件保護功能全面,包括欠壓鎖定 (UVLO)、過電流保護 (OCP) 和熱關斷。MPM54304 所需的外部元器件數量極少,并采用節省空間的 LGA(7 mm x 7 mm x 2 mm) 封裝(圖 6)。LGA 的扁平外形使其適合板后布置或置于散熱器下。

設計和布局注意事項

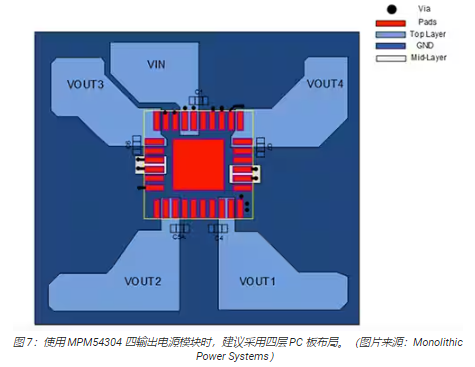

MPM54304 的邊沿引腳布局簡單,使布局和 PC 板設計更容易。只需 5 個外部器件,整體解決方案小巧緊湊。LGA封裝使得堅實的接地平面覆蓋了模塊下方的大部分區域,這有助于封閉渦流回路,進一步降低 EMI。

這種降壓轉換器的輸入電流是不連續的,在保持直流輸入電壓的同時,需要一個電容器向轉換器提供交流電流。設計人員應使用低等效串聯電阻 (ESR)電容器,以獲得最佳性能。推薦使用 X5R 或 X7R 電介質陶瓷電容器,因為其 ESR 低、溫度系數小。對于大多數應用來說,22 微法拉 (μF)電容器就足夠了。

高效的 PC 板布局是 MPM54304 穩定運行的關鍵。為了達到更好的散熱性能,建議使用四層 PC 板(圖

7)。為了達到最佳效果,設計師應該遵循這些準則。

盡量減少電源回路

用一個大型接地平面直接連接 PGND。如果底層是接地平面,則在 PGND 附近增加過孔。

確保 GND 和 VIN 處的大電流路徑具有短而直接的寬印制線。

將陶瓷輸入電容盡可能地靠近該器件。

盡量保持輸入電容和 IN 盡可能短,盡可能寬。

將 VCC 電容盡可能靠近 VCC 和 GND 引腳。

將 VIN、VOUT 和 GND 連接到一個大面積的銅片上,以提高散熱性能和長期可靠性。

將輸入 GND 區域與頂層的其他 GND 區域分開,并在內部層和底層通過多個過孔連接在一起。

確保在內部層或底層有一個集成的 GND 區域

使用多個過孔將電源平面連接到內部層。

結語

隨著處理架構的不斷發展,以應對苛刻的數據應用,設計人員面臨著開發多軌電源解決方案的挑戰:要求這些解決方案能夠支持更強的處理能力和更多體積不變或更小的電子器件。在設計這些系統的電源解決方案時,降壓式DC/DC 轉換器是關鍵,但實施起來可能很復雜。

如圖所示,設計人員可以轉向具有多電源軌和可編程排序功能的自足式降壓 DC/DC轉換器模塊,從而簡化設計流程,加快產品上市。同時,新的構建技術使這些自足式模塊具有了許多性能優勢:電磁干擾得到了更好的控制,改善了散熱,減小了占地面積。

-

電源

+關注

關注

184文章

17586瀏覽量

249502 -

轉換器

+關注

關注

27文章

8627瀏覽量

146872 -

嵌入式

+關注

關注

5068文章

19019瀏覽量

303302 -

電源轉換

+關注

關注

0文章

144瀏覽量

23708 -

降壓式

+關注

關注

0文章

8瀏覽量

6132

發布評論請先 登錄

相關推薦

Vicor 發布高密度AC-DC前端模塊

高密度DC/DC轉換器的PCB布局第二部分

雙輸出高效率高密度模塊穩壓器DC2066A

具有雙端口CLA應用的高效率降壓DC/DC轉換器

DC/DC轉換器的高密度印刷電路板(PCB)布局

使用集成降壓式DCDC模塊實現具有較低EMI高密度高效率電源轉換

具有PMBus接口的高密度160A 4相DC DC降壓轉換器設計

使用集成降壓式 DC/DC 模塊實現具有較低 EMI、高密度、高效率電源轉換

使用集成降壓式 DC/DC 模塊實現具有較低 EMI、高密度、高效率電源轉換

評論