開發目的

FPGA項目開發的過程中,需要完成設計代碼開發、驗證環境搭建、仿真分析、板級驗證等操作,在這個過程中,許多操作雖然必不可少但是步驟是重復的。輔助軟件通過預先定義的處理模式,對一些重復性復雜操作通過Python輔助軟件使操作簡化以提高項目開發效率。獨立仿真可以不依賴Vivado,簡化仿真步驟,但建立獨立仿真往往需要復雜繁瑣的步驟,所以簡化建立獨立仿真的步驟很有必要。

重要的是,有了脫離Vivado建的第三方仿真工具單獨的環境,為FPGA工程后續ASIC化提前搭建好仿真環境,只把用到的庫和相關文件從Vivado庫里抽取出來,同時,每次仿真時不用啟動非常占資源的Vivado軟件,直接運行仿真腳本即可。同時,軟件生成的仿真環境后也可以手動進行優化調整,按照用戶自己熟悉的仿真習慣進行定制化修改。

功能描述

該軟件用于提升FPGA仿真效率,節省仿真時間和步驟。本軟件可以建立獨立仿真,生成Questasim、modesim或VCS環境下的獨立仿真,可視化界面,更加方便用戶操作。

RTL設計完后會進行仿真Vivado內自帶仿真器,或者可以通過Vivado啟動第三方仿真工具聯合仿真。但是在實際項目開發過程中,當我們修改代碼后,需要關閉仿真軟件并重啟仿真,之前加載的波形信號也需要重新加載。因而很多時候,我們希望脫離Vivado,利用Modelsim或者VCS等第三方仿真工具,提高仿真效率;在這個過程中,通過提取工程中的代碼文件和IP核信息文件,縮減工程所占用的內存空間,方便項目開發人員同步及備份。該軟件建立獨立仿真首先會提取源仿真工具、目的仿真工具,了解要建立哪種環境下的獨立仿真。

還要提取自動化仿真文件名和創建獨立仿真的路徑,用于建立獨立仿真文件夾,該文件夾有rtl和sim兩個文件夾,仿真用到的文件都會放到該文件夾里面。然后會提取tb的module名字和vivado生成do文件路徑,該軟件會根據路徑和tb的module名字找到Vivado生成do文件,提取do文件里面的信息,把對應文件放到自動化仿真文件夾里面。提取目的仿真工具的win64和.setup文件的路徑,用于建立批處理文件和makefile文件。提取完信息后,點擊“開始生成按鈕”即完成建立自動化仿真操作。

該軟件在可執行python的環境下均可以運行,在實際項目測試中,能夠自動生成自動化仿真工程,減少仿真對vivado的依賴,減少了大量的重復性操作。

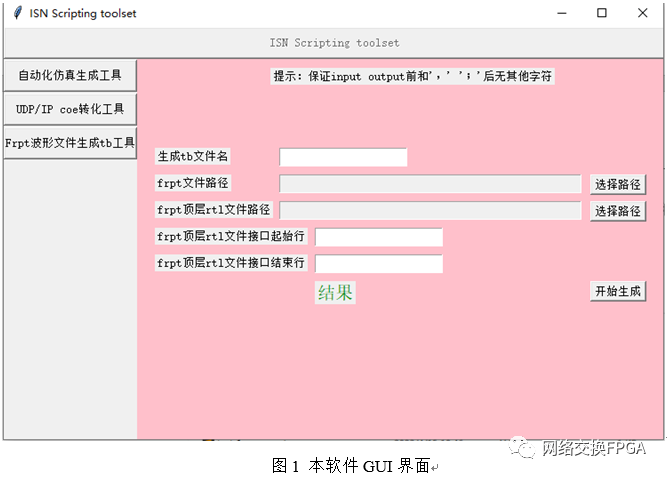

為了方便項目開發人員對輔助軟件的使用,輔助軟件需要具有良好的可視化操作界面,在完成一些基本參數的配置后,可一鍵式完成復雜操作。GUI界面如圖1所示:

使用說明

1 安裝和初始化

本軟件免安裝,通過點擊FPGA_simulate_tool.exe文件即可執行,如圖2所示:

2 輸入

根據GUI界面的提示輸入需要執行的命令。

3 輸出

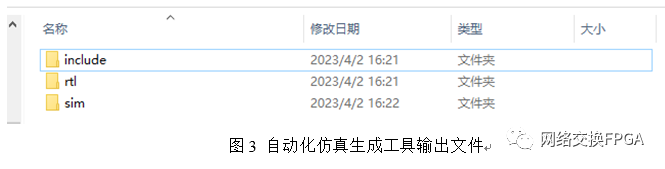

運行軟件后,首先會根據選擇生成不同的輸出文件,選擇“自動化仿真生成工具”,輸入提示信息后,點擊生成“開始生成”,會生成自動化仿真工程,如圖3所示,其中所有rtl文件存放在rtl文件夾下,include文件存放在inlcud文件夾下,sim文件存放do文件和批處理文件。

操作步驟

本軟件在Window10的python可執行環境下示例操作。自動化仿真生成工具使用步驟如下:

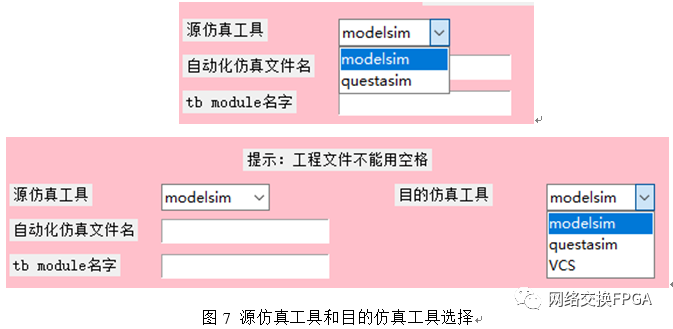

步驟1:首先選擇源仿真工具和目的仿真工具。源仿真工具可供選擇的有:ModeSim、Questasim,目的仿真工具可供選擇的有ModeSim、Questasim、VCS,如圖7所示。

步驟2:輸入tbmodule名字、自動化仿真文件名字,會產生該名字的文件夾,自動化仿真工程在該文件夾里面。

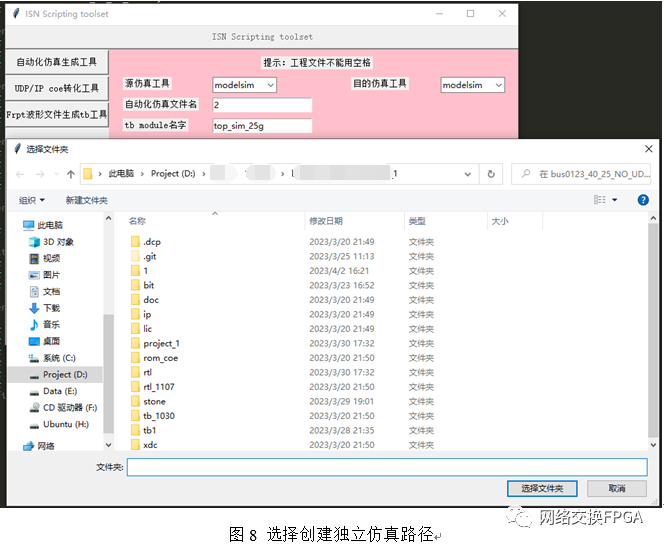

步驟3:選擇“創建獨立仿真路徑”后面的“選擇路徑”按鈕,會讓選擇路徑,選擇好后點擊“選擇文件夾”按鈕,選擇創建獨立仿真路徑,如圖8所示:

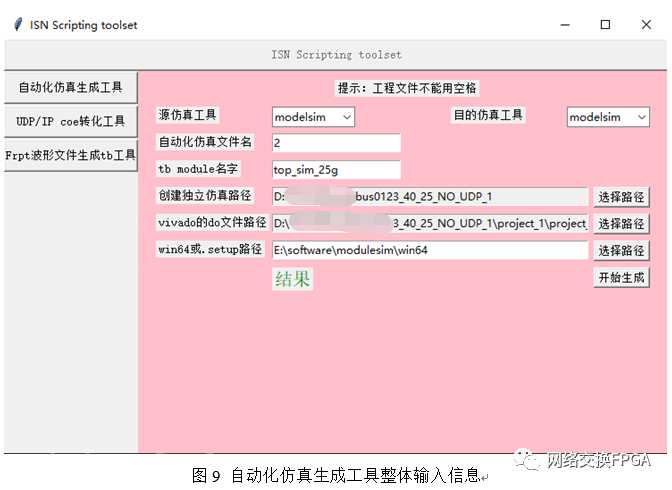

步驟4:點擊“選擇路徑”按鈕,選擇vivado的do文件路徑和win64或.setup路徑,整體輸入信息如圖9所示:

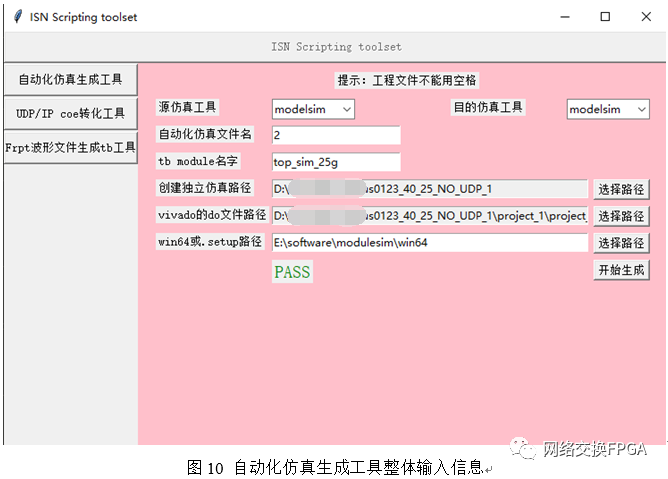

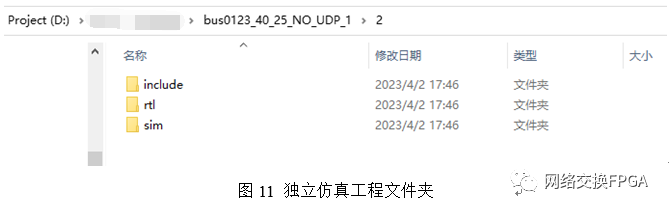

步驟5:點擊“開始生成”按鈕,生成獨立仿真工程,生成成功會顯示“PASS”。如圖10所示。其中獨立仿真工程目錄在D盤文件夾“bus0123_40_25_NO_UDP_1”,文件名為“2”。該文件夾下內容如圖11所示,其中所有rtl文件在rtl文件夾下,所有include文件在include文件夾下。

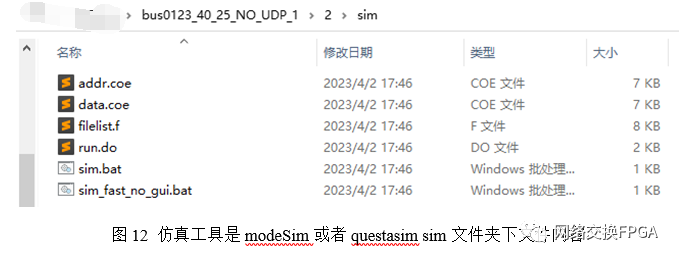

當目的仿真工具選擇“modelsim”或者“questasim”,sim文件夾內容如圖12所示。其中.coe文件是源vivado工程的RAM的初始化文件,不是該軟件生成的文件。filelist.f文件存放所有需要編譯的rtl列表,run.do文件是用于自動化仿真,sim.bat和sim_fast_no_gui.bat是批處理文件,以上四個文件都是該軟件生成。點擊sim.bat或者sim_fast_no_gui.bat即可運行仿真工具進行自動化仿真,其中sim_fast_no_gui.bat省去了仿真工具的GUI界面,可以加速仿真速度。

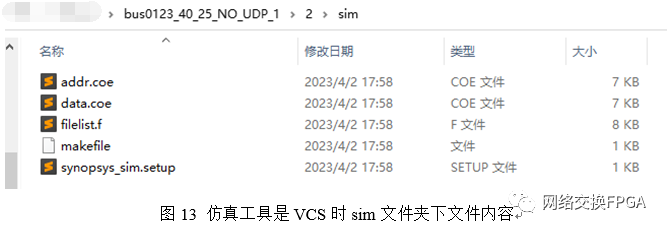

當目的仿真工具選擇“VCS”時(雖然Vivado聯合VCS仿真時有自帶的一鍵轉換到VCS仿真的功能,但本文軟件提供的是一種更直接的脫離方式,把用到的庫和所有文件單獨提取出來放到一個文件夾中,便于分享,也便于為ASIC化的IP替換創建必要的環境),sim文件夾內容如圖13所示。其中.coe文件是源vivado工程的RAM的初始化文件,不是該軟件生成的文件。

filelist.f文件存放所有需要編譯的rtl列表,makefile是自動仿真文件,輸入make即可進行VCS的自動化仿真,仿真完后輸入makeverdi,即可用verdi打開波形文件。

上圖中雙擊sim.bat文件即可運行。

說明:建議在原Vivado工程所在的機器上運行該軟件提取相關腳本信息,原Vivado工程需要調用第三方仿真工具運行過并保留相應的sim文件夾。如有問題,請檢查vivado版本和仿真工具版本,以及編譯的vivado仿真庫所用的vivado版本和仿真工具版本。

結論

本軟件根據預先定義的Python腳本命令,通過用戶與GUI界面的交互,輸入必要的信息,將原本重復繁瑣操作通過輔助軟件進行簡化,提升了RTL的仿真的工作效率。本軟件通過將大量重復性文件和文件夾進行批處理,減少了人力創建文件夾,書寫重復代碼,人工轉化表項等繁瑣操作。此外,通過GUI界面的交互,提供了一個可視化界面,極大的提高了軟件的可操作性。

審核編輯:劉清

-

FPGA

+關注

關注

1626文章

21677瀏覽量

601986 -

FPGA設計

+關注

關注

9文章

428瀏覽量

26489 -

仿真

+關注

關注

50文章

4047瀏覽量

133430 -

仿真器

+關注

關注

14文章

1016瀏覽量

83646 -

RTL

+關注

關注

1文章

385瀏覽量

59710 -

GUI

+關注

關注

3文章

650瀏覽量

39551 -

python

+關注

關注

56文章

4783瀏覽量

84473 -

Vivado

+關注

關注

19文章

808瀏覽量

66343

原文標題:脫離Vivado建立單獨仿真環境軟件

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于PFGA的脫離Vivado單獨建仿真環境工程

如何用Python實現Vivado和ModelSim仿真自動化?

如何使用vivado仿真zynq7000ov5640程序呢?

介紹一下xilinx的開發軟件vivado的仿真模式

Vivado軟件仿真DDS核的過程中應該注意的問題

Vivado調用Questa Sim或ModelSim仿真小技巧

如何脫離Vivado建立單獨仿真環境軟件呢?

如何脫離Vivado建立單獨仿真環境軟件呢?

評論