點擊上方藍字關注我們

1.概述

隨著圖像處理技術的快速發展,圖像采集處理系統在提高工業生產自動化程度中的應用越來越廣泛。本文結合實際系統中的前端圖像處理和圖像數據傳輸的需要,充分利用ARM的靈活性和FPGA的并行性的特點,設計了一種基于ARM+FPGA的高速圖像數據采集傳輸系統。所選用的ARM體系結構是32位嵌入式RISC微處理器結構,該微處理器擁有豐富的指令集且編程靈活;而FPGA則在速度和并行運算方面有很大優勢,適合圖像處理的實時性要求;并且通過千兆以太網接口實現了采集板與上位機之間圖像數據的高速遠程傳輸。

2.硬件設計方案

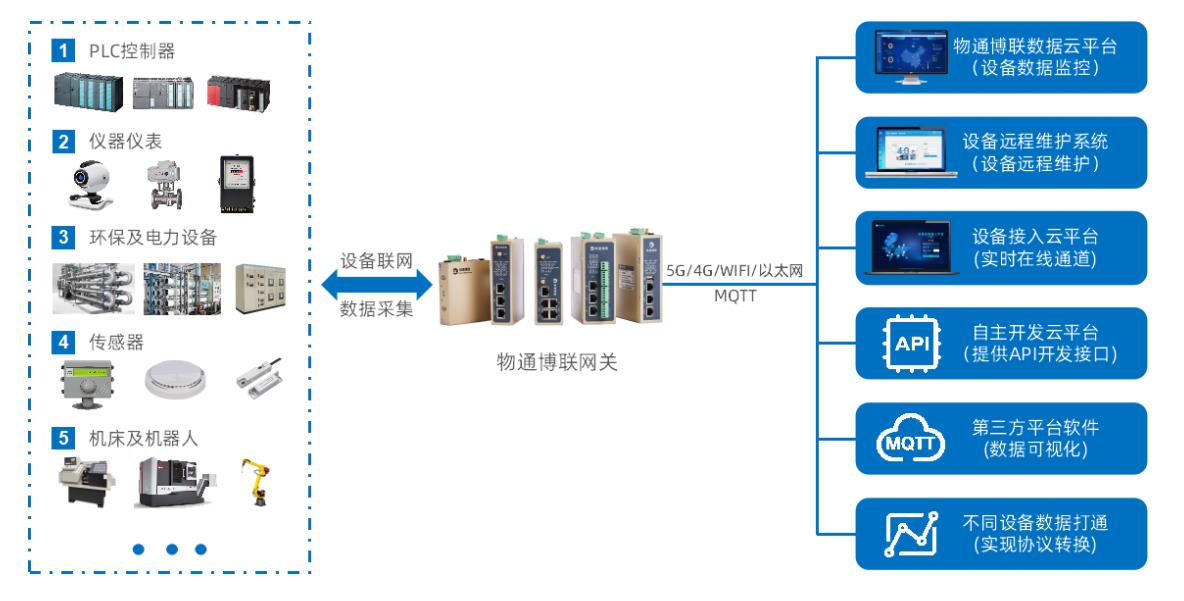

2.1 系統總體設計

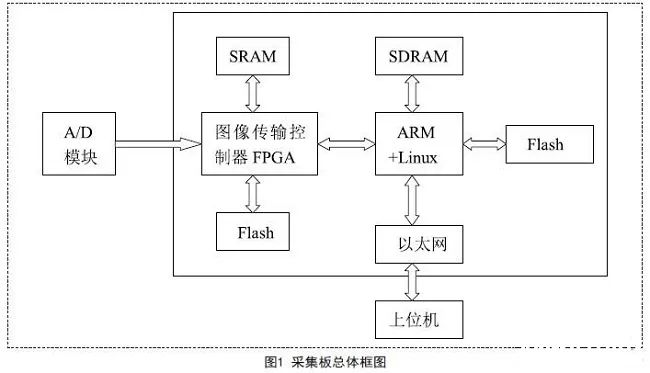

本設計采用的ARM芯片為三星公司的S3C2440A、FPGA芯片為Xilinx公司生產的Spartan系列的S3C500E芯片,系統組成還包括千兆以太網控制芯片AX88180、千兆PHY芯片88E1111、存儲器、嵌入式Linux、網絡驅動程序等(如圖1所示)。

本設計的主控芯片S3C2440A是基于ARM920T核的16/32位RISC微處理器,采用了0.13um的CMOS標準宏單元和存儲器單元,運行頻率高達500MHz.ARM920T 實現了MMU,AMBA BUS和Harvard高速緩沖體系結構構。這一結構具有獨立的16KB指令Cache和16KB數據Cache.每個都是由具有8字長的行組成。通過提供一套完整的通用系統外設,S3C2440A減少整體系統成本和無需配置額外的組件。它主要面向手持設備以及高性價比、低功耗的應用,具有非常豐富的片上資源。

FPGA芯片S3C500E主要用于圖像傳感器的控制、圖像數據的緩存及外圍芯片時序的產生。它通過控制A/D實現數據采集,并保存至SRAM,對ARM的讀寫信號進行譯碼以將目標數據讀回ARM并傳到上位機。

ARM芯片S3C2440A負責整個系統的控制,它通過讀寫總線上的地址來進行指令和數據的傳輸以控制FPGA的所有動作[1-2]。嵌入式Linux內核負責系統任務的管理并集成TCP/IP協議,方便實現網絡控制功能。

S3C2440A與AX88180以總線方式連接,是通信控制的主體。S3C2440A通過網絡驅動程序實現對AX88180內部寄存器編程,以及對以太網數據的發送和接收,從而完成網絡與系統之間的數據傳輸。

AX88180與88E1111之間采用RGMII接口方式互連,負責數據傳送底層協議的實現。

2.2 數據采集接口設計

系統設計的難點在于數據采集接口的設計,它是數據傳輸的通道,同時也是連接系統前后端的橋梁。本系統采用S3C2440A和S3C500E配合共同實現數據的高速采集。

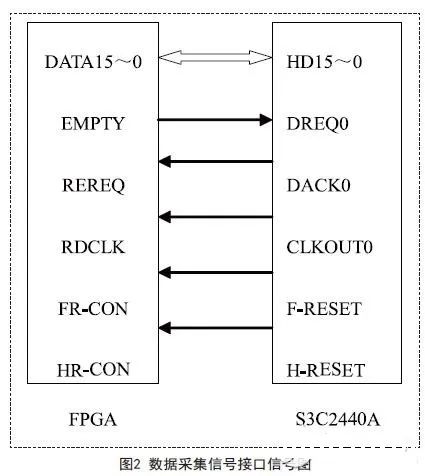

直接內存存取(DMA)作為一種獨立于CPU的后臺批量數據傳輸技術,以其快速、高效的特點在數據采集領域得到了廣泛的應用。本設計中,S3C2440A采用外部DMA方式采集FPGA內部存儲數據,其接口信號連接如圖2所示。

接口設計的FPGA部分主要包括異步FIFO模塊、復位模塊和數據緩沖模塊組成。異步FIFO模塊主要解決圖像輸出數據頻率和數據采集的頻率不匹配的問題,系統采用的異步FIFO寬度為8bits,深度為2048.復位模塊在控制信號的作用下實現對系統的FIFO的復位控制。

系統采用DMA通道0采集圖像數據。

其中,DREQ0和DACK0分別為DMA的請求和應答信號。FPGA的空信號EMPTY與DREQ0相連,讀請求RDREQ與DACK0相連。FPGA寫時鐘由圖像輸出位同步信號提供,讀時鐘由S3C2440A的時鐘輸出引腳CLKOUT0提供。CLKOUT0根據S3C2440A內部寄存器的設置可以輸出幾種不同的時鐘頻率。FIFO的讀操作與ARM的DMA操作配合進行。系統采用單服務命令模式的DMA操作,每次傳輸一個字節數據位。當DREQ0信號變為低電平時DMA操作開始,每次傳輸一個字節后產生一個DACK0應答信號,而且只要DREQ0為低電平DMA操作就繼續進行,直到DMA控制寄存器中的計數器為0,產生DMA中斷。根據上述時序特點,將FIFO的空信號作為DMA的請求信號DREQ0.當圖像輸出的數據寫入FIFO中時,空信號跳變為低電平啟動DMA操作,同時以DACK0信號作為FIFO的讀請求。每次DMA操作后產生的應答信號DACK0使FIFO內部的讀指針前移1位指向下次要讀出的數據。F-RESET和H-RESET分別控制FPGA內的幀同步復位和行同步復位,保證系統在每幀信號到來時開始工作,同時每采集完一行信號復位FIFO.FIFO輸出數據經過以nGCS4為選通信號的BUFFER后接到ARM的數據總線上。nGCS4是S3C2440A存儲空間中BANK4的片選信號,當S3C2440A對地址范圍0×20000000~0×28000000的存儲空間進行讀寫操作時為低電平,其余時間為高電平,NGCS4作為緩沖模塊的選通信號可以有效地避免數據總線的污染。

2.3 網絡傳輸接口設計

本設計采用的以太網控制器為***亞信公司推出的一款Non-PCI千兆以太網控制芯片AX88180.其內置1000Mbps以太網媒體存取控制器(MAC);它可以十分方便地實現與一般16/32位微處理器連接,并且可以像SRAM一樣被訪問;它有40KBytesSRAM網絡封包緩存器。它符合IEEE802.3/IEEE802.3u/IEEE802.3ab協議,可廣泛應用于各種消費電子和家庭網絡市場或要求更高的網絡帶寬連接,如數字媒體、家用網關及IP電視等。

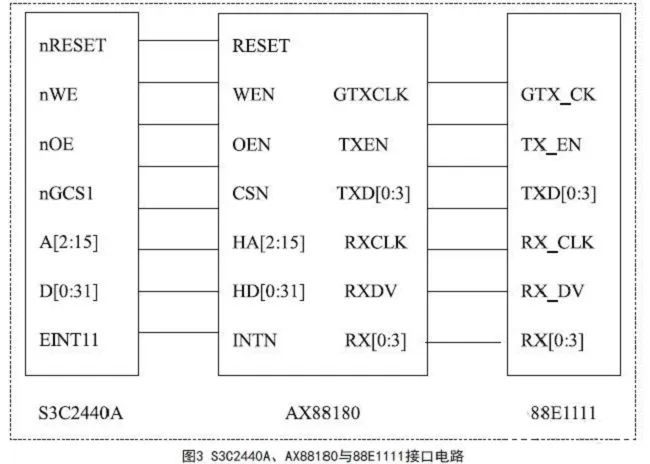

嵌入式芯片S3C2440A、以太網控制器AX88180及物理層芯片88E1111的接口電路圖如圖3所示。

S3C2440A與AX88180之間采用總線方式相連,地址總線A2~A15、數據總線D0~D31、讀寫信號等可以直接連接,AX88180中斷信號與S3C2440A EINT11相連,AX88180的40M~100M時鐘信號由S3C2440A提供,整個接口電路無需外加電路;AX88180與PHY芯片之間采用簡化千兆比特媒體RGMII接口,信號對應 相連,負責實現數據傳送底層協議[5]。

3.Linux驅動程序設計

FPGA作為ARM的外設,需要設計它在Linux下的驅動程序。驅動程序是操作系統與硬件之間的接口,它為應用程序屏蔽硬件的細節。硬件系統只有和高效可靠的驅動程序相結合才能在操作系統下正常工作。

Linux的設備驅動程序需要完成如下功能:

①對設備進行初始化和釋放。

②提供各類設備服務。

③負責內核和設備之間的數據交換。

④檢測和處理設備工作過程中出現的錯誤。

Linux下的設備驅動程序被組織成一組完成不同任務的函數集合,通過這些函數使Windows的設備操作猶如文件一般。

Linux將設備分為字符設備和塊設備兩類。我們使用的是字符設備。驅動程序的模塊化我們先不做介紹,我們主要介紹Linux下的中斷[6].Linux將中斷處理程序分解成兩個半部:上半部和下半部。上半部完成盡可能少的比較緊急的功能,下半部用來完成中斷事件的絕大部分任務。因為中斷的耗時工作在這里完成,所以將讀取數據放在下半部完成。Linux系統實現下半部采用的機制主要有tasklet、工作隊列和軟中斷。許多設備涉及到中斷操作,因此,在這樣的設備的驅動程序中需要對硬件產生的中斷請求提供中斷服務程序。與注冊基本入口點一樣,驅動程序也要請求內核將特定的中斷請求和中斷服務程序聯系在一起。在Linux中,用request_irq()函數來實現請求:

int request_irq(unsigned intirq,void(*handler)int,unsigned longtype,char*name);

參數irq為要中斷請求號,參數handler為指向中斷服務程序的指針,參數type用來確定是正常中斷還是快速中斷(正常中斷指中斷服務子程序返回后,內核可以執行調度程序來確定將運行哪一個進程;而快速中斷是指中斷服務子程序返回后,立即執行被中斷程序,正常中斷type取值為0,快速中斷type取值為SA_INTERRUPT),參數name是設備驅動程序的名稱。

我們的中斷處理函數是:

void fpgalc12_interrupt(int irq,void*dev_id,struct pt_regs*regs)。

Irqflags是中斷處理的屬性,若設置了SA_INTERRUPT,則表示中斷處理程序是快速處理程序,快速處理程序被調用時屏蔽所有中斷,而慢速處理程序不屏蔽。dev_id在中斷共享時會用到,一般設置為這個設備的結構體或NULL.request_irq()返回0表示成功,返回-INVAL表示中斷號無效或處理函數指針為NULL,返回-EBUSY表示中斷已經被占用且不能共享。這兩個函數分別要在初始化和釋放模塊中加載。

要在Linux申請了中斷通道后,系統會響應外部中斷IRQ_EINT0,從而進入中斷處理序。中斷處理程序功能就是將有關中斷接收的信息反饋給設備,并根據要服務的中斷的不同含義相應地對數據進行讀寫[7-8]。所以FPGA中斷處理的主要任務是:FIFO在接收到AD轉換來的數據后,向ARM發出中斷請求信號,讓ARM來讀取FPGA中FIFO狀態寄存器的值,獲取需要信息并安排接受數據,然后寫狀態寄存器清除相關中斷位以繼續響應中斷,保證數據的有效傳輸。

中斷處理程序的第一步是要先清除S3C2440A的中斷懸掛寄存器和中斷源寄存器相應的位。這是為了能夠繼續響應FPGA產生的中斷。為了能夠讓FIFO能及時的接收到新數據,把寫狀態寄存器放到中斷的一開始,即第二步就是寫狀態寄存器相應位,通過置1清除狀態使AD中斷能夠繼續產生。最后讀取FIFO的數據。使用中斷后數據的傳輸效率大大得到提高,能夠滿足實際的采集需要。

4.結束語

本方案中的采集板充分利用了ARM的靈活性和FPGA的并行性的特點,實現了適用于高速數據采集板的設計。方案采用S3C2440A作為主控芯片,通過千兆以太網接口實時地將采集的數據傳輸到上位機PC機,上位機可實時控制目標數據采集。FPGA芯片在控制A/D轉換芯片的同時,將數據存儲在SRAM中,并通過DMA接口與S3C2440A進行數據傳輸。實驗表明,本采集板的實時性和高速性能夠滿足系統的設計要求,可廣泛應用于各種數據采集系統中。

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:基于ARM和FPGA設計高速圖像數據采集傳輸系統

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602022

原文標題:基于ARM和FPGA設計高速圖像數據采集傳輸系統

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

利用ADS869X做一個隔離的高速數據采集系統,ADC需要一個時鐘信號,可以自己外接一個晶振電路嗎?

高速分切機數據采集監控告警系統解決方案

基于ARM和FPGA設計高速圖像數據采集傳輸系統

基于ARM和FPGA設計高速圖像數據采集傳輸系統

評論