點擊上方藍字關注我們

本文提出了一種新的包括PCI9054單周期讀、寫和存儲器映射傳輸的設計,并討論了通用PCI總線高速數據采集卡的實現方案。

PCI總線(Peripheral Component Interconnect)是Intel公司推出的一種高性能32/64位局部總線,最大數據傳輸速率為132~264MB/s,是目前使用較為廣泛的一種總線。在高速信號的實時處理中,利用PCI總線將采集數據直接傳送到微機系統內存,可有效解決數據的實時傳輸和存儲,為信號的實時處理提供方便。利用PCI總線進行高速數據采集,可以簡化電路設計,而且這種高速數據采集接口模塊可以在多次設計中重復使用,縮短產品的研發周期。在此通過對專用接口芯片PCI9054的性能分析,特別是對單周期讀、寫和存儲器映射傳輸操作的時序進行了分析,提出了一種新的包括PCI9054單周期讀、寫和存儲器映射傳輸的設計,并討論了通用PCI總線高速數據采集卡的實現方案。

1 PCI9054性能簡介

PCI9054是PLX公司推出的一種32位33 MHz的PCI總線控制器。它采用多種先進技術.可以將復雜的PCI接口應用設計變得簡單。利用PCI9054靈活的局部總線可以方便地連接多種存儲器、I/O外圍設備和CPU,其中包括與Motorola公司的MPC860和Intel公司的960和IBM公司的PPC401等處理器之間的直接連接。PCI9054可廣泛應用于Motorola公司的MPC 860適配器設計、Compact PCI熱交換適配器設計、PCI總線主控適配器和嵌入式主機等設計系統中。PCI9054的本地總線時鐘可與PCI總線時鐘異步,本地總線有三種工作模式:M模式、C模式和J模式,可方便地與多種微處理器連接。其中,在C模式下,本地總線(Local Bus)為非復用的32 b地址與數據總線,時序與控制比較簡單。PCI9054還有三種數據傳送方式,即PCI主發起、PCI從目標、DMA方式。PCI從目標即PCI9054作為PCI總線的從設備,由總線上的其他主設備向它傳送數據;在PCI9054的本地總線端,PCI9054又作為主設備,向本地的存儲空間和I/O空間傳送數據。在設計本地總線的數據傳送接口時,主要有兩項工作,一是需要對PCI空間到本地空間,或本地空間到PCI空間的地址映射,進行相應的存儲器配置;二是根據PCI9054提供的本地總線控制信號設計本地總線的邏輯控制功能,實現相應的數據傳送時序。

2 數據采集卡PCI接口電路設計

PCI總線規范定義了嚴格的電氣特性和時序要求,它要求在接口卡和終端設備之間有一個總線接口控制器,采用某些公司提供的專用接口芯片,如PLX公司的PCI9080,PCI9054和AMCC公司的S5933,S5920等。使用它只需要設計用戶接口邏輯和配置電路。大大減少了開發人員的工作量,且功能強,使用靈活。

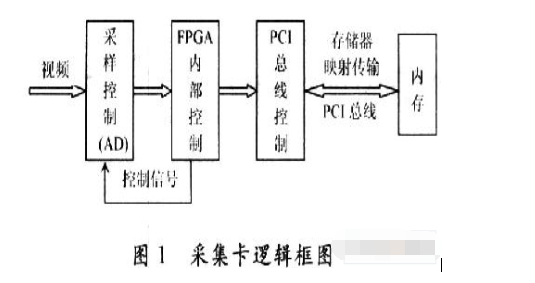

該設計采用PCI9054+FPGA實現高速數據傳輸接口。PCI9054能實現復雜的PCI總線規范2.2版,支持重要產品數據(VPD)配置,支持雙地址周期,可編程中斷生成,可編程突發管理,存儲器映射傳輸,具有可選的串行E2PROM接口,并支持Compact PCI和熱交換功能,性能卓越,使用方便。FPGA用來配合PCI9054的Local總線控制信號,實現Local總線端的數據傳送。E2PROM接口直接連接一個E2PROM來初始化配置PCI9054。整個板卡的邏輯結構框圖如圖1所示。

2.1 FPGA內部控制

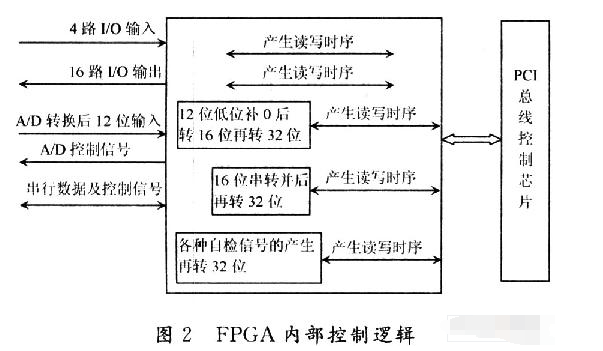

采樣控制電路主要完成視頻信號和動目標信號采樣,并對采樣值進行處理。設計的FPGA采用Altera公司的FLEX系列中的EPF1OK20芯片,并采用該公司與之配套的配置設備EPC2芯片來完成采樣后的數據處理。在FPGA內部,根據由網絡傳過來高低、方位及自定義的差分信號傳送時鐘、串行幀同步、串行數據、模式字,對采樣數據進行相關處理和小目標的放大。當信號小于一定值,則認為沒有信號;信號值落在某一區間,為了觀察方便要將其放大。FPGA同時完成各種自檢信號的產生、A/D的控制信號、以及各種讀寫時序。Local總線與外部的I/O部分,用鎖存器(如74F574)接口數據通路,用雙向通路(如74LS245)接口控制信號線。具體框圖如圖2所示。

2.2 存儲器映射傳輸

基于PCI9054的存儲器映射傳輸是核心部分。根據配置寄存器配置的Local總線三個空間的大小以及三個空間的基地址,把數據寫到相應的存儲空間。計算機操作系統識別板卡正確后,自動分配存儲空間給本卡,應用軟件應用計算機自動分配的存儲空間進行編程,完成所需要的功能。REQ,GNT,LHOLD,LHOL-DA為PCI BUS和LocaI BUS的仲裁信號,IRDY和TRDY分別為主設備準備好信號和從設備準備好信號,當兩者同時有效時,才能真正進行數據傳輸。板卡復位或上電時,PCI9054自動裝載E2PROM中的配置信息,同時EPC2自動配置EPF10K20,即裝載程序入FP-GA。芯片PCI9054已經整合了PCI協議,實現了PCI總線的接口。整個板卡設計的關鍵工作就在于FPGA程序的設計、PCI9054的配置和板卡驅動程序的編寫。PCI9054的正確配置是其正常工作的關鍵,PC操作系統在開機掃描總線時,正確的配置信息使操作系統正確識別板卡,并提示安裝驅動程序。如果配置不正確或不完整,則操作系統將找不到板卡,并且可能死機。單靠硬件無法將數據送到內存供顯示讀數設備所用,設備驅動程序是連接到板卡的軟件接口。該設計中,設備驅動程序的基本功能就是完成設備的初始化,對端口的讀寫操作,對中斷的設置、響應和調用,以及對內存和接口設備存儲器空間的直接讀寫。這里選用的驅動程序開發工具是Windrive。Windrive與DDK和VtoolsD相比,適應面比較窄,但是它主要針對ISA/PCI插卡,還包含一個代碼生成器Windrive Wizward和針對于PCI9054的函數,所以開發比較簡單,周期比較短。文獻[4,5]在設計驅動程序之前,對欲控制的硬件設備進行了細致的分析,詳細了解硬件設備的特性。硬件設備的特性對驅動程序設計會產生重大的影響。需要了解的最主要特性有:

設備的總線結構,該設計中即PCI總線;

寄存器,該設計中即配置的PCI9054寄存器的值;

設備的錯誤和狀態,了解如何判斷設備的狀態和錯誤信號,通過驅動程序返回給用戶程序;

中斷行為,了解設備產生中斷的條件和使用中斷的數量;

數據傳輸機制,是I/O傳輸、DMA傳輸,還是存儲器映射傳輸;

設備內存,RAM的容量,與系統總線(PCI)對應的基地址和范圍。

3 寄存器配置

設計好接口連接,接口設計工作只完成了50%。由于PCI9054是通用PCI接口功能芯片,它的功能還不一定能夠滿足用戶的需求,所以還要進行功能寄存器設置,以使接口電路具有特定的功能。寄存器的配置包括E2PROM初始化,以及Local功能寄存器和PCI配置寄存器的配置。

3.1 E2PROM初始化

在計算機的加電自檢期間,PCI總線的RST信號復位,PCI9054內部寄存器的默認值作為回應。PCI9054輸出本地LRESET信號并檢測串行E2PROM。如果串行E2PROM中的前33個比特不全為1,那么PCI9054確定串行E2PROM為非空,用戶可通過向9054的寄存器CNTRL的CNTRL29位寫1來加載E2PROM的內容到PCI9054的內部寄存器,配置的信息(設備識別號,供應商代碼號,Local總線三個空間的大小以及三個空間的基地址等)事先要利用編程寫入配置寄存器中。

3.2 PCI配置寄存器的配置

配置PCI配置寄存器比較簡單。主要是填寫生產商ID號、器件ID號、類碼子系統ID號和子系統生產商ID號。對于PCI9054,其生產商ID號為10B5,器件ID號為9054,子系統號ID為9054,子系統ID號為10B5,類碼號為0680,表示其為橋設備中的其他橋設備類。

3.3 本地配置寄存器的配置

對于本地配置寄存器的配置就是對本地地址空間及其本地總線屬性的配置。這些配置是根據實際開發的硬件板卡的硬件資源進行配置。設備人員配置寄存器的任務就是要把某一段本地地址應設為PCI地址。也就是當主機CPU要訪問本地地址空間時,要知道其對應的PCI總線地址。

4 電路板實現與測試

PCI規范對擴展板的機械和電氣方面都有一系列的規范要求。在布板和繪圖的過程中需要特別注意一些技術要求,布出來的板子工作起來才會穩定可靠。如:除了PCI協議中的信號線外,連接器本身的信號引腳值得注意,如板卡存在信號PRSNT1和PRSNT2;電源的退耦、PCI協議信號線的走線長度限制和擴展板上信號線的負載要求等都是在布板過程中特別應該重視的,都要滿足PCI電氣規范的要求。

該設計中嚴格按照規范要求設計,PCI連接器上的PRSNT1而開路,PRSNT2接地,表示本板卡的最大功耗為15 W。元件的退耦電容采用0.1μF,電源的濾波電容采用10μF的電解電容。采用存儲器映射的傳輸方式,本地時鐘采用20 MHz時,通過測試,傳輸速率能夠達到20 MB/s以上,提高本地時鐘的頻率,數據傳輸率還能夠更高。

5 結 語

這里實現的PCI數據傳輸接口,有效地解決了系統的數據傳輸問題,有利于數據的實時處理,獲得了比較滿意的效果。隨著信號處理技術的發展,這種基于PCI的數據傳輸接口有著十分廣闊的應用前景。

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:基于PCI總線的雷達視頻高速數據采集接口設計?

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602037

原文標題:基于PCI總線的雷達視頻高速數據采集接口設計?

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCIe接口的工作原理 PCIe與PCI的區別

通過PLX PCI9080橋接芯片實現TMS320C6000擴展總線與PCI總線的接口

YXC差分振蕩器賦能數據采集卡,讓數據更精準!

NI數據采集板卡如何連接使用?

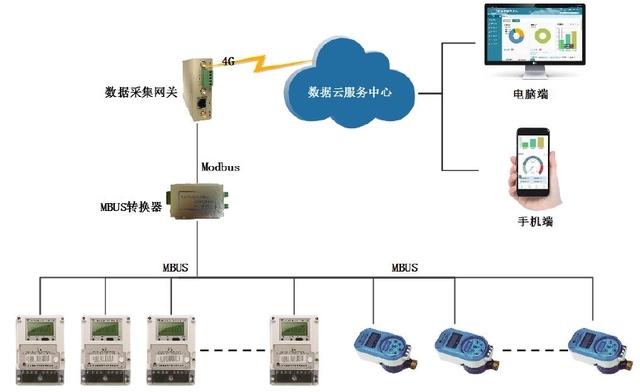

基于物通博聯工業數據采集網關的工廠數據采集方案

基于PCI總線的雷達視頻高速數據采集接口設計?

基于PCI總線的雷達視頻高速數據采集接口設計?

評論