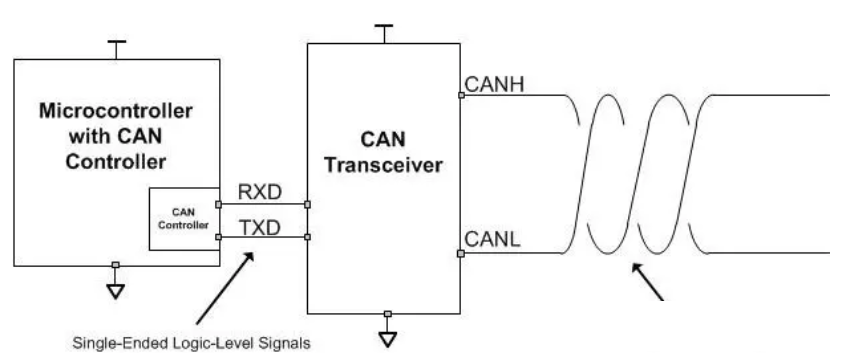

我們先從基礎(chǔ)的講起。CAN節(jié)點的電路一般如下圖所示,MCU內(nèi)置了CAN控制器用來將MCU的數(shù)據(jù)封裝為CAN幀格式,同時它也負(fù)責(zé)CAN幀的校驗和錯誤幀的處理。

控制器封裝好的邏輯報文經(jīng)TX RX送到CAN收發(fā)器,將邏輯信號轉(zhuǎn)變?yōu)檎嬲目偩€差分波形。

一、CAN物理層

也就是CAN收發(fā)器干了啥?

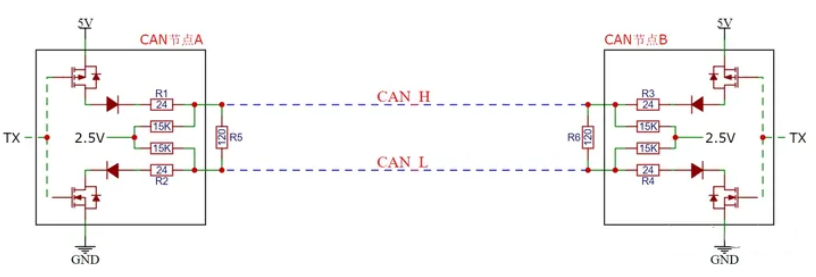

一個典型的雙節(jié)點CAN網(wǎng)絡(luò)的物理層等效電路如上圖,兩顆120Ω終端電阻并聯(lián)呈現(xiàn)總線電阻60Ω。黑框里是A、B兩個節(jié)點的CAN收發(fā)器(Transceiver),它只負(fù)責(zé)電平轉(zhuǎn)換。當(dāng)總線靜默時,收發(fā)器內(nèi)部的2.5V電源經(jīng)15KΩ電阻把CAN-H和CAN-L都拉到2.5V,總線這個狀態(tài)稱之為隱性。

當(dāng)節(jié)點A想要驅(qū)動總線的時候(TX=0),它同時把內(nèi)部的上下兩個MOS管導(dǎo)通,整個網(wǎng)絡(luò)的電流流向:節(jié)點A的5V電源經(jīng)二極管、24Ω、兩顆終端電阻并聯(lián)、24Ω、二極管回到節(jié)點A的地,總線這個狀態(tài)稱之為顯性。CAN總線上的電壓實際上就是終端電阻的分壓。

從節(jié)點B來看,CAN-H就變成3.5V,CAN-L變成1.5V,拉出了總線 H - L = 2V 的差分電壓,大于0.7V的判斷閾值,節(jié)點B就認(rèn)為收到了一個顯性(RX=0)。大家可以算一下分壓值以增強記憶,后邊會用到。

反直覺知識點①:總線無人驅(qū)動時,也就是各個節(jié)點都隱性時,CAN標(biāo)準(zhǔn)定義這時的TX/RX邏輯電平為1;總線有節(jié)點驅(qū)動顯性,也就是主動拉開差分電壓的時候,對應(yīng)TX/RX端邏輯電平0,這個1/0的反邏輯類似I2C等OC門的驅(qū)動邏輯,努力適應(yīng)一下。這么做我猜有兩個原因:一是對地邏輯的抗擾能力強一些,NPN載流能力強&回流路徑短;二是為了數(shù)學(xué)上的嚴(yán)謹(jǐn)性:1x1x1x1...1x0 = 0,任意節(jié)點驅(qū)動顯性0,那總線就是顯性0;所有節(jié)點隱性1,總線才是隱性1。但這樣的反邏輯帶來一個問題是,電路設(shè)計時需要尤其注意上下電時序,上電/休眠/喚醒過程中千萬不要出現(xiàn)MCU已下電(TX拉低)但CAN收發(fā)器還供5V電的情況。如果實在難以避免,可以試試單3.3V的CAN收發(fā)器MAX3051,它不需要5V電源,邏輯電和驅(qū)動電共用同一路3.3V,肯定不會出現(xiàn)電源時序問題。

反直覺知識點②:理論上CAN_L短地,或 CAN_H短路12V,因60Ω終端電阻的存在,隱性時CAN-H與CAN-L之間基本還是重合的,顯性時也能正常拉開壓差,能維持正常通信,只不過丟包率可能會大一點。大家可以算算總線電壓,示波器很容易診斷這個問題。另外,如果你看到CAN的通信電壓不是以2.5V為中心對稱的,也有可能是多個CAN線交叉錯接,比如CAN1_L錯接到了CAN2_L上。

反直覺知識點③:一個CAN網(wǎng)絡(luò)里,120Ω終端電阻1~4顆都能工作,少了的話 離終端電阻遠(yuǎn)的節(jié)點 抗擾度會差,多了的話 顯性差分電壓可能無法觸發(fā)閾值。

反直覺知識點④:除了線路的最遠(yuǎn)端,任何稍長的CAN分支都可以加1K~4.7K的支線電阻,跑點電流來改善抗擾度。只要分支別太長,大致1Mbps以內(nèi)的任何總線其終端電阻都是跑電流增強抗擾的,不涉及真正的阻抗或者反射抑制,雙絞的要求也不是特別嚴(yán)格。

二、CAN鏈路層

也就是CAN控制器干了啥?

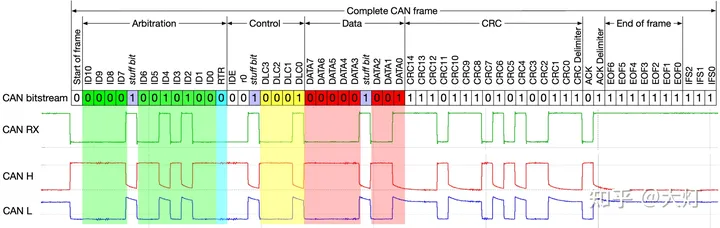

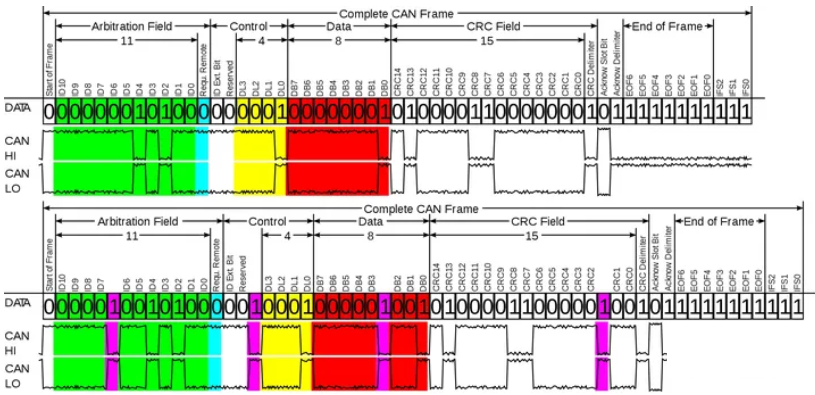

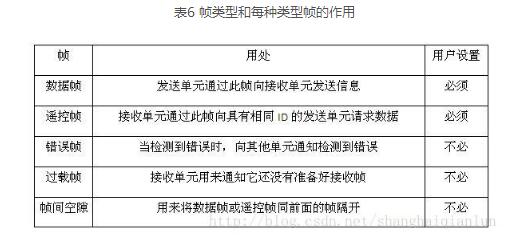

回顧完物理層,咱來看鏈路層,CAN幀的標(biāo)準(zhǔn)格式。當(dāng)發(fā)送節(jié)的MCU將TX由1變0的時候,CAN收發(fā)器將CAN-H拉高&CAN-L拉低,接收節(jié)點收到了H-L>0.7V的壓差后,接收節(jié)點的CAN收發(fā)器RX輸出由1變0。下圖是一個節(jié)點接收到CAN波形后解碼出的RX邏輯。

一幀報文里邊有比較關(guān)鍵的幾段:仲裁段、控制段 、 數(shù)據(jù)段、CRC段、ACK段。

仲裁段中的大部分是CAN報文的ID,起名為“仲裁”其實是因為這一段有優(yōu)先級仲裁的功能:假設(shè)A、B兩個節(jié)點在同一時刻搶發(fā)報文,節(jié)點A要發(fā)二進制ID為001的報文,B要發(fā)010。當(dāng)A、B節(jié)點都在發(fā)第一位的顯性0的時候,總線會同時被兩個節(jié)點驅(qū)動顯性,A、B節(jié)點回讀總線也都是顯性,相互之間還意識不到對方的存在。當(dāng)節(jié)點A發(fā)到第二位的0,節(jié)點B發(fā)到第二位的1的時候,總線只有節(jié)點A驅(qū)動顯性0,節(jié)點B不驅(qū)動 卻發(fā)現(xiàn)總線被別人驅(qū)動了,此時節(jié)點B會認(rèn)為CAN線上有比自己這幀010優(yōu)先級更高的數(shù)據(jù),節(jié)點B就會主動停發(fā),讓節(jié)點A獨占總線發(fā)完。之后節(jié)點B懷揣著這幀數(shù)據(jù)再次參與總線優(yōu)先級的仲裁。

反直覺知識點①:CAN作為一個對等網(wǎng)絡(luò),沒有主從關(guān)系,報文全部廣播,節(jié)點本身也沒有優(yōu)先級概念,只有報文ID的優(yōu)先級。可以這么理解:CAN節(jié)點是“由事件驅(qū)動的”,比如剎車制動器,它能發(fā)高優(yōu)先級的“剎車被踩下”的報文,也會發(fā)低優(yōu)先級的“剎車油位正常”的報文,這些報文根據(jù)ID的大小在總線上自由競爭優(yōu)先級,而不是剎車制動器這個節(jié)點的話語權(quán)一定高。這個特性就要求設(shè)計人員提前規(guī)劃好所有報文優(yōu)先級和周期(即“通信矩陣”)才能保證整個CAN網(wǎng)絡(luò)如期運轉(zhuǎn)。如果你的CAN網(wǎng)絡(luò)有大量雷同節(jié)點,節(jié)點又只有一幀報文,那么ID數(shù)大(優(yōu)先級低)的節(jié)點一定會在總線繁忙或干擾重發(fā)的時候"插不上話",可以試試把時間戳融合到ID里邊,確保各節(jié)點的新數(shù)據(jù)優(yōu)先級最高,舊數(shù)據(jù)自然會被仲裁掉。

反直覺知識點②:在A、B節(jié)點同時驅(qū)動第一個顯性0的時候,總線被兩個節(jié)點同時驅(qū)動,電壓會顯著高于2V。示波器上會看到在仲裁段的頭部有明顯的電平凸臺,后續(xù)節(jié)點A搶占總線之后電壓會回歸正常的2V。

反直覺知識點③:各個節(jié)點的時鐘同步是把每個bit做16~20份的數(shù)字切片來實現(xiàn)的,這個切的份數(shù)不建議太多或太少。詳細(xì)機制請參閱 ZLG致遠(yuǎn)電子的這篇:CAN同步機制,你真的了解嗎?

控制段中有幾個控制位,這里拿幾個常用的舉例。IDE位為擴展ID的指示。如果IDE位為隱性1,就會在后邊再續(xù)上18位的ID,共11+18=29位長度。比如0x9E就是個11位長度的ID,0x0151就是個29位的ID。R0位是CAN里邊的預(yù)留位,在CAN-FD里被用作FD幀格式的標(biāo)志位FDF,這一位為隱性1就會按FD的幀格式解碼后續(xù)報文。DLC指示了后邊的數(shù)據(jù)段的長度,例如1000表示后續(xù)會有8個Byte長度的數(shù)據(jù)。CAN-FD協(xié)議只在數(shù)據(jù)段會切換成高速率,比如2Mbps/8Mbps,前后其他段的速率保持500kbps不變。

反直覺知識點①:CAN與CAN-FD除了數(shù)據(jù)段波特率的不同,幀格式也有區(qū)別,CAN-FD多了一些控制位。比如FDF(也叫EDL)位用來指示是否按FD幀格式解碼,BRS位用來指示是否需要切換高波特率,也就是說,一個FD幀可以全程500kbps不切速率的。

反直覺知識點②:CAN控制器的標(biāo)準(zhǔn)ISO11898-1里要求接收方不解讀R0位的顯隱性,所以CAN的控制器無法過濾FD幀。標(biāo)準(zhǔn)CAN網(wǎng)絡(luò)里邊一旦出現(xiàn)FD幀會因為多了BRS、ESI等控制位被認(rèn)為是格式錯誤。同樣的,因為CAN 2.0時代R0/FDF幀無意義,也有一些設(shè)備把發(fā)送出去的CAN幀的R0位錯誤地置了隱性1,這樣的設(shè)備在CAN網(wǎng)絡(luò)里一切正常,但若進入CAN-FD網(wǎng)絡(luò)就會被解讀成FD幀,進而因為缺少BRS、ESI等控制位被認(rèn)為是格式錯誤。所以,CAN-FD并不是真的向下兼容CAN,因為舊時代的CAN設(shè)備并沒有判別R0/FDF位的能力,一旦它進入FD網(wǎng)絡(luò)就會瘋狂地打斷通信。

反直覺知識點③:DLC的長度,在CAN標(biāo)準(zhǔn)里DLC可以是0000~1000之間的二進制值,可以用8421的算法直接計算出數(shù)據(jù)長度。而在CAN-FD中,1001~1111之間的值則被解讀為離散的12,16,20,24,32,48,64byte。

CRC段對于從幀頭到Data結(jié)束之間的數(shù)據(jù),CAN協(xié)議使用了CRC15這個比較特別的多項式計算校驗,有興趣的可以手算CRC試試。CAN-FD根據(jù)數(shù)據(jù)長度的不同使用了CRC17和CRC21,這里暫不做展開。

ACK段是由收到該幀的CAN節(jié)點回復(fù)的確認(rèn)(Acknowledge)。注意 發(fā)送節(jié)點在ACK位一定發(fā)的是隱性1,由接收節(jié)點回應(yīng)顯性0,雙方無縫銜接才在總線上呈現(xiàn)出一個完整的CAN報文。

反直覺知識點①:總線上任何節(jié)點 只要認(rèn)為這個幀的結(jié)構(gòu)正確,都會在ACK位回顯性0,不管需不需要這一幀的ID和數(shù)據(jù)。為什么不需要的節(jié)點也會回ACK?因為等MCU算完會造成這一位的延遲,攪亂總線時序,不如只保障鏈路層本身的格式正確,純芯片數(shù)字邏輯實現(xiàn)無延遲。嗯,90年代的總線要求不要太高。

反直覺知識點②:發(fā)送節(jié)點若發(fā)現(xiàn)自己這一幀沒有ACK回應(yīng),它也會認(rèn)為總線出錯,重發(fā)16次后進入Passive error狀態(tài),有興趣的自行研究一下,這里不做展開。

三、真實CAN波形

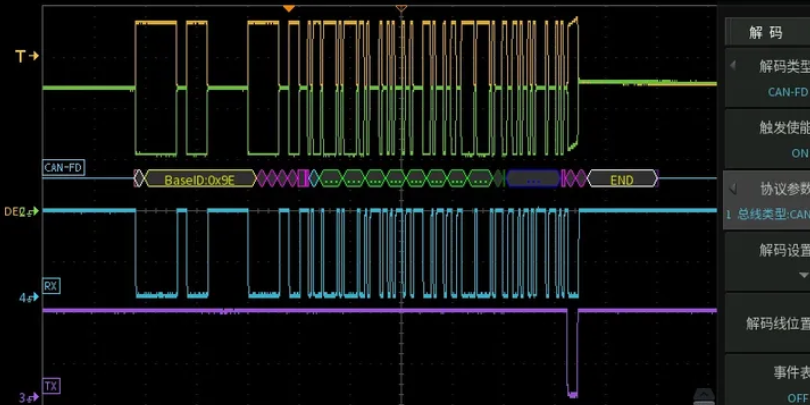

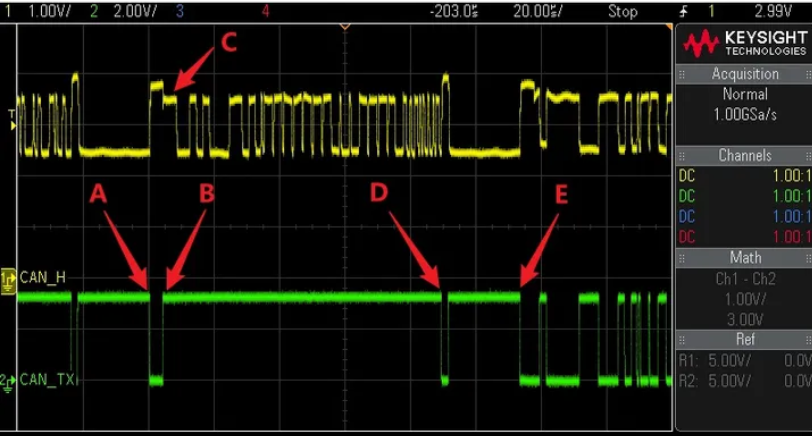

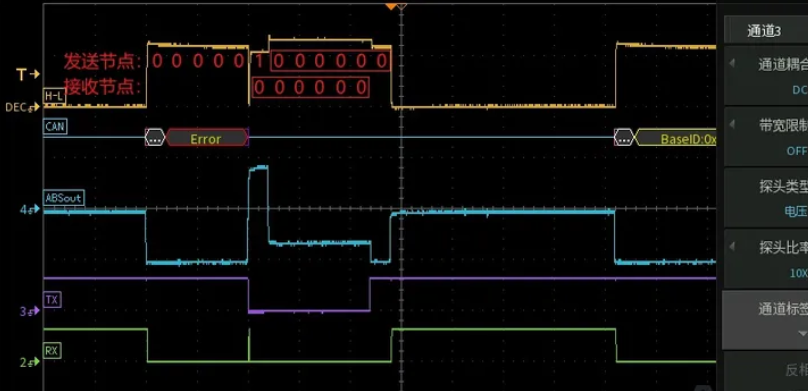

來看一個兩節(jié)點案例:若節(jié)點A發(fā)送0x9E報文到總線,從節(jié)點B收到的總線波形和邏輯側(cè)波形如下:

黃線為CAN-H,綠線為CAN-L,藍(lán)線為節(jié)點B的邏輯側(cè)RX,紫線為節(jié)點B的邏輯側(cè)TX。可以看到,作為接收方的節(jié)點B,總線拉差分電壓拉出顯性的時候,收發(fā)器將RX拉0給到MCU。在節(jié)點B想要回應(yīng)ACK的時候,MCU將TX拉0,CAN收發(fā)器在總線上拉出了一個歪斜的顯性(歪斜是因為測量點的寄生電感影響)。RX在ACK位置的0,是收發(fā)器TX=0驅(qū)動總線顯性之后 回讀到的0。

再看一個比較真實的車上波形,CAN網(wǎng)絡(luò)上大于4個節(jié)點:

黃色是CAN_H,高電平表示顯性0,綠色是我們掛示波器這個節(jié)點的邏輯側(cè)TX,低電平表示顯性0。箭頭A~D是一幀完整的CAN報文,箭頭A ~ B這個過程中,我們掛示波器的這個節(jié)點和另一個節(jié)點正在進行優(yōu)先級仲裁,根據(jù)我們之前講到的物理層的分壓原理,兩個節(jié)點同時驅(qū)動電壓會高一截。在箭頭C這個bit 該節(jié)點想發(fā)隱性1但發(fā)現(xiàn)總線是顯性0,那就說明有另外的節(jié)點在發(fā)送更高優(yōu)先級的報文,我們這個節(jié)點會主動退出發(fā)送,成為接收節(jié)點,并在箭頭D點校驗成功后回應(yīng)ACK,等待報文結(jié)束后這個節(jié)點再次參與總線仲裁,成功搶占總線如E點所示。

注意波形高度,在箭頭A~B之間,差分電壓略高于2V,這是正常現(xiàn)象,說明有兩個節(jié)點同時驅(qū)動總線顯性,但從邏輯看,因為H-L>0.7V所以都為顯性0,純數(shù)字邏輯的CAN控制器在箭頭A~B之間還感知不到對方的存在,箭頭C點之后才感知得到;而在箭頭D點,因為除了發(fā)送節(jié)點之外的所有節(jié)點都在同時驅(qū)動ACK,所以總線電壓比箭頭A~B之間的雙節(jié)點驅(qū)動 電壓更高。

四、錯誤幀

終于到了錯誤幀,注意,錯誤幀不是由哪個節(jié)點發(fā)出的,而是由某個接收節(jié)點認(rèn)為總線錯誤,才故意驅(qū)動總線打斷發(fā)送方,在總線上呈現(xiàn)為一個錯誤幀。也就是說錯誤幀 一定是由 一個發(fā)送節(jié)點和至少一個 認(rèn)為發(fā)送方有錯的節(jié)點 共同形成的。

五、位填充

位填充規(guī)則是CAN協(xié)議的靈魂,簡單來講就幾個字:逢五補一。當(dāng)發(fā)送節(jié)點想要發(fā)連續(xù)5個bit的顯性0的數(shù)據(jù),會故意插入一個無意義的隱性1;當(dāng)出現(xiàn)連續(xù)5個bit的隱性1,會故意插入一個無意義的顯性0,如下圖的紫色bit。如果發(fā)送節(jié)點漏填了這個0/1,或者這個0/1被干擾成了1/0,接收節(jié)點就會判定為“填充錯誤”,向總線上輸出“主動錯誤標(biāo)志”——連續(xù)六個顯性0,故意破壞這一幀報文,發(fā)送節(jié)點感知到總線錯誤之后停止發(fā)送這一報文的后續(xù)部分。你說巧妙不巧妙?連續(xù)6個顯性0本身就是破壞“逢五補一”規(guī)則的,被拿來當(dāng)錯誤標(biāo)志回給發(fā)送節(jié)點。

假如原始數(shù)據(jù)是0x00,二進制0000 0000,發(fā)送節(jié)點發(fā)到0000 0的時候發(fā)送節(jié)點會先插一個1,再發(fā)后續(xù)的000,成為0000 01000,共9bit長度,接收節(jié)點也會在第5bit的0之后預(yù)期一個無效的1,解碼時摳掉。

假如原始數(shù)據(jù)是0000 0100,第六位自帶1,發(fā)送節(jié)點發(fā)到00000的時候也會先插一個1,再發(fā)后續(xù)的100,成為0000 01100,共9bit長度。

六、回讀確認(rèn)

發(fā)送節(jié)點發(fā)送了0或1的時候,會回讀確認(rèn)總線是否和自己的發(fā)送相符,比如在仲裁段搶優(yōu)先級失敗就會等下一幀再發(fā);如果發(fā)到了數(shù)據(jù)段,按理說此時總線應(yīng)該只有自己,發(fā)著發(fā)著突然發(fā)現(xiàn)回讀的0/1與自己發(fā)的不同,比如受到了干擾,發(fā)送節(jié)點就會輸出“主動錯誤標(biāo)志”——連續(xù)6bit顯性0,來主動拋棄后續(xù)報文,同時讓接收節(jié)點知道我這一幀有誤。

在這時,接收節(jié)點收到第6bit顯性0的時候,因違背逢五補一的位填充規(guī)則,也會往總線上輸出“主動錯誤標(biāo)志”,所以會在總線上看到連續(xù)12bit的顯性0,前6個來自發(fā)送節(jié)點,后6個來自接收節(jié)點。

正常情況來說,總線上的顯性不應(yīng)該>5bits=10us。那么用示波器設(shè)置>11us的脈寬觸發(fā)模式就很容易定位錯誤幀的位置,不一定要用解碼示波器。

七、升維打擊

CAN網(wǎng)絡(luò)的幅度和電流可以為我們提供更多維度的信息,此所謂升維打擊。

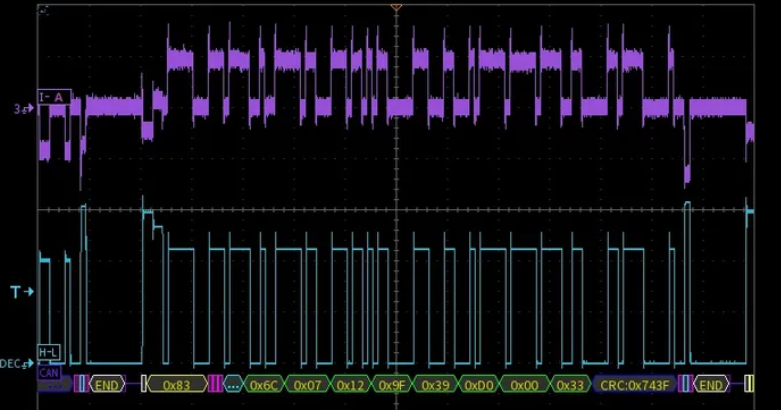

我們先來看一個正常幀,我們叫它節(jié)點A吧,它內(nèi)部有終端電阻,藍(lán)線為H-L的差分電壓,紫線是我們節(jié)點A的CAN-H引腳電流,輸出為正,輸入為負(fù)。

先看藍(lán)色的總線電壓波形,從0x83到END之間是一幀正常波形,注意看幀頭有多級臺階,幀尾ACK位置也特別高,這是正常的,可以理解 當(dāng)多個節(jié)點同時驅(qū)動總線就會導(dǎo)致60Ω終端電阻上的分壓高于2V。從這些臺階來看,可以判斷出網(wǎng)絡(luò)上至少有5個節(jié)點。

為啥?先看報文中部的幅度,這肯定是只有一個節(jié)點搶占總線之后的波形,往前有兩級臺階,可以認(rèn)為A、B、C三個節(jié)點同時搶占總線出現(xiàn)了第一個高臺,然后節(jié)點C優(yōu)先級仲裁失敗退出總線,A、B節(jié)點繼續(xù)搶占出現(xiàn)了第二個臺階,之后節(jié)點A成功搶占到了總線優(yōu)先級,發(fā)送中間的數(shù)據(jù)。最后的ACK位比3節(jié)點驅(qū)動的第一個bit更高,說明至少有4個節(jié)點在驅(qū)動ACK,再加上節(jié)點A,網(wǎng)絡(luò)上至少有5個節(jié)點。

再看紫色的電流波形,已知節(jié)點A自己有終端電阻,外邊有另一顆終端電阻。波形中部的數(shù)據(jù)區(qū)肯定是節(jié)點A在驅(qū)動總線,差分電壓流經(jīng)外邊的終端電阻形成回路,所以我們在節(jié)點A的引腳上觀察到了輸出的正向電流;往前一個電壓臺階的位置,電流為0,是A、B兩個帶終端電阻的節(jié)點在驅(qū)動總線,所以總線電壓拉開了但電流仍是無進無出的;再往前一個臺階,A、B、C三個節(jié)點驅(qū)動,節(jié)點C的電流流入A、B的終端電阻,所以在節(jié)點A的引腳上測到了輸入的負(fù)向電流;然后幀尾的ACK位置,至少有4個節(jié)點同時驅(qū)動,流入終端電阻A和B的負(fù)向電流更大了。

八、錯誤幀實戰(zhàn)

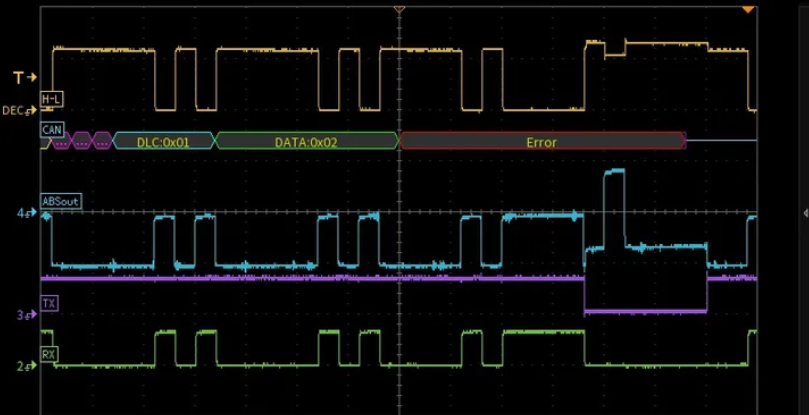

這是一個兩節(jié)點網(wǎng)絡(luò),一個節(jié)點發(fā),另一個節(jié)點收,兩方都有終端電阻,發(fā)送節(jié)點用的是TJA1042,接收節(jié)點用的是單3.3V收發(fā)器MAX3051。在幀頭就發(fā)生了錯誤,這種錯誤幀一般源于時鐘偏差或采樣點過小。

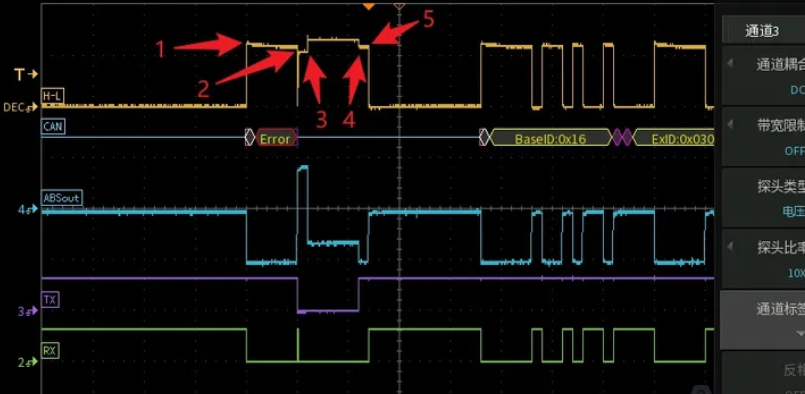

我們將示波器的差分探頭和電流探頭掛在接收端,下圖黃色為H-L的差分電壓,藍(lán)色為接收節(jié)點的輸出電流,RX為收發(fā)器將H-L差分電壓轉(zhuǎn)換出的邏輯波形,MCU內(nèi)部的CAN控制器會根據(jù)RX的0/1來解讀總線。TX為接收節(jié)點的發(fā)送邏輯,MCU將TX拉低的時候收發(fā)器會往總線上驅(qū)動顯性。

我們已知500kbps的每個bit寬2us,注意上圖紫線TX在2 ~ 4箭頭之間出現(xiàn)了連續(xù)2us * 6=12us的顯性0,說明我們掛示波器的這個接收節(jié)點在此刻往外輸出了一個“主動錯誤標(biāo)志”,那一定是接收節(jié)點在此之前認(rèn)為總線出現(xiàn)了錯誤。我們來往前看,箭頭1~2之間總線差分電壓和RX邏輯側(cè)都只有10us/2us=5bit的顯性0,幀前邊都是長隱性1,這能有什么錯?一個可能是我們碰到了傳說中的過載幀,這個東西本應(yīng)該很少見了;另一個可能是接收節(jié)點把對方來的正確報文認(rèn)成了錯的,這10us被接收節(jié)點認(rèn)成了6bit,錯誤的采樣點+硬同步(幀頭對齊)做得稀爛的國產(chǎn)MCU更容易出現(xiàn)這樣的幀頭報錯。

不管哪種,我們推演一下看看是否符合我們的理論,在箭頭2~3之間發(fā)送節(jié)點應(yīng)該是想發(fā)送一個隱性,但這時接收節(jié)點已經(jīng)覺得不對開始發(fā)“主動錯誤標(biāo)志”,將總線拉成了顯性。然后發(fā)送節(jié)點讀到這一bit自己想發(fā)送隱性但總線是顯性,所以。。。仲裁區(qū)搶優(yōu)先級失敗退出總線,,,怎么可能,之前有6個連續(xù)顯性呢,所以發(fā)送節(jié)點因違反“逢五補一”在箭頭3~5也輸出“主動錯誤標(biāo)志”。所以就成了黃色總線波形的7個bit的“凸”型,中間的凸臺的位置總線被兩個節(jié)點驅(qū)動,電壓高起一個臺階。

再注意一個細(xì)節(jié),凸臺的左肩膀和右肩膀高度不一樣,左肩膀是接收節(jié)點MAX3051驅(qū)動的電平,它比 右肩膀TJA1042的驅(qū)動能力弱一些,總線電平低一點。這個特性可以用來區(qū)分總線上的不同設(shè)備。

藍(lán)色線,是接收節(jié)點的輸出電流。箭頭1~2之間的負(fù)向電流為發(fā)送節(jié)點驅(qū)動總線,差分電壓流經(jīng)接收節(jié)點內(nèi)部的終端電阻帶來的負(fù)電流;箭頭2~3之間的正電流是接收節(jié)點驅(qū)動的主動錯誤的第一個bit;后邊3~4的凸臺兩個節(jié)點都在驅(qū)動顯性 但對應(yīng)的電流也是負(fù)的,這是因為發(fā)送節(jié)點的驅(qū)動能力強過接收節(jié)點,整個網(wǎng)絡(luò)電流還是由發(fā)送節(jié)點灌入接收節(jié)點;再往后4~5的負(fù)電流是發(fā)送端驅(qū)動接收節(jié)點的終端電阻的電流。

下圖我標(biāo)出了兩個節(jié)點的輸出bit流,紅框是“主動錯誤標(biāo)志”。

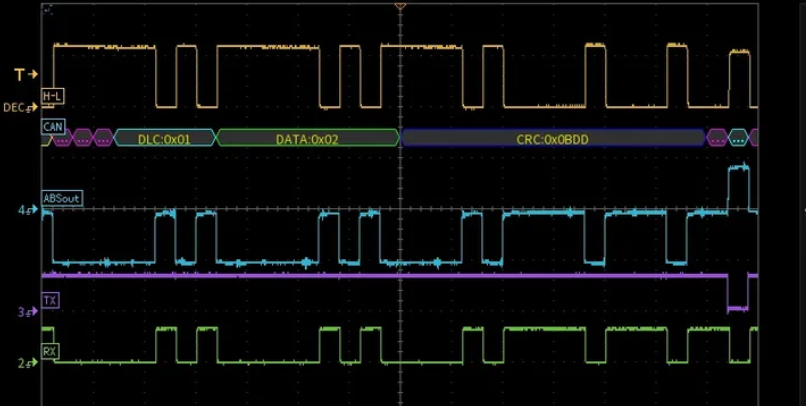

仍然是這個兩節(jié)點網(wǎng)絡(luò),仍然是這個稀爛的國產(chǎn)MCU,我們來看這個錯誤幀是怎么個情況:

這一幀的DLC=0x01,也就是只有1byte數(shù)據(jù),數(shù)據(jù)區(qū)之后就是CRC區(qū),我們的“主動錯誤標(biāo)志”就發(fā)生在這個區(qū),觀察又沒有填充錯誤,那就是我們掛示波器這個接收節(jié)點認(rèn)為發(fā)送節(jié)點出現(xiàn)了CRC錯誤。但我們看到黃線在“主動錯誤標(biāo)志”中間出現(xiàn)了凹坑,意味著發(fā)送節(jié)點還是想繼續(xù)發(fā)隱性,并不認(rèn)為自己有錯,直到發(fā)現(xiàn)這一位被“主動錯誤標(biāo)志”覆蓋為顯性才感知到位錯誤后拋棄后續(xù)報文。

原因最后定位到:過小的采樣點+過大的再同步補償寬度SJW讓時鐘誤差逐步積累,這顆國產(chǎn)MCU的重同步又做得稀爛,把正常報文錯讀了一位導(dǎo)致算CRC錯誤。最后通過調(diào)整采樣點和SJW寬度減少了這種錯誤的出現(xiàn)頻次,得到正常波形如下:

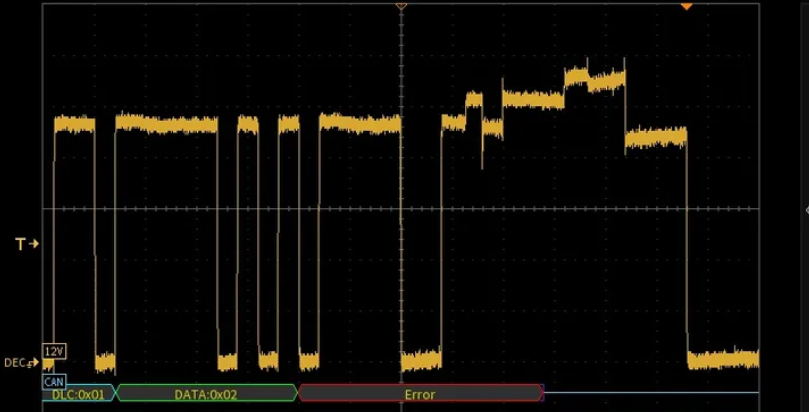

我們再試著從差分波形來分析一個錯誤幀:

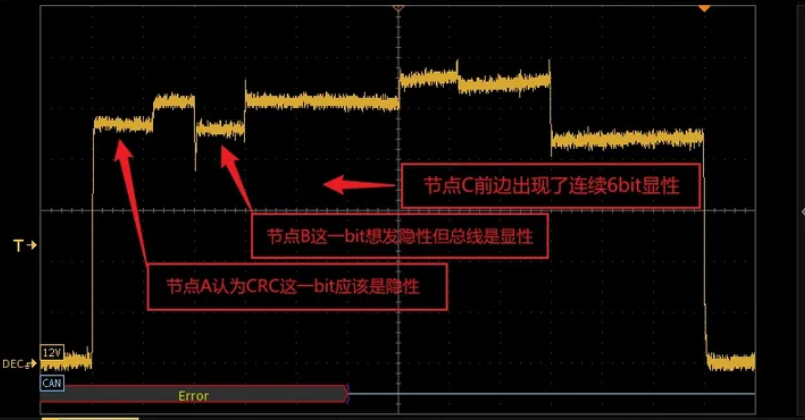

錯誤發(fā)生在CRC區(qū),我們放大一下,看看各節(jié)點都發(fā)生了啥:

從每一個臺階往前畫12us的方框,得到每個節(jié)點輸出的“主動錯誤標(biāo)志”,分析可知:這是一幀節(jié)點B發(fā)送的報文,節(jié)點A認(rèn)為它的CRC算錯了,節(jié)點C湊了個熱鬧,三者一起形成了這個12bits長的“主動錯誤標(biāo)志”。

那,節(jié)點A為什么會認(rèn)為CRC有錯呢?大概率是因為之前的數(shù)據(jù)讀錯了一位。

這么好的波形也能讀錯?是的,我們無法判斷節(jié)點A所在的位置波形有多差,可能分支上沒有終端電阻振鈴很大呢?我們只能相信節(jié)點A不會亂搞。另外,采樣點偏差會導(dǎo)致節(jié)點對噪聲額外地敏感。

九、CAN-FD錯誤排查

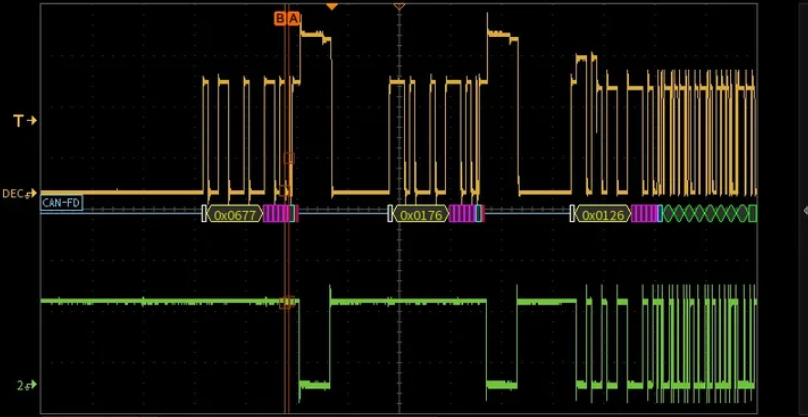

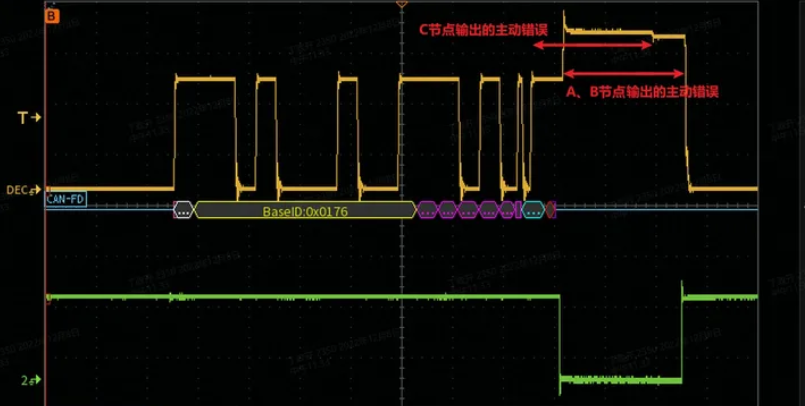

來看一個A B C三節(jié)點CAN-FD錯誤幀的案例,節(jié)點C發(fā),節(jié)點A、B收:黃色是H-L的差分電壓,綠色是節(jié)點B的邏輯TX。0x0677和0x0176是兩個錯誤幀。FD區(qū)波特率設(shè)置為2Mbps。

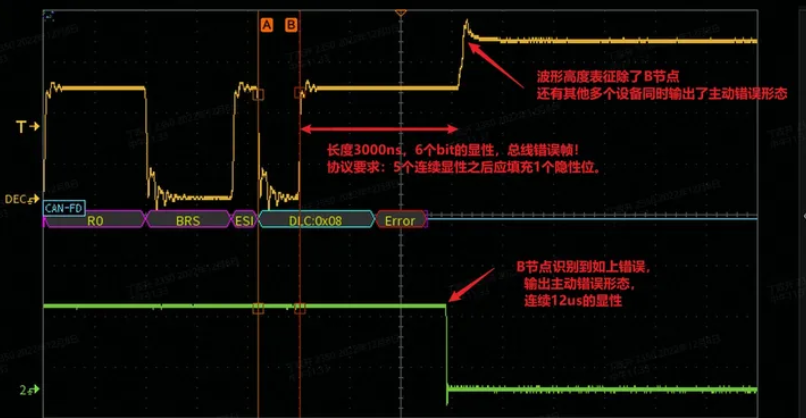

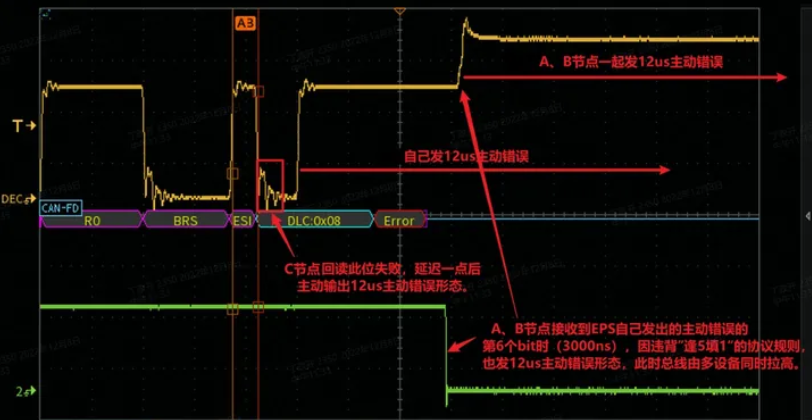

放大0x0176幀的細(xì)節(jié):

標(biāo)尺A B之間時間長度約0.8us,由一個2Mbps FD bit的0.5us + 一個CAN-FD的TDC(300ns)組成。

之后出現(xiàn)了6個FD bit(0.5us*6=3000ns)的連續(xù)顯性位,電平高度與之前相同,之后有連續(xù)2usx6=12us的顯性。

在標(biāo)尺B線后12us位置出現(xiàn)了一個電壓跌落的小小的下降臺階,見下下圖。

綜上三條,認(rèn)為節(jié)點C所在位置干擾過大/分支線路過長,節(jié)點C自己回讀↓下圖↓框出的bit位失敗,自己往總線上輸出“主動錯誤標(biāo)志”(連續(xù)6bit=2usx6=12us的顯性),其他設(shè)備在接收到第6個CAN-FD的bit=0.5usx6=3us的時候就讀到了錯誤(違反FD速率的“逢五補一”規(guī)則),也往總線上疊加2us*6=12us的主動錯誤標(biāo)志。然后,12us時節(jié)點C的主動錯誤標(biāo)志先結(jié)束,其他節(jié)點的主動錯誤在2usx6+0.5usx6=15us后結(jié)束。至此,錯誤幀形態(tài)完成。

“逢五補一”這條規(guī)則是跟隨波特率變化的,6個連續(xù)的高波特率0或1都會觸發(fā)填充錯誤。但填充錯誤之后輸出的“主動錯誤標(biāo)志”是500kbps波特率的6bit,固定長度12us。

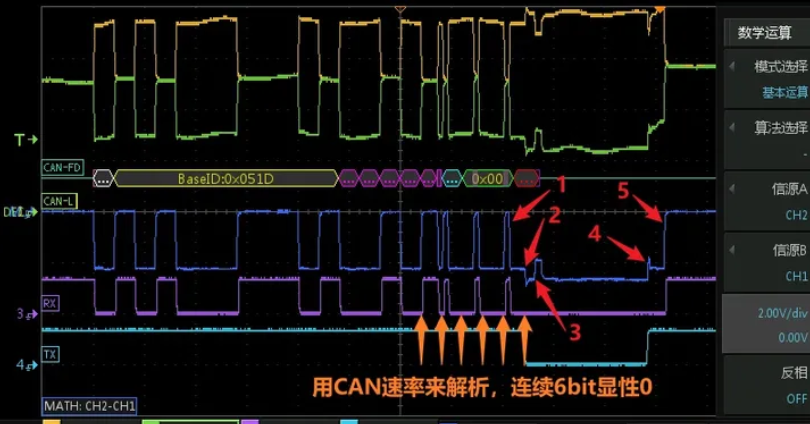

再來一個案例:CAN-FD采樣點設(shè)置出錯導(dǎo)致節(jié)點B把節(jié)點A發(fā)送的CAN-FD報文當(dāng)CAN來解析出錯。

黃色CAN_H,綠色CAN_L,藍(lán)色L-H反向差分電壓,紫線為節(jié)點B邏輯RX,青線為節(jié)點B邏輯TX。

注意看0x00前后的數(shù)據(jù)段,這一段是CAN-FD的2Mbps速率,節(jié)點B因為采樣點設(shè)置錯誤讀錯了BRS這一波特率轉(zhuǎn)換標(biāo)志,仍按照標(biāo)準(zhǔn)的500kbps去解析節(jié)點A的2Mbps速率的數(shù)據(jù),對RX信號2us一個采樣我用黃色箭頭標(biāo)出來了,可以看到這恰好是6個連續(xù)顯性0,違反“逢五補一”的規(guī)則,故而接收節(jié)點B在箭頭2~4之間發(fā)“主動錯誤標(biāo)志”,打斷總線通信,告知發(fā)送節(jié)點你發(fā)錯了。

箭頭2~3之間,發(fā)送節(jié)點A恰好也要發(fā)顯性,所以節(jié)點A此時還沒感覺到不對。

箭頭3之后,節(jié)點A想要拉隱性,電壓出現(xiàn)一個坑,卻發(fā)現(xiàn)總線還是顯性,此時節(jié)點A判斷出現(xiàn)了“位錯誤”,開始輸出“主動錯誤標(biāo)志”,想告知接收方放棄我這一幀報文。

箭頭4的位置節(jié)點B釋放“主動錯誤標(biāo)志”,箭頭5的位置節(jié)點A釋放“主動錯誤標(biāo)志”。

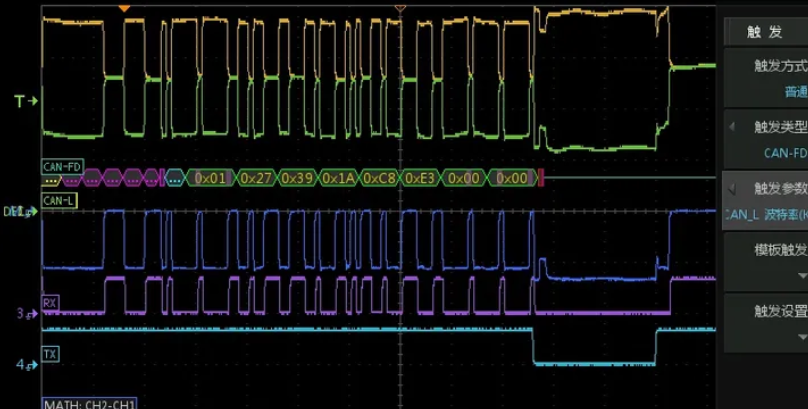

如果數(shù)據(jù)比較巧,恰好能滿足逢五補一的規(guī)則,那這種錯誤形態(tài)會在發(fā)送很多數(shù)據(jù)之后才會出現(xiàn),但最晚也會被CRC攔截:

補充知識:CAN-FD網(wǎng)絡(luò)各個節(jié)點的采樣點必須完全相同,高速率導(dǎo)致對時序敏感很多,這一點與CAN網(wǎng)絡(luò)容許一個范圍顯著不同。

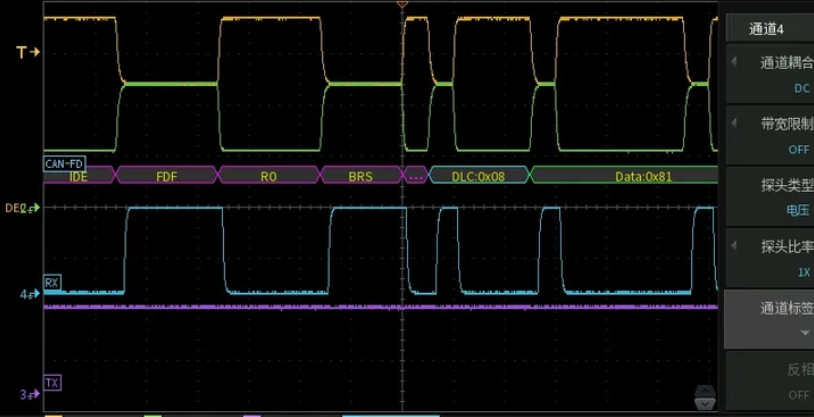

上邊這一幀的BRS位怎么讀錯的呢?再一次違反直覺:CAN-FD的采樣點影響發(fā)送節(jié)點的驅(qū)動波形!用示波器可以輕松量出FD的采樣點位置。

看下圖,CAN-FD報文的控制段中的BRS位(Bit Rate Switch)明顯是短于前邊的FDF、R0位的,采樣點不匹配的話很容易讀錯。因為-FD的速率翻轉(zhuǎn)是在這一bit的采樣點位置發(fā)生的。比如采樣點80%的2Mbps CAN-FD網(wǎng)絡(luò),BRS這一位的寬度為2us80%+0.5us20%=1.7us,而不是2us。接收節(jié)點的采樣點如果設(shè)置大于85%就會錯過整個BRS位(2us*85%=1.7us),從而導(dǎo)致如上的BRS位讀錯的問題。

以上,就是示波器升維破解CAN錯誤幀/BusOff的經(jīng)驗分享,總結(jié)一下:

結(jié)合已知ID是哪個節(jié)點發(fā)的先驗信息,逐個拔掉非終端節(jié)點,示波器觀察“主動錯誤標(biāo)志”,就能模糊定位錯誤源頭;

如果能引出敏感設(shè)備的TX,哪個節(jié)點認(rèn)為哪個節(jié)點出了什么錯就會非常清晰明了;

其次,測量CAN的輸出電流也能清楚地定位誰在驅(qū)動“錯誤標(biāo)志”,進而找到故障點;

如果上述難以實現(xiàn),以12us間隔拆分“錯誤標(biāo)志”的電壓臺階,也能定位大部分錯誤原因;

額外關(guān)注單bit寬度的電壓臺階,能排除部分節(jié)點;

審核編輯:劉清

-

二極管

+關(guān)注

關(guān)注

147文章

9575瀏覽量

165913 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3399瀏覽量

105865 -

示波器

+關(guān)注

關(guān)注

113文章

6194瀏覽量

184526 -

MOS管

+關(guān)注

關(guān)注

108文章

2396瀏覽量

66603 -

CAN控制器

+關(guān)注

關(guān)注

3文章

74瀏覽量

15017

原文標(biāo)題:用示波器排查CAN的各種錯誤幀

文章出處:【微信號:汽車電子嵌入式,微信公眾號:汽車電子嵌入式】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

示波器破解CAN錯誤幀/BusOff的經(jīng)驗分享

一文讀懂CAN通訊錯誤幀

CRC校驗方法通過CAN總線通信來實現(xiàn)

一種由粗略到精確的瞳孔定位算法

示波器怎么量某一段波形脈寬?技巧分享

一種高效的I幀分區(qū)錯誤隱藏方法

一種新的CAN/FlexRAY網(wǎng)絡(luò)網(wǎng)關(guān)數(shù)據(jù)封裝方法

英創(chuàng)信息技術(shù)關(guān)于新CAN驅(qū)動的錯誤幀定義

通過脈寬變化趨勢分析SPWM波形的方法

一種基于TextRank算法的幀定位方法

虹科干貨 | 帶你全面認(rèn)識“CAN總線錯誤”(一)——CAN總線錯誤與錯誤幀

分享一種用CAN波形的幅度和脈寬信息來精確定位錯誤幀來源的方法

分享一種用CAN波形的幅度和脈寬信息來精確定位錯誤幀來源的方法

評論