ESD靜電放電在芯片實際使用過程中越來越影響到芯片的可靠性,是影響芯片質量和性能的重要因素之一。因此,ESD抗干擾測試是非常重要的,防止ESD對芯片造成損壞。

什么是ESD抗干擾測試?

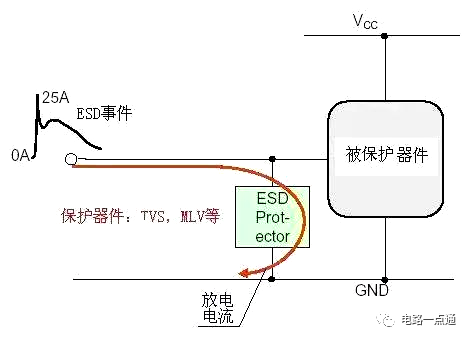

ESD即Electro-Static discharge,意思是靜電放電測試。原理是模擬人或物體接觸設備時產生的放電,以及人或物體對鄰近物體的放電,來檢測設備對靜電放電抗干擾的能力。

ESD分為直接放電和間接放電。直接放電是指利用放電點擊直接對設備進行放電;間接放電是指對設備附近的耦合版實施放電,以模擬人對被測設備附近物體的放電。

ESD抗干擾測試可以檢測芯片的抗干擾能力,從而為采取ESD防護、ESD防護材料的選擇、產品抗靜電性能提升等提供依據,提升芯片質量和可靠性。

影響ESD抗干擾測試的因素

1. 產品本身的材質

不同外殼材質的產品有不一樣的放電路徑,對靜電放電抗干擾測試也會有不一樣的影響。如導體、絕緣體、噴有導電漆的絕緣體等。

2. 測試時的放置方式

不同的放置方式有不同的放電路徑,影響也是不一樣的。

3.放電點與敏感線路的距離

靜電是一種高頻干擾,放電時會產生電磁場,距離近會有較大的寄生電容和較小的耦合阻抗,更容易被干擾。

4.芯片本身的抗干擾能力

這個涉及多個方面,比如芯片本身承受脈沖干擾而不發生邏輯錯誤的能力、外圍電路的處理、外部連接的布線等。

5.放電點的靜電流放電路徑和阻抗

不同路徑會造成不同的阻抗,不同的阻抗會產生不同的干擾。

6.直接注入情況下的防護措施

如MIC、喇叭等在進行空氣放電時會直接沖擊信號線,如果此線路沒有做防護,大多情況下會直接擊穿毀壞芯片。

常見芯片抗ESD的方法

1. 設計ESD保護電路

ESD保護電路如二極管、MOSFET、靜電放電器等。將ESD保護電路集成到芯片設計中,可以防止ESD損壞芯片。

2. 增加芯片的接地和電源引腳數量

增加芯片的接地和電源引腳數量來降低ESD放電時的電阻,幫助更好地分散ESD能量。

3. 減小芯片尺寸

芯片尺寸減小可以幫助減小芯片內部的電容以及靜電放電時芯片受到的電壓峰值,從而降低ESD對芯片的損害。

4. 選擇合適的材料

合適的材料可以降低ESD放電時產生的熱能,降低芯片損壞的風險。

5. 在芯片外部添加防護措施

比如添加ESD保護器件和EMI濾波器等,可以保護芯片不受外部環境ESD和EMI干擾。

6. 嚴格的測試和驗證

在芯片設計和制造的過程中,進行嚴格的ESD測試和驗證,以確保芯片符合相關標準,并能夠在ESD環境下正常工作。

納米軟件專注于各類儀器測試軟件開發,其芯片測試系統與傳統手動測試相比極大提高了測試效率和精度,支持批量測試,并且可以自動匯總管理測試數據,對數據進行智能分析,多樣化數據報告模板可以一鍵導出生成。該系統致力于為廣大用戶提供測試解決方案,解決測試難點。

審核編輯 黃宇

-

ESD

+關注

關注

48文章

2011瀏覽量

172731 -

芯片測試

+關注

關注

6文章

129瀏覽量

20055

發布評論請先 登錄

相關推薦

EMI電磁干擾測試方法 如何有效防止EMI電磁干擾

ESD器件的測試方法和標準

ESD測試儀器的使用方法

ESD測試是什么?CW32能扛8000V?

選擇ESD有哪些建議?

CYT2B75BADQ0AZEGST ESD抗干擾能力問題求解

干貨 | 電路設計中如何減少ESD?

ESD對電子元件的影響 如何選擇ESD保護元件?

用CYUSB3014的時候,怎么樣增強芯片的抗干擾能力?

esd保護措施有哪些

ESD抗干擾測試是什么?防止ESD的常見方法有哪些

ESD抗干擾測試是什么?防止ESD的常見方法有哪些

評論