引言

在數字系統中,總是需要對一些數據進行比較,比較兩個數值甚至多個數值的大小,然后進行排序,于是,數值比較器(Comparator)的邏輯電路便應運而生。

一、半加器的 Verilog 代碼實現和 RTL 電路實現

比較器呢,比較簡單,那就讓我們從底層硬件代碼看一看到底有多簡單!!!

下面是比較器的 Verilog 代碼實現:

module Comparator(

input wire [7:0] a, // 比較數

input wire [7:0] b, // 比較數

output reg result, // 比較結果

output reg equal // 比較結果

);

// 行為描述

always @(a or b) begin

if(a > b)

{equal,result} <= 2'b01; // a 比 b 大

else begin

if(a < b)

{equal,result} <= 2'b00; // a 比 b 小

else

{equal,result} <= 2'b10; // 相等

end

end

// 數據流描述

// assign equal = (a == b) ? 1 : 0;

// assign result = (a > b) ? 1 : 0;

endmodule

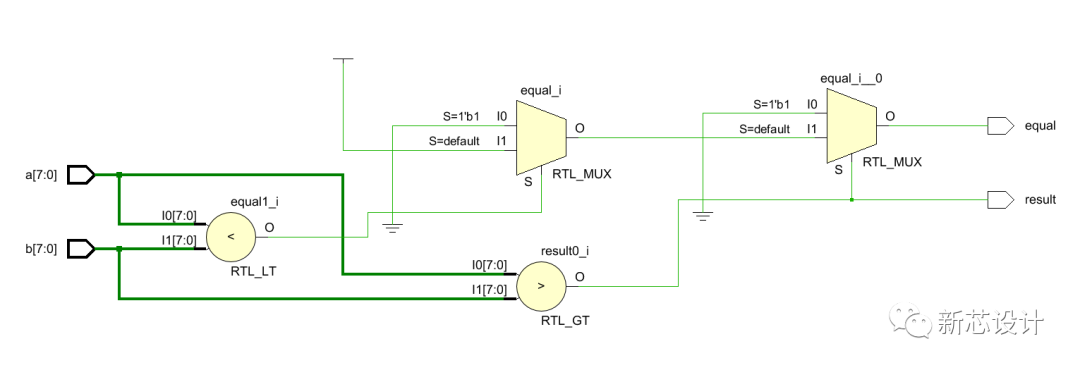

這是一個 8 位數值比較器,其 RTL 電路圖如下所示:

8 位數值比較器的 RTL 電路圖

對兩個 8 位二進制輸入信號進行大小判斷:如果 a 大,則 out 為高電平;如果 b 大,則 out 為低電平;如果 a 和 b 大小相等,那么 equal 則輸出高電平,否則輸出低電平。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42580 -

比較器

+關注

關注

14文章

1634瀏覽量

107099 -

二進制

+關注

關注

2文章

793瀏覽量

41599 -

RTL

+關注

關注

1文章

385瀏覽量

59699 -

Verilog設計

+關注

關注

0文章

20瀏覽量

6514

發布評論請先 登錄

相關推薦

數字電路設計中的一款強大工具—Verilog編程語言介紹

Verilog是一種硬件描述語言,用于描述數字電路的結構和行為。與傳統的編程語言不同,Verilog更加注重電路的行為和時序特性。

發表于 08-01 09:00

?4310次閱讀

招聘:數字電路設計師

數字集成電路設計ASIC設計/驗證經驗;2.熟悉邏輯/時序電路的原理和設計;3.精通verilog語言;熟練使用Cadence,Modelsim,NC-

發表于 02-27 10:52

數字電路設計的基本方法有哪些

在數字電子技術基礎課程中,數字電路設計的數學基礎是布爾函數,并利用卡諾圖進行化簡。卡諾圖只適用于輸入比較少的邏輯函數的化簡。數字電路的設計方法是:組合

發表于 02-27 11:55

基于LabVIEW的數字電路設計和仿真

基于LabVIEW的數字電路設計和仿真

數字電路設計和仿真是電子工程領域的基本技術。介紹了基于LabV IEW的數字電路設計和仿真的原理和方法,比較了其與專業EDA軟

發表于 03-30 16:09

?124次下載

高速數字電路設計

高速數字電路設計

關于高速數字電路的電氣特性,設計重點大略可分為三項 : Ø 正時 (Timing) :由于數字電路大多依據時脈信號來做信號間的同

發表于 10-16 17:22

?3129次閱讀

FPGA CPLD數字電路設計經驗分享.

FPGA CPLD數字電路設計經驗分享.(電源技術發展怎么樣)-FPGA CPLD數字電路設計經驗分享? ? ? ? ? ? ? ? ? ??

發表于 09-18 10:58

?52次下載

Verilog數字系統設計——復雜數字電路設計2(FIFO控制器設計)

Verilog數字系統設計十二復雜數字電路設計2文章目錄Verilog數字系統設計十二前言一、什

發表于 12-05 15:51

?9次下載

基于Verilog的經典數字電路設計(2)比較器

基于Verilog的經典數字電路設計(2)比較器

評論