引言

在數(shù)字信號的傳輸過程中,有時需要從一組輸入數(shù)據(jù)中選出某一個來,比如輸入有 “A、B、C、D” 四個數(shù)據(jù),那么我們想要哪個字母輸出,就可以設(shè)置哪個字母輸出,這里的設(shè)置,即所謂的 “選擇開關(guān)” ;又或者,你可以理解為多個通道輸入到單個通道的輸出;于是,數(shù)據(jù)選擇器(Data Selector)或多路開關(guān)(Multiplexer)的邏輯電路便應(yīng)運而生。

一、2 選 1 數(shù)據(jù)選擇器的 Verilog 代碼實現(xiàn)和 RTL 電路實現(xiàn)

module Multiplexer(

input wire a, // 輸入數(shù)據(jù)信號

input wire b, // 輸入數(shù)據(jù)信號

input wire sel, // 輸入控制信號

output result // 輸出數(shù)據(jù)信號_已選擇

);

assign result = sel ? a : b;

endmodule

這是 2 選 1 數(shù)據(jù)選擇器的設(shè)計代碼,非常簡單明了,主要是輸入數(shù)據(jù) a 和 b,然后通過 sel 信號來選擇輸出是 a 還是 b。倘若 sel 拉高,即為 “1” 的時候,那么就輸出 “a”,反之,倘若 sel 拉低,即為 “0” 的時候,那么就輸出 “b”。

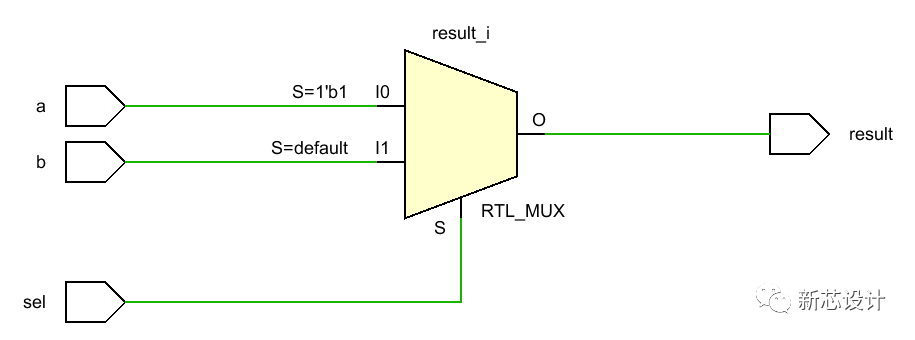

這是一個數(shù)據(jù)選擇器設(shè)計,該設(shè)計是一個直接用組合邏輯語句或者也可以說是連續(xù)賦值語句 assign 的方式描述的電路,其 RTL 電路圖如下所示:

2 選 1 數(shù)據(jù)選擇器的 RTL 電路圖

二、4 選 1 數(shù)據(jù)選擇器的 Verilog 代碼實現(xiàn)和 RTL 電路實現(xiàn)

module Multiplexer(

input wire a, // 輸入數(shù)據(jù)信號

input wire b, // 輸入數(shù)據(jù)信號

input wire c, // 輸入數(shù)據(jù)信號

input wire d, // 輸入數(shù)據(jù)信號

input wire [1:0] sel, // 輸入控制信號

output reg result // 輸出數(shù)據(jù)信號_已選擇

);

always @(sel, a, b, c, d)

case (sel)

2'b00: result <= a;

2'b01: result <= b;

2'b10: result <= c;

2'b11: result <= d;

endcase

endmodule

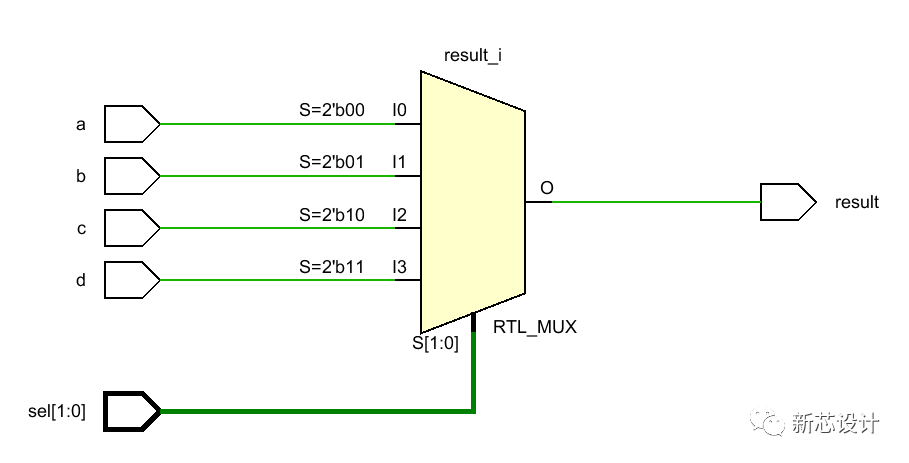

這是一個 4 選 1 數(shù)據(jù)選擇器,基于查找表 LUT(Look Up Table)(查找表在 FPGA 中非常重要,軟件思維可以理解為 “索引”,它是 FPGA 芯片架構(gòu)的重要組成部分,合理利用查找表,能夠使你的 FPGA 硬件工程達到一定程度的優(yōu)化設(shè)計)的方式實現(xiàn)的一個電路,其 RTL 電路圖如下所示:

4 選 1 數(shù)據(jù)選擇器的 RTL 電路圖

總結(jié)

數(shù)據(jù)選擇器在實際生活中應(yīng)用廣泛。比如,在實際中對選手進行挑選,比如在歌手舞臺對 “小洪” 編號為 “a”,對 “小華” 編號為 “b”,然后 “sel” 選擇信號就交給 “裁判”,倘若 “小洪” 唱歌功底勝出,那么輸出 “a”,反之輸出 “b”,是不是很形象呢?!

-

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42581 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59706 -

數(shù)據(jù)選擇器

+關(guān)注

關(guān)注

2文章

116瀏覽量

16429 -

FPGA芯片

+關(guān)注

關(guān)注

3文章

246瀏覽量

39780 -

Verilog設(shè)計

+關(guān)注

關(guān)注

0文章

20瀏覽量

6514

發(fā)布評論請先 登錄

相關(guān)推薦

數(shù)字電路設(shè)計中的一款強大工具—Verilog編程語言介紹

招聘:數(shù)字電路設(shè)計師

數(shù)字電路設(shè)計的基本方法有哪些

基于LabVIEW的數(shù)字電路設(shè)計和仿真

高速數(shù)字電路設(shè)計

數(shù)字電路設(shè)計

數(shù)字電路中的FPGA和verilog教程

FPGA CPLD數(shù)字電路設(shè)計經(jīng)驗分享.

Verilog數(shù)字系統(tǒng)設(shè)計——復(fù)雜數(shù)字電路設(shè)計2(FIFO控制器設(shè)計)

基于Verilog的經(jīng)典數(shù)字電路設(shè)計(3)選擇器

基于Verilog的經(jīng)典數(shù)字電路設(shè)計(3)選擇器

評論