什么是傳輸時延?

首先介紹下傳輸時延指標。

傳輸時延定義:時延是指最小系統輸出信號對輸入信號的時間延遲。

傳輸時延的指標:

選頻型 ≤20μs;

寬帶型 ≤10μs;

每鏈型增加一級擴展設備,時延增加小于1.5μs;

另外還有一個相關的指標,這個指標對于兩級以上的直放站系統需要關注,這個指標是時延校正范圍及補償精度。

定義:時延校正補償精度是指系統對由于支路之間的鏈型級數和光纖長度不同引起的不同遠端單元時延偏差的校準補償能力。

指標:

時延補償范圍≥50μs

時延校正補償精度±2μs

系統應具備手動和自動時延調整功能。

為什么需要傳輸時延指標?

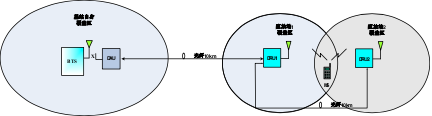

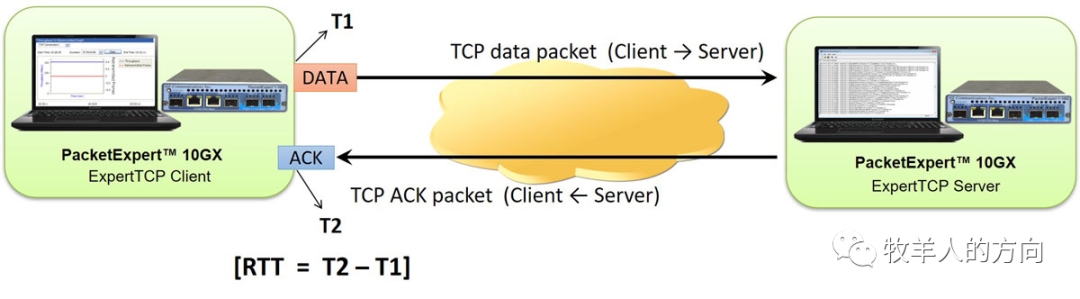

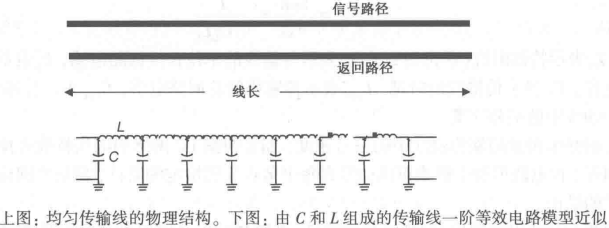

信息在空間傳播的速度是3×108m/s(即一公里有3.3μs時延),在光纖中的速度約為自由空間的2/3(即一公里的光纖有5μs時延)。對于時分多址系統來說,每個終端都是按順序先后發送數據。通常是離基站近的信號就早點到達,離得遠就晚點到。

問題來了,如果有一個終端用戶離得基站特別遠呢?基站沒有識別到這個終端,這樣就有可能和其他終端信號一起到達,從而形成信號重疊,而導致信號干擾。

所以直放站作為基站和用戶終端之間的信號傳輸通道,時延不能無限制。一般系統的時延+空間傳輸的時延要小于各制式的保護間隔。

那么時延校準是為什么呢?

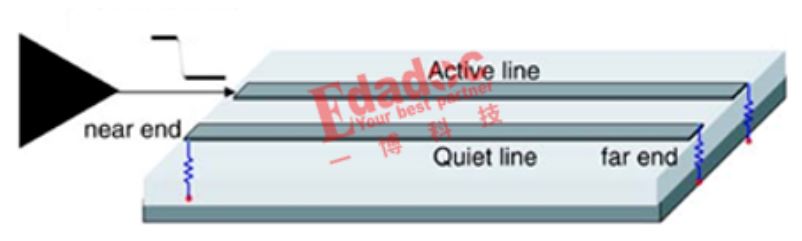

用戶終端發射的信號是一個球狀,如果一個用戶終端剛好在兩個遠端的重疊覆蓋區,那么用戶發射的信號到達基站的時延差不一樣,如果不調整,其中一個信號就成為另外一個信號的同頻干擾了。所以需要把每個遠端的時延調整到一個合理區間。

怎么設計才能滿足傳輸時延?

固有傳輸時延設計建議:

1、數字預的濾波器:如果是模擬系統,其實整個時延就是1us內。主要是數字系統的直放站時延很大,其中很大一部分是數字預的成型濾波器。帶外抑制越好成型濾波器的階數越高,需要FPGA在做濾波器時做好兼顧。

2、光口傳輸速率:光口傳輸速率之前聊過,大家想把傳輸速率做低,這樣可以傳輸更大帶寬的信號,但是這樣時延會增加,這個也需要同時兼顧的。

3、采樣速率:采樣速率越高,時延越低。但是這樣會增加數字預的內插和抽取倍數,從而增加一定的時延。這個也需要同時兼顧。

4、組幀和解幀:這個是固有時延,當然如果系統時延不滿足的時候,也可以優化這部分。

時延調整范圍和精讀設計建議:

這個比較簡單,時延只可以增加,不能減少,所以FPGA在內部數字預里面做一個時延調整功能即可。但是精讀盡量做細點,也就是每個sample需要足夠小。

-

濾波器

+關注

關注

158文章

7592瀏覽量

176556 -

FPGA器件

+關注

關注

1文章

22瀏覽量

11589 -

傳輸時延

+關注

關注

0文章

5瀏覽量

1808

發布評論請先 登錄

相關推薦

TLV3201電流檢測電路的時延應該怎么算?

HarmonyOS實戰開發-如何實現音頻低時延錄制和播放,AudioVivid音樂播放的相關功能

泰克示波器如何測量時延?

為什么網線都會限制傳輸距離為100米?

CAN總線的傳輸距離與采樣點、傳輸時延之間的關系,你弄明白了嗎?

AD9361時延響應特性不固定如何優化?

差分探頭測量差分時鐘時延的全面指南

走近NetEngine?5000E集群 |?助力福建移動時延降低43%,體驗看得見

什么是傳輸時延?為什么需要傳輸時延指標?

什么是傳輸時延?為什么需要傳輸時延指標?

評論