1.前言

Live-Simulation (live-sim)模式允許Visualizer調(diào)試環(huán)境與Questasim進(jìn)行交互操作,此模式將Visualizer GUI與Questasim仿真相結(jié)合,因此可以在線調(diào)試當(dāng)前仿真的結(jié)果和波形。

在livesim模式中,可以在Visualizer GUI中控制仿真、設(shè)置斷點(diǎn)(Breakpoints)、單步調(diào)試、檢查記錄或未記錄的數(shù)據(jù)值、以及跟蹤類對(duì)象。因此,在調(diào)試驗(yàn)證環(huán)境或RTL的問題時(shí),livesim可以更有效率地定位問題。下文介紹下live-simulation模式如何啟動(dòng)以常用功能。

2.啟動(dòng)live-sim模式

Questasim要求使用3步仿真流程(vlog, vopt, vsim)來調(diào)用livesim模式下的Visualizer,而不是2步仿真流程(vlog, vsim+vopt)。

第一步:準(zhǔn)備TB和RTL代碼

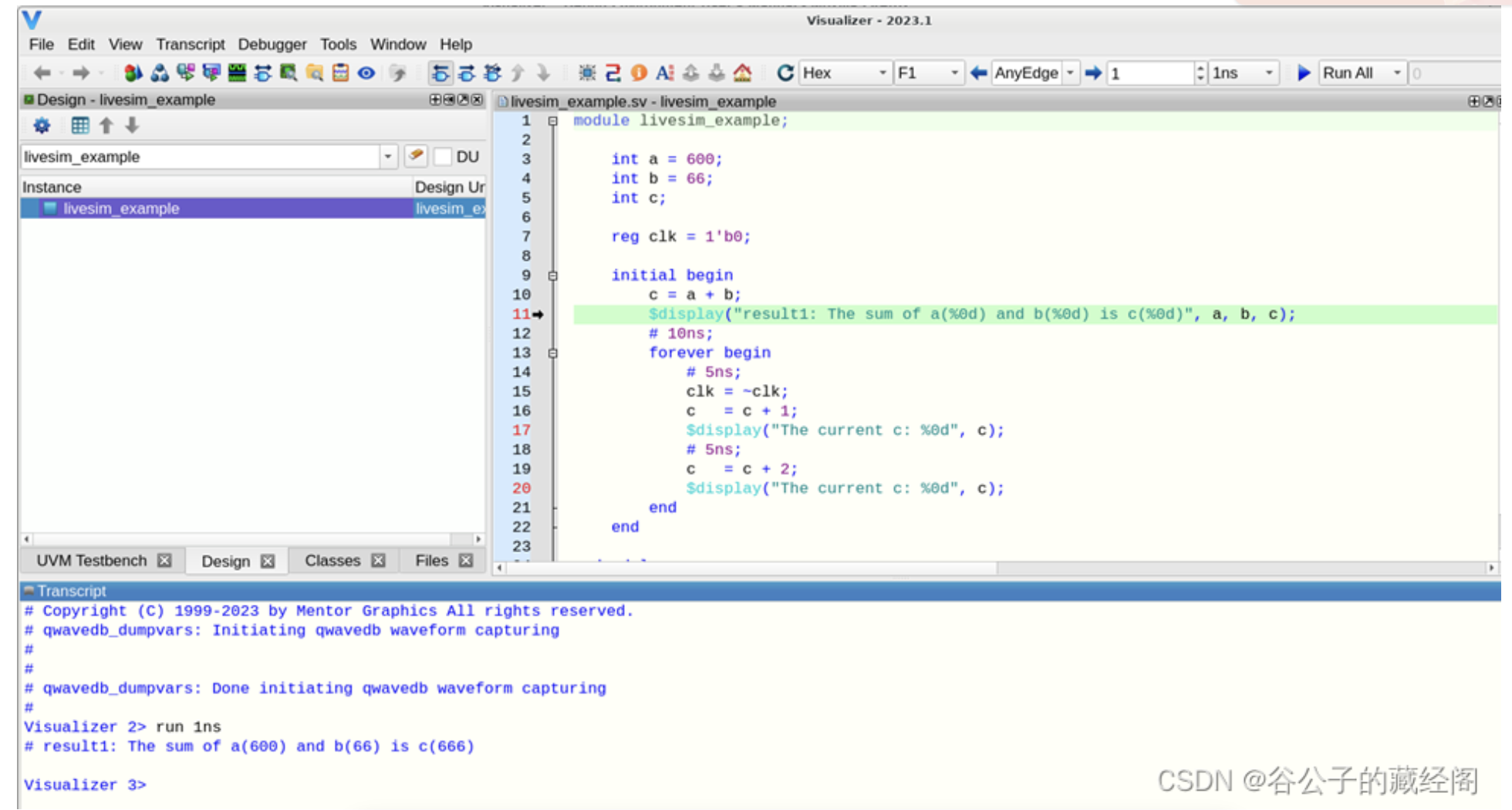

這里簡單創(chuàng)建名為livesim_example.sv的文件,它的內(nèi)容是:

module livesim_example;

int a = 600;

int b = 66;

int c;

reg clk = 1'b0;

initial begin

c = a + b;

$display("result1: The sum of a(%0d) and b(%0d) is c(%0d)", a, b, c);

# 10ns;

forever begin

# 5ns;

clk = ~clk;

c = c + 1;

$display("The current c: %0d", c);

# 5ns;

c = c + 2;

$display("The current c: %0d", c);

end

end

endmodule

第二步:vlog命令編譯

需要調(diào)用Questasim的vlog命令把代碼先編譯過,命令如下:

vlib work

vlog livesim_example.sv

這時(shí)候會(huì)生成livesim_example的top module。(注意,如果是VHDL文件的話,要使用vcom命令,而不是vlog)

第三步:vopt命令優(yōu)化

需要調(diào)用Questasim的vopt命令把design優(yōu)化下,命令如下:

vopt -debug livesim_example -o live_opt -designfile design.bin

這時(shí)候會(huì)生成名為live_opt的優(yōu)化design名。

在優(yōu)化過程中,必須的-designfile參數(shù)的作用是創(chuàng)建Visualizer所需的design數(shù)據(jù)庫文件名稱(design.bin),如果默認(rèn)用design.bin名稱的話,其實(shí)-designfile design.bin可以替換為+designfile,這樣Questasim默認(rèn)生成的bin文件名字為design.bin。必須的-o參數(shù)為design的優(yōu)化版本指定一個(gè)名稱,名稱可以包含小寫字母、大寫字母、數(shù)字字符或下劃線。可選的-debug參數(shù)限制優(yōu)化以保證行號(hào)的可見性,這就可以在Visualizer的livesim模式下啟用行breakpoints。其它需要的vopt參數(shù)大家可以根據(jù)需要添加。

第四步:vsim命令仿真

使用vsim命令開始仿真,命令如下:

vsim -visualizer live_opt

這里live_opt的名字就是第三步vopt命令-o參數(shù)生成的名字。vsim命令將design加載到仿真器中,然后將design.bin文件和仿真控制傳遞給Visualizer GUI。

在design elaboration過程中,仿真elaboration消息顯示在啟動(dòng)shell中,并且也保存在visualizer.log文件中。如果elaboration有錯(cuò)誤,則顯示消息并退出仿真。如果elaboration成功,將調(diào)用Visualizer GUI。Visualizer GUI首先讀取數(shù)據(jù)并連接到仿真器,當(dāng)GUI準(zhǔn)備好接受CLI命令時(shí),在transcript窗口會(huì)出現(xiàn)” Visualizer 1>”。

只要完成了以上的幾個(gè)步驟,就會(huì)出現(xiàn)以下界面,表示進(jìn)入livesim模式了,也就是聯(lián)合Questasim和Visualizer進(jìn)行實(shí)時(shí)仿真調(diào)試。

3. livesim仿真常用功能

進(jìn)入livesim模式后,就是使用Visualizer GUI界面去debug代碼了,這里簡單介紹幾個(gè)常用功能,更多的用法大家可以去探索下。

3.1 變量值提示

當(dāng)啟用變量值提示(Value Tool Tip)功能后,記那個(gè)鼠標(biāo)懸停在源代碼、原理圖和許多其它窗口中的對(duì)象上時(shí),彈出的工具提示將顯示該對(duì)象的值、大小和帶有下劃線 (_) 的基數(shù)前綴。此默認(rèn)值格式化在仿真期間被記錄。

不過通過vsim命令中指定+vis_no_format_num,可以禁用值格式化,只顯示對(duì)象值。變量值提示(Value Tool Tip)啟動(dòng)和關(guān)閉按鈕在下圖紅色箭頭指向的地方。

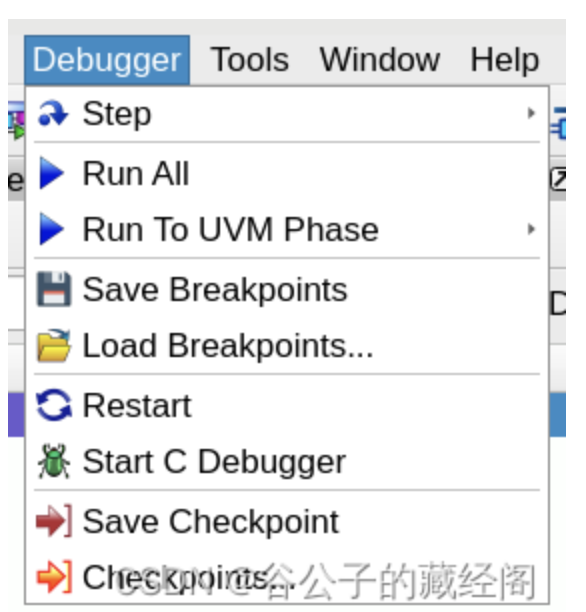

3.2 Debugger菜單

在Debugger菜單下有運(yùn)行、步進(jìn)、重新啟動(dòng)、保存或恢復(fù)checkpoints點(diǎn),以及使用C調(diào)試器。

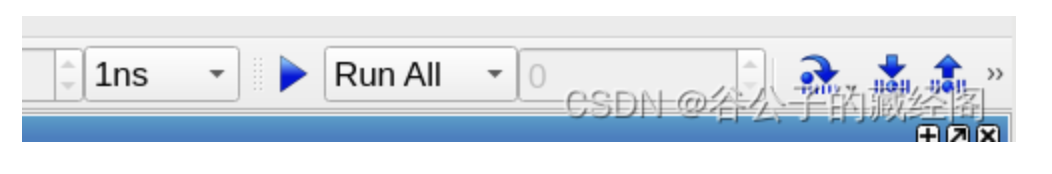

3.3 工具欄的調(diào)試

在工具欄上也可以方便的控制仿真的進(jìn)行。

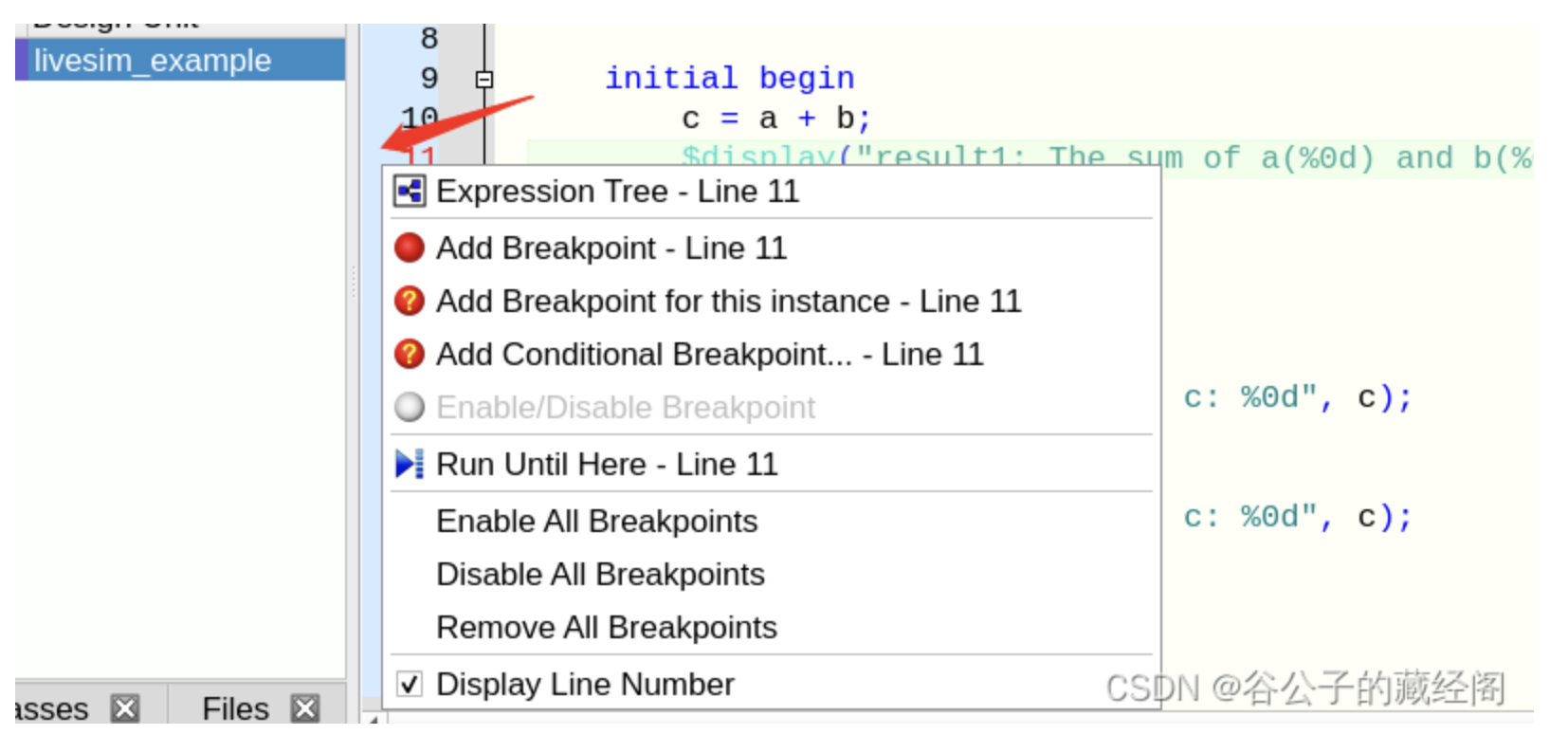

3.4 設(shè)置breakpoint

右鍵代碼的前方,會(huì)出現(xiàn)以下窗口,我們就可以設(shè)置一些breakpoint來輔助debug。

-

仿真器

+關(guān)注

關(guān)注

14文章

1016瀏覽量

83632 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59699 -

GUI

+關(guān)注

關(guān)注

3文章

648瀏覽量

39546 -

VHDL電路

+關(guān)注

關(guān)注

0文章

4瀏覽量

1399

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

NCSIM、VCS和QuestaSim后仿真如何屏蔽冗余的違例信息呢?

如何用questasim進(jìn)行systemverilog仿真

ISE設(shè)計(jì),questasim仿真時(shí)庫編譯的問題

PROTOLINK PROBE VISUALIZER的優(yōu)勢(shì)

介紹一下波形仿真如何進(jìn)行

Proteus仿真如何將40110的7段數(shù)碼管輸出信號(hào)轉(zhuǎn)換成BCD二進(jìn)制信號(hào)呢?

全新WEBENCH Visualizer設(shè)計(jì)工具

ModelSim和QuestaSim功能簡介及應(yīng)用

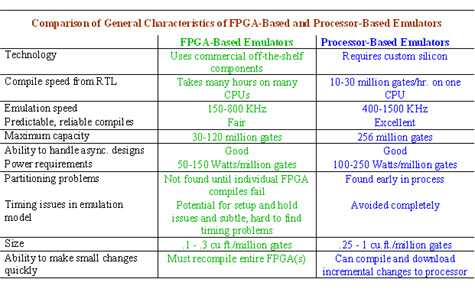

基于FPGA的仿真如何工作

如何通過自動(dòng)化腳本實(shí)現(xiàn)Questasim和Verdi的聯(lián)合仿真

Questasim與Visualizer的livesim仿真如何啟動(dòng)呢?

Questasim與Visualizer的livesim仿真如何啟動(dòng)呢?

評(píng)論