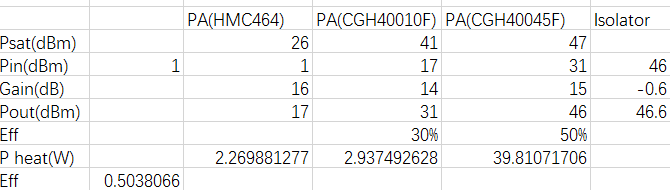

具體指標如下:

頻段 2.7-3.5GHz

輸入功率<1dBm

輸出飽和功率>46dBm

介質板為Rogers 4003,介電常數為3.38,厚度為0.508mm

- 末級功放電路設計

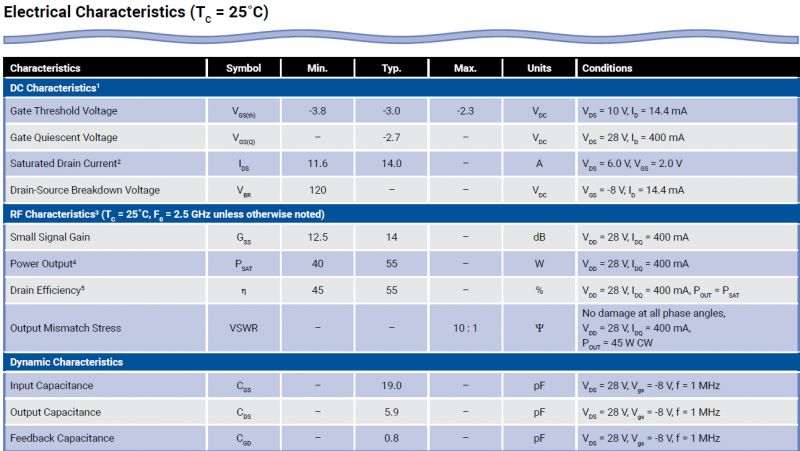

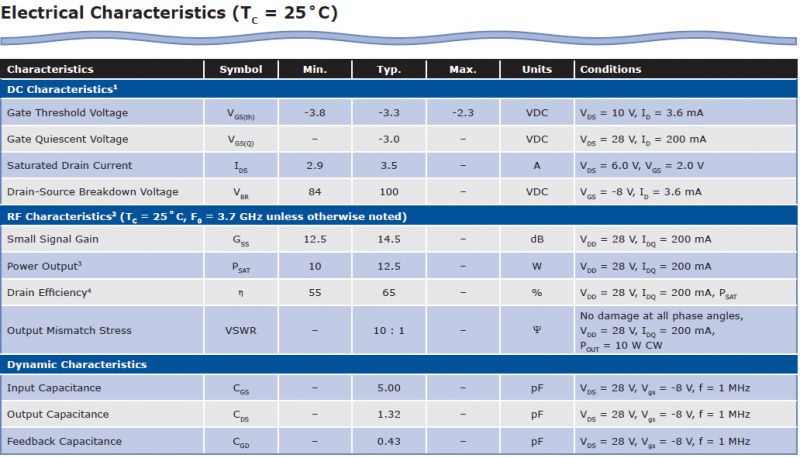

末級功率放大電路選用CREE公司的CGH40045高電子遷移速率晶體管。資料中CGH40045的飽和輸出功率為55W,效率為55%

設計流程如下:

- 1 靜態工作點的設置

在芯片資料中,漏源電壓28V,柵源電壓的工作范圍為-3.0V

1.2 穩定性分析

對晶體管進行穩定性仿真可以得到穩定判斷的K線圖和B線圖,分別如下圖所示,K>1且B>0,CGH40045F在應用頻段屬于穩定的。

1.3晶體管輸入與輸出阻抗分析

利用CREE公司提供的大型號模型,結合ADS 負載牽引可以仿真得出輸出與輸出阻抗變化呈線性分布,因此設計電路考慮輸入輸出對稱拓撲結構。

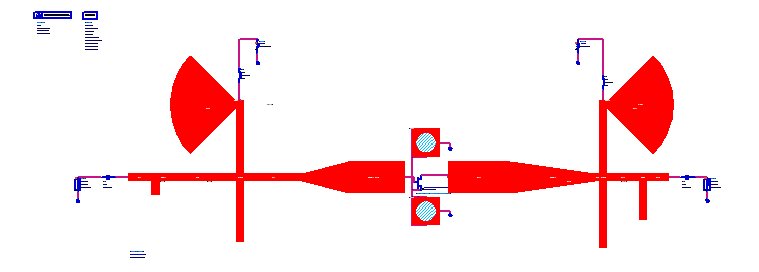

1.4 饋電端λ/4高阻線設計

偏置電源為其供電時,必須要保證電源的直流信號可以順利向CGH40045F所在的功放電路的柵極、漏極提供偏置電壓,并且還要保證功率放大器輸入輸出信號不會從偏置電路泄露。故需要在所要求的頻段內設計一高阻線,使其對于直流表現為通路,射頻信號表現為開路,即相當于扼流圈的作用。,扇形結構由于寬度是漸變的,可以很好的滿足寬帶性能,拓撲結構如下圖所示:

經過仿真優化得到S(1,1)、S(2,2)接近0dB,在2.7-3.5GHz頻段范圍內全反射,滿足高阻線設計要求。

1.5 功放寬帶匹配電路的設計

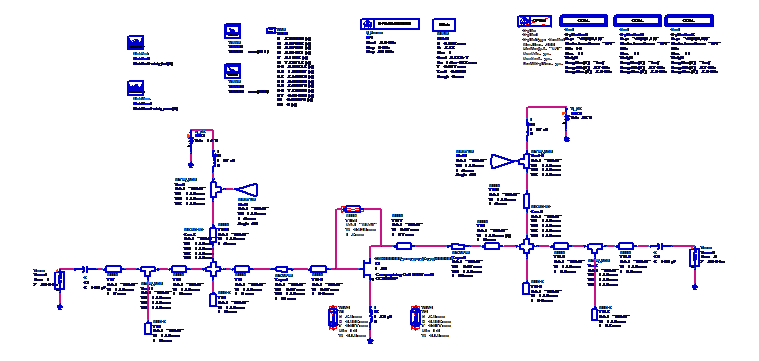

如下圖所示,本文采用典型的雙分支平衡匹配電路,由于其結構具有較多的可控變量,適用頻段更寬,同時由于晶體管輸入,輸出阻抗變化較為線性,在輸入端和輸出端各有一段漸變線,進行阻抗平滑過渡。

根據S參數不斷進行原理圖優化,滿足要求后進行EM版圖聯合仿真。

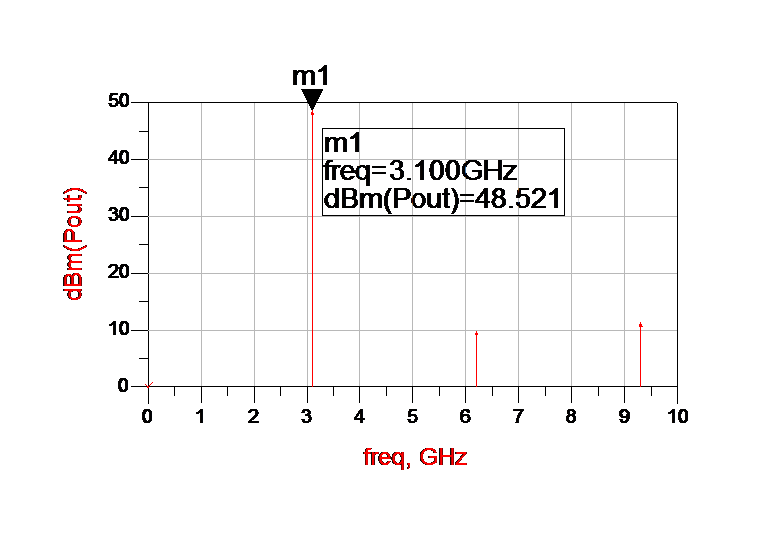

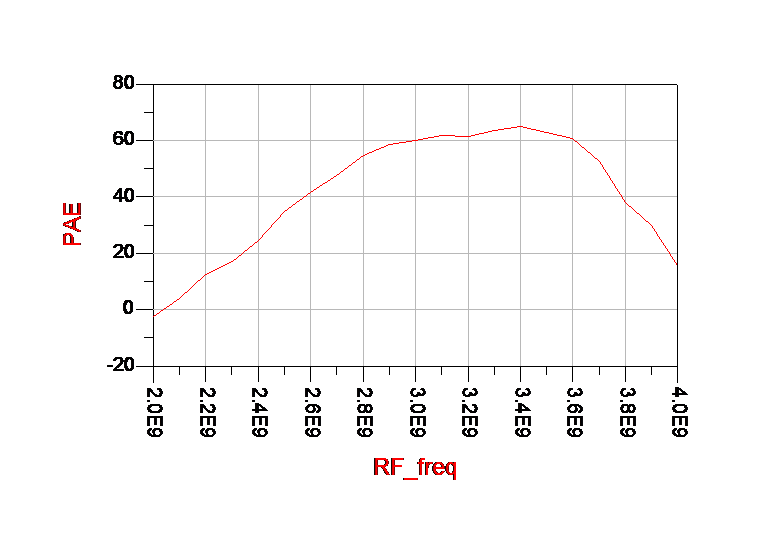

版圖聯合仿真滿足S參數指標要求后,進行諧波平衡仿真與增益,功率仿真,結果如下,可見基波在3.1GHz處的功率為48.5dBm,二次諧波和三次諧波的功率為10dBm左右,諧波相對于基波可以忽略不計。CGH40045F晶體管的3dB輸出功率約48.5dBm,而實際需要46.6dBm就已經足夠,因此在正常工作時,沒有必要達到此3dB壓縮點,在全頻段功放效率在50%以上。

- 驅動級功放設計

驅動級選擇的CREE的CGH40010F,芯片資料中,給出了CGH40010氮化鎵高電子遷移速率晶體管的飽和輸出功率為13W,在飽和輸出功率下的效率為65%。

根據大信號模型仿真其阻抗點跟末級功放一樣,具有線性的增長變化,因此中間級驅動具有相同的拓撲結構,通過優化變量使其S參數指標滿足要求。

原理圖結合EM版圖聯合仿真,同時分別調用ADS電磁仿真軟件下的S參數仿真模塊對其功率增益以及一端口二端口的反射情況進行仿真分析;調用諧波平衡仿真模塊對其二次諧波、三次諧波的大小進行分析;調用增益壓縮仿真模塊,對匹配電路的1dB功率增益壓縮點進行仿真分析等。

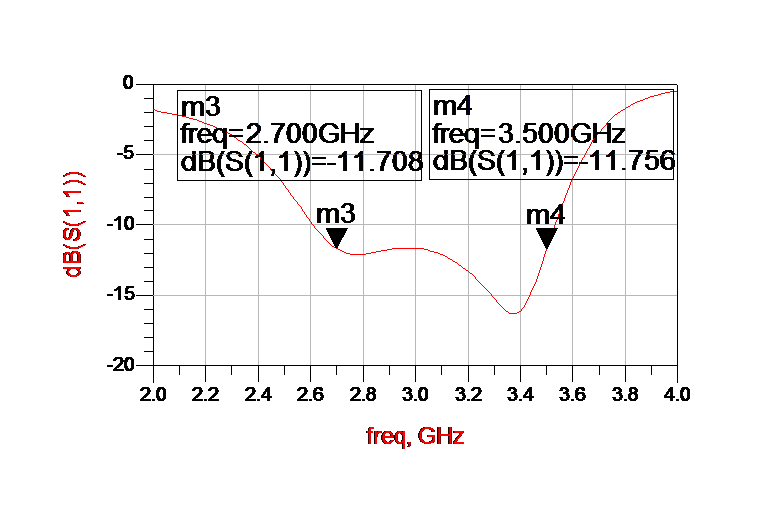

2.1 驅動級功放S參數仿真分析

如下圖所示,S(1,1)<-11dB,S(2,1)>13dB。

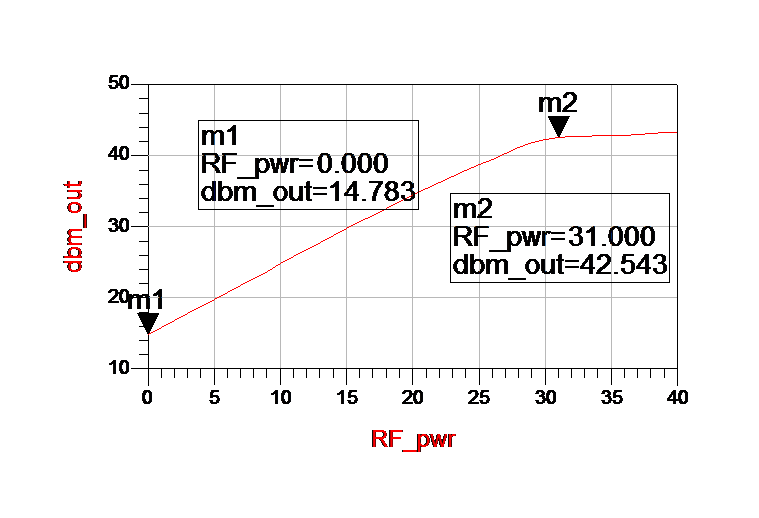

2.2 驅動級功放諧波平衡仿真

如下圖所示,中心頻率3.1GHz處,基波的3dB壓縮點的輸出功率約為42.5dBm,二次諧波和三次諧波的3dB壓縮點的輸出功率分別約為20.2dBm、13.2dBm,較基波的輸出功率小得多,對基波影響較小。晶體管全頻帶效率大概在35%以上。

3 前級功放的設計

前級功放選擇Hittite公司的HMC 464功放芯片,其增益在2GHz~4GHz內大于16dB,回波損耗在-15dB以下,輸出功率1dB壓縮點為26dBm。

- 末級隔離器的選型

為了保障功放的合理測試,防止反射功率太大損壞功放,因此末級選擇了UIY(深圳優譯的隔離器)UIYBDI3234A2T4,如下圖所示:

- 整機鏈路計算

此模塊采用三級放大,整個模塊的效率在50%

-

功率放大電路

+關注

關注

13文章

161瀏覽量

25769 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

偏置電路

+關注

關注

10文章

97瀏覽量

30764 -

ADS仿真

+關注

關注

0文章

71瀏覽量

10425 -

二次諧波

+關注

關注

0文章

25瀏覽量

9564

發布評論請先 登錄

相關推薦

請問RF的頻率是1.2GHZ-3.5GHZ,本振芯片可以選什么?

3.5GHz產業市場巨大

MT8820A無線通信分析儀--30MHz至2.7GHz

TRF1216,pdf(3.5-GHz High Dynam

3.5GHz固定無線接入系統技術分析

MAX2839/MAX2839AS 2.3GHz至2.7GH

5G NR(3.5 GHz)無線網絡覆蓋問題及建議方案分析

美國無線通信和CTIA敦促FCC就3.5 GHz和3.7-4.2 GHz頻段頻譜分配做出行動

HMC546LP2E:10 W,FailSaffe,GAAs,SPDURT.2 GHz to 2.7 GHz數據Sheet

HMC114PM5E:>10W(42 Dbm)、2.7 GHz to 3.8 GHz、Gan Power Amplififer數據Sheet

HMC1114:10瓦,GaN功率放大器,2.7 GHz至3.8 GHz數據表

2.7GHz-3.5GHz功放設計分析

2.7GHz-3.5GHz功放設計分析

評論