高速信號行為、RF信號傳播和PDN仿真是PCB中最難仿真的部分。在這些電磁現象中,高速信號傳播和RF傳播需要電磁場求解器工具來提取有用的結果。在電路仿真中需要考慮的寄生效應和設計特定效應過多。盡管我們很努力,但信息實在太多了,在這兩種情況下難以建模。

PDN仿真有些不同,因為要仿真的相關頻率范圍較低,對于大多數設備而言通常小于10GHz。這意味著可以使用SPICE仿真而不是完整的電磁場求解器仿真,為相對較小的電路板上支持中速數字元件的PDN建模。只要電路板足夠小或頻率足夠低以至于可以忽略傳播,就可以通過SPICE仿真收獲有用的結果。

如果您以前從未這樣做過,我將展示如何設置以及您可能會收獲什么樣的結果。通過仿真連接到PDN的負載元件中的開關動作,可提取某些有用的數據來描述您的PDN,甚至可以計算其網絡參數。在下方我將展示的仿真中,目標是提取:

PDN阻抗頻譜

在負載元件的輸入引腳處測量的瞬態響應

這些參數如何隨著電容值的變化而變化

對相對低速和小型電路板的限制很重要,我將詳述這到底意味著什么。

設置PDN仿真

用于描述PDN阻抗和計算瞬態響應的標準仿真如下圖所示。我已將其放置在Altium 365 Viewer中,以便用戶可以瀏覽設計并查看仿真是如何設置的。

仿真原理圖是使用一組未按任何特定順序選擇的去耦電容器創建的。起初我一直把這個數字保持在較低水平,但稍后我將在的仿真中增加這個數字,這樣我們就可以看到增加電容會如何影響結果。在繼續的同時,我們將調整其他參數。

等效電路模型

此原理圖是使用Altium Designer中內置的仿真通用元件庫中的元件設置的。如果不是Altium Designer用戶,您當然可以使用SPICE包或其他原理圖編輯器中的通用元件,在任何其他仿真程序中重新創建。正如我在原理圖中指出的那樣,整體仿真由四個部分組成:

穩壓器:這是為PDN供電的穩壓器模塊或電路。我已包括其標稱輸出電阻和電感。

衰減:這是去耦電容器部分。電容器將ESL和ESR作為分立元件包括在內,只是為了清楚地顯示它們。請注意,您還可以將這些值定義為屬性面板中這些元件的參數。

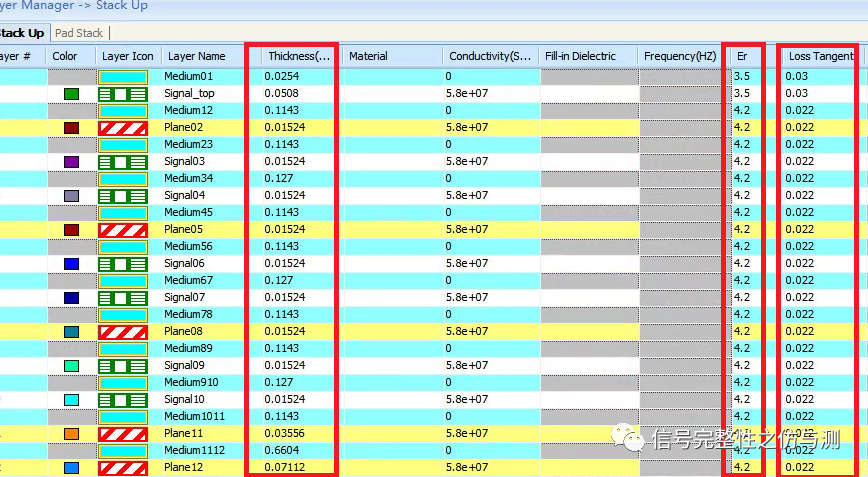

平面:本節定義了我們的電源/接地平面對的電容、電感和電阻。本節中的電感是擴散電感,我在另一篇文章中對此進行了描述。

PWR_IN:這是我們負載IC中的輸入電源部分。我已嘗試通過電感、引腳封裝電感和輸入端的接觸電阻,對輸入進行建模。這些值因產品和封裝而異,但此處的值是典型的數量級數字。

此等效電路模型需要調整平面電容(CP1)、平面電感(LP1)和去耦電容的數量。我們將使用瞬態分析和交流掃描仿真來獲得這些數據。

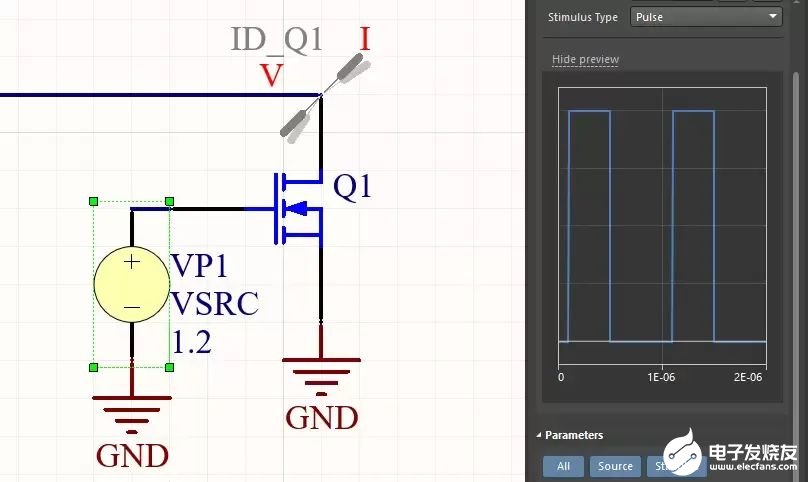

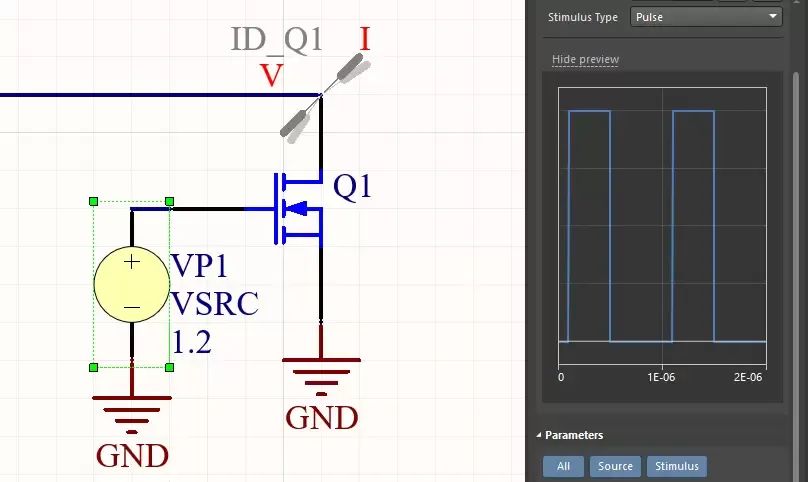

在此之前,我們應該討論上圖所示的NMOS元件。

負載建模

PWR_IN部分包含一個負載模型,它只是一個開關n通道MOSFET。在建模負載并查看PDN上的瞬態響應時,目標是檢查PDN如何對開關操作做出反應,然后吸收電流。以這種方式使用快速MOSFET,可檢查負載電流如何根據某些邏輯輸入突然切換到高電流狀態。該邏輯輸入通過在屬性面板中將VSRC元素設置為脈沖模式以實現建模目的。我已將升壓和降壓時間設置為1ns。盡管1/(升壓時間)帶寬為500MHz,但這不在超高頻范圍內,因此信號可能會受到平面去耦不良和較大電容器的影響。

仿真中的PWR_IN部分

另一種方法是將電流源設置為脈沖模式。這將有效地執行在低電流狀態和高電流狀態之間切換負載的相同功能。然后,仿真將讀取輸出給MOSFET漏極的電流和電壓。更準確的方法是放置一個CMOS緩沖電路來仿真IO,但這對于檢查接地反彈或抖動等問題會更好,因此我們將其保存以備后用。現在,我們將查看上述模型,以檢查當邏輯電路切換狀態并通過PDN汲取電流時會發生什么。

結果

首先,我想看看上述案例的結果,我們有9個不同值的并聯去耦電容器,它們都具有相似的ESL和適中的ESR值。ESR值在這里很重要,因為它有助于拉平PDN阻抗頻譜,正如我在另一篇關于PDN阻抗的文章中所展示的那樣。仿真參數如下:

瞬態分析:10ns步長,5-10us總仿真時間

交流掃描:10GHz最大頻率,計算PDN的|Z|

去耦電容器編號:我將查看上面的9個電容器模塊和一個由36個電容器組成的四倍模塊。

平面電容:低態(CP1 = 20 pF)和高態(CP1 = 1 nF)

內芯電壓:VDD = 1.8 V

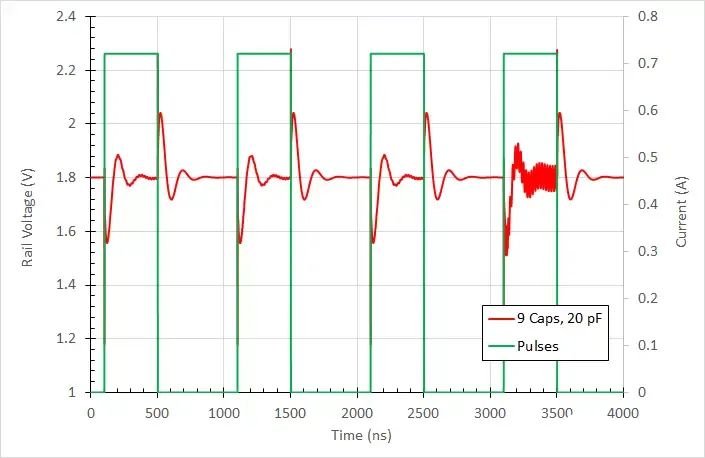

9個電容器,20pF平面電容

僅使用9個去耦電容器和20pF平面電容,我們可以看到瞬態響應中具有非常大的波動,幅度達到約300 mV,疊加在所需的1.8V內芯電壓上。這對于任何實際應用來說都大到無法接受,并且會在輸出上產生大的干擾。此處顯示的數據摘自.sdf文件并導出為Excel格式。

使用9個去耦電容器和20 pF平面電容的瞬態結果

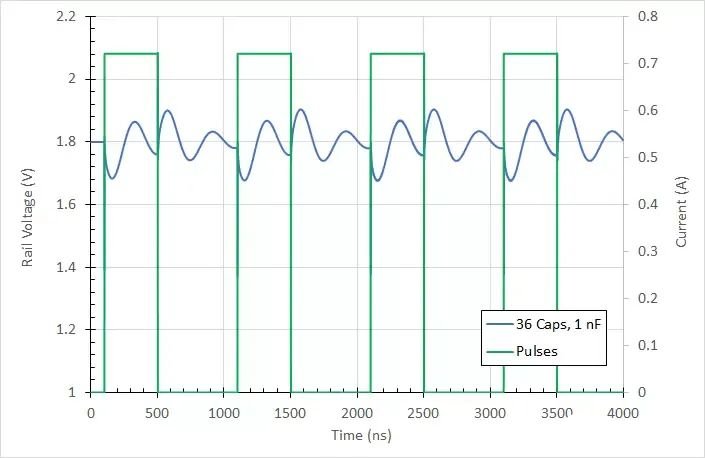

36個電容,1 nF平面電容

讓我們看看當我們將去耦電容器的數量增加到四倍并將平面電容增加到50倍時會發生什么。此設計的新版本和改進版本如下所示。基本上,復制去耦電容器模塊是為了增加該去耦網絡的等效電容。

結果清楚地顯示了具有電源/接地平面對以及更多去耦電容器的好處;隨著電容的增加,瞬態響應的幅度通常會下降,正如我們所預料的那樣。當我們將電容器數量增加到四倍并增加平面電容時,PDN上的電源軌響應僅以100mV的幅度波動。

使用36個去耦電容器和1 nF平面電容的瞬態結果

對于1.8V電源軌來說,這仍然有點大,似乎使用36個電容器應該會產生更好的結果。通過查看每種情況下的阻抗頻譜,我們可以了解為什么使用更多電容器不會產生明顯的阻尼。

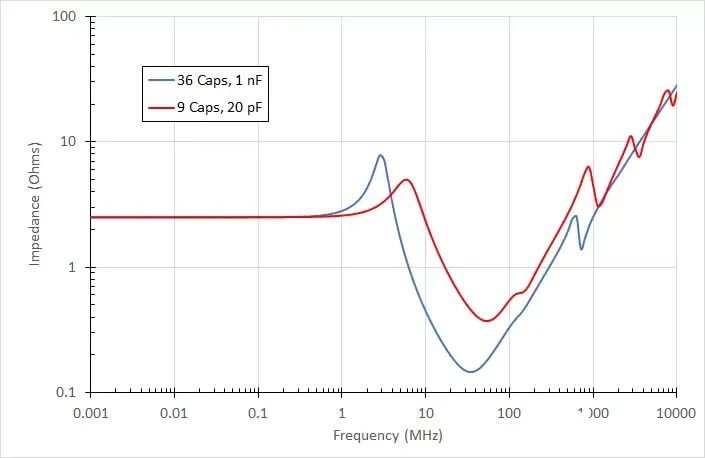

阻抗比較

我們還可以取頻域中復V/I響應函數的比率(AC掃描結果),然后計算該比率的大小以獲得PDN阻抗。我們可以看到PDN阻抗仍然偏大,尤其是在1/(升壓時間)帶寬限制附近。在查看PDN阻抗頻譜時,我們也可以看到其優勢,如下所示。下圖將36 decaps/1 nF的當前情況與之前的9 decaps/20 pF情況進行了比較。

PDN阻抗仿真結果對比

請注意,在大約10年內,我們能達到低阻抗(100 mOHM)。我們希望這個低阻抗頻帶更低更寬。我們還有一些在3MHz左右的峰值和630MHz的高頻響應。為了解決這些問題,我們可能需要更多數量和多樣性的電容器。我們可以使用一些其他技巧,例如在層過渡到IC期間增加過孔數,因為這會減少PWR_IN輸入級的總電感,而我們可以在SPICE仿真中反映這一點。 實際上,在高IO計數IC中,具有36個低ESL/低ESR電容器很常見;當然,在單脈沖中會產生720mA電流的IC中也是如此。事實上,如果您查看一些使用具有高IO計數的高速元件的參考設計或評估產品,您會發現36個去耦電容器是一個較低的數字。僅供參考,此脈沖的dI/dt值為720MA/秒(即每秒720兆安!),這是一個龐大的數字,需要許多電容器快速放電。在這種薄平面分離電介質上嵌入電容材料也會增加平面電容。

為什么是“小型”電路板?

什么才算是“小型”PDN?請記住,當負載切換時,寬帶電流脈沖被拉入PDN,并且該脈沖以光速沿PDN傳播。將其視為一種傳播信號,但它承載的是能量而不是數據。在小型PDN的限制下,我們可以像在傳輸線中一樣忽略傳播效應。事實上,傳輸線比較在這里是恰當的,PDN有時被描述為使用與傳輸線相同的集總電路模型。 當傳輸功率脈沖中具有最大頻率元件的波長遠大于標稱電路板尺寸時,我們可以忽略傳輸功率必須從穩壓器輸出傳播到負載輸入這一事實。這與理解為什么我們可以在傳輸線中定義臨界長度的邏輯相同。一旦設計過大,或者當相關帶寬達到非常高的頻率時,將需要電磁求解器來運行完整的PDN阻抗仿真并提取瞬態響應。

缺少什么?

精明的設計工程師應該注意到一些重要的事情:我們沒有將耗散包括在平面電容中!這引用了介電常數的虛部,通過將一些與平面電容串聯的電阻相加來實現建模目的。它在傳輸線的阻抗方程中基本上起著與G相同的作用。此電阻的大小需要一些額外的計算,這將取決于分隔平面層的介電材料的損耗量。在下一篇關于電源平面諧振的文章中,我們將能夠看到層壓板中高損耗切線的有益影響。

我們還能仿真什么?

上方結果清楚地顯示了增加電容如何降低PDN阻抗并有助于穩定內芯電壓。上述電容器僅為隨機選擇,并非基于針對特定頻率范圍的全面分析。如果我們通過這項練習并在更寬的帶寬上降低PDN阻抗,就能收獲更好的結果。 我們可以在SPICE中仿真的其他一些點包括:

我們已經通過計算輸入和輸出端口的阻抗,得出PDN的S參數

拉入PDN的任何電流脈沖的脈沖響應

PDN中多軌之間的傳輸阻抗

額外電感影響,例如在電源引腳上添加鐵氧體;我們將在即將發表的文章中對此進行探討

將旁路電容器直接添加到負載的電源輸入中(與Q1并聯)

Altium Designer中的內置SPICE包可以幫助您執行一系列仿真,包括PDN仿真。當您準備將這些文件發布給您的協作者進行更高級的仿真時,Altium 365平臺可以輕松協作和共享您的項目。您可以在一個軟件包中找到設計和生產高級電子產品所需的一切。

博客作者:Zachariah Peterson

-

pcb

+關注

關注

4280文章

22690瀏覽量

392035 -

阻抗

+關注

關注

17文章

914瀏覽量

45642 -

仿真

+關注

關注

50文章

3938瀏覽量

132818 -

SPICE

+關注

關注

5文章

175瀏覽量

42357 -

PDN

+關注

關注

0文章

72瀏覽量

22624 -

Altium Designer

+關注

關注

47文章

390瀏覽量

44590

原文標題:SPICE中的PDN阻抗仿真與分析

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

LM339官網TINA-TI spice模型仿真參考設計TSC與插入TSM模型仿真結果不一致,為什么?

LMH3401 spice模型在cadence中仿真SFDR較差是什么原因?

PDN 元件對阻抗的影響

搞定電源完整性,不如先研究PDN!

請問一下spice仿真怎么產生時鐘信號呢?

SPICE仿真類型有哪些

利用SPICE模型能不能進行PCB的SI仿真?

AD539沒有spice模型,該如何仿真?

怎么通過SPICE仿真來預測VDS開關尖峰?

電源完整性之PDN仿真有哪些注意事項?

SPICE中的PDN阻抗仿真與分析

SPICE中的PDN阻抗仿真與分析

評論