一. 晶振原理概述

在數(shù)字的世界里,無處不需要時鐘,各種振蕩電路的設(shè)計可以實現(xiàn)片內(nèi)的集成,但是要實現(xiàn)高精度的時鐘頻率,晶體振蕩器是很好的選擇,時鐘頻率精度可以達(dá)到ppm級別。

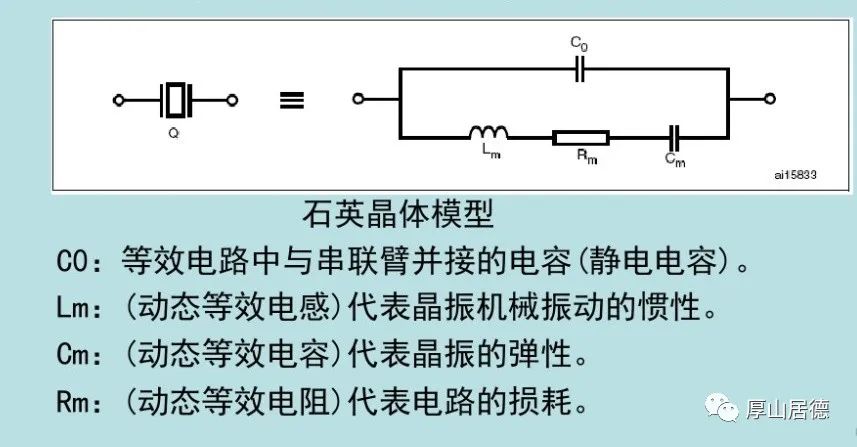

石英晶體是一種將電能和機(jī)械能相互轉(zhuǎn)化的壓電器件,能量的轉(zhuǎn)變發(fā)生在共振頻率點上。石英晶體可以等效為電阻電容電感的串并聯(lián)模型。

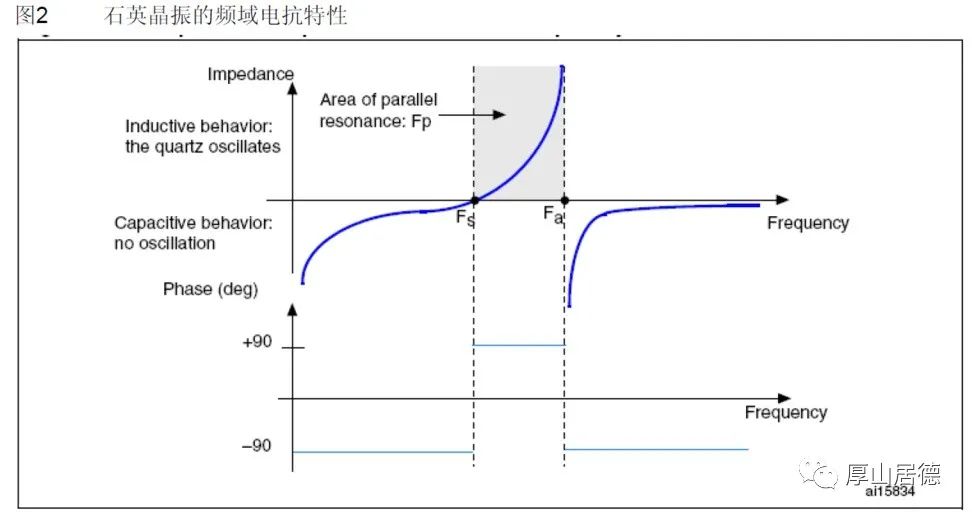

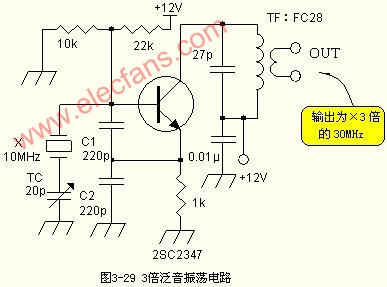

對于如上圖所示的模型,可以得到晶振的阻抗和頻率的關(guān)系圖。

晶振的串聯(lián)諧振頻率為Fs, 并聯(lián)諧振頻率為Fa,在小于Fs和大于Fa的頻率,表現(xiàn)為電容性,而在Fs和Fa之間,表現(xiàn)為電感性。對于晶振電路,希望工作在Fs和Fa之間,而靠近Fs的地方。

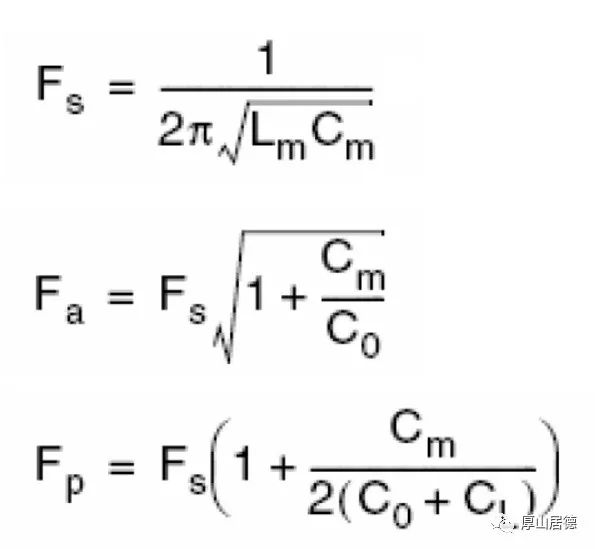

在Fs到Fa之間的區(qū)域,稱為晶振的“并聯(lián)諧振區(qū)”,在這一區(qū)域晶振工作在并聯(lián)諧振狀態(tài)。晶振呈現(xiàn)電感特性,帶來了180度的相移。頻率的表達(dá)式為:

Fp就是我們晶振工作的頻率,由于Fp中,其他參數(shù)確定,唯有Cl值可以調(diào)節(jié),所以可以通過調(diào)整晶振的負(fù)載電容值Cl達(dá)到調(diào)節(jié)頻率的目的。并且一般的溫度補(bǔ)償晶振電路也是通過調(diào)節(jié)Cl的值達(dá)到目的。

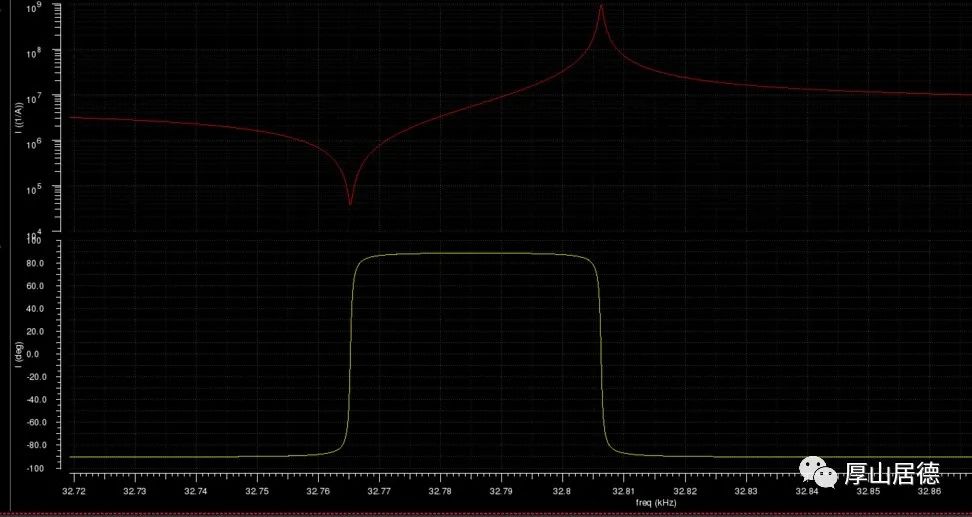

對于一個32.768K的晶振,按照模型參數(shù)仿真,對晶體模型兩端加交流信號,可以仿真得到其阻抗隨頻率的曲線。和理論值一致。

二. 晶體振蕩電路的設(shè)計

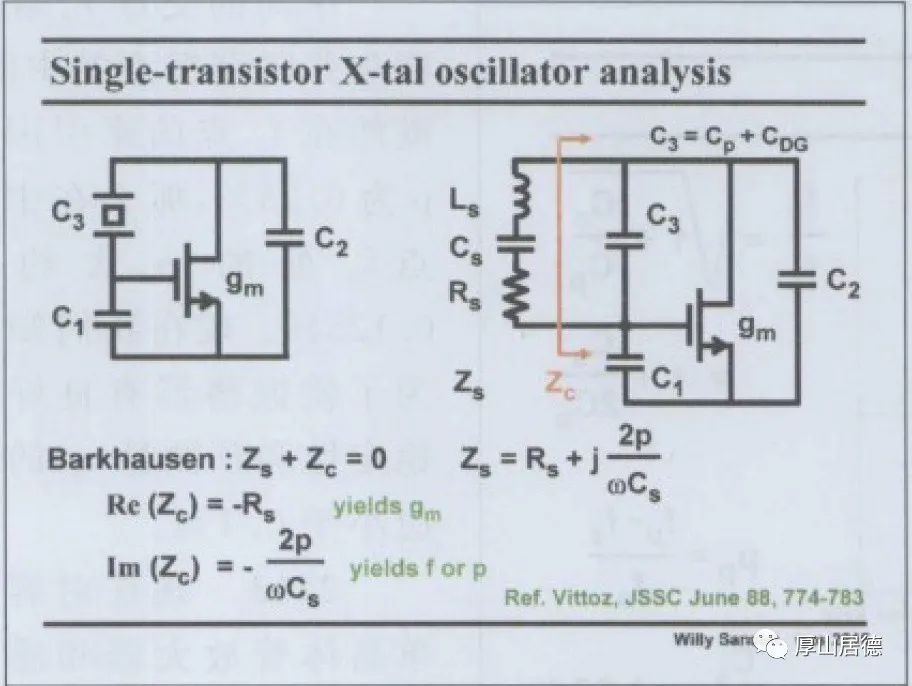

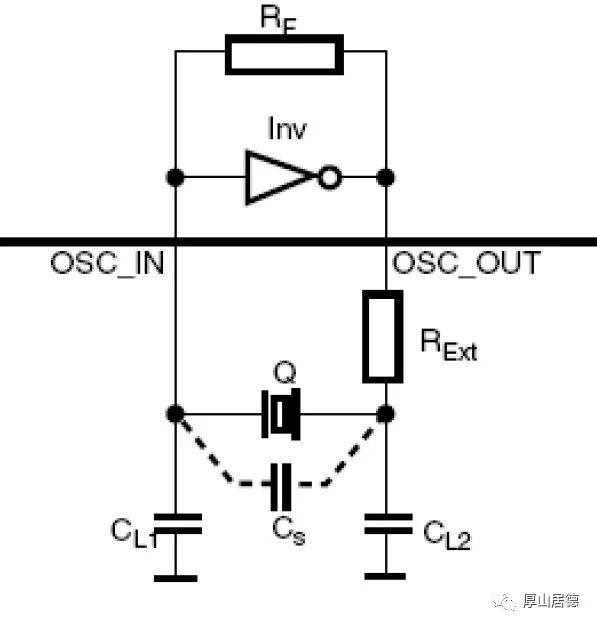

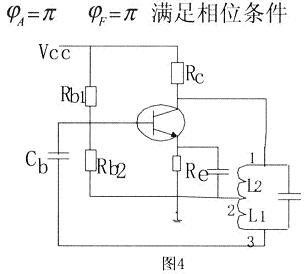

在晶體振蕩電路中,最常見的結(jié)構(gòu)為Pierce振蕩器。而對晶體振蕩電路的分析,第一是使用負(fù)阻的概念,第二是使用增益與相位原理。

今天只說負(fù)阻法。

由于前面的分析,得到晶振在串聯(lián)諧振頻率處阻抗為Rs,則需要振蕩電路提供-Rs的阻抗。而晶振發(fā)生了180的相移,在振蕩頻率出表現(xiàn)為電感的特性,則需要振蕩電路提供電容的特性。

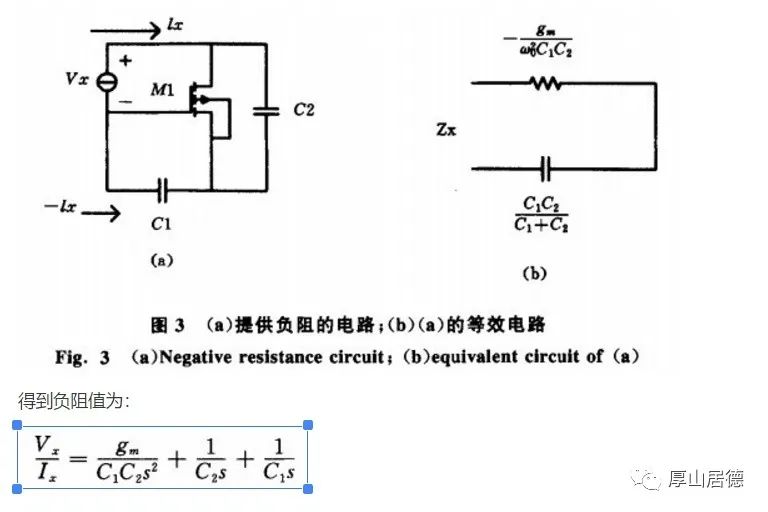

對于Pierce振蕩電路的負(fù)阻的計算,如下圖,在Razavi的書中有描述。

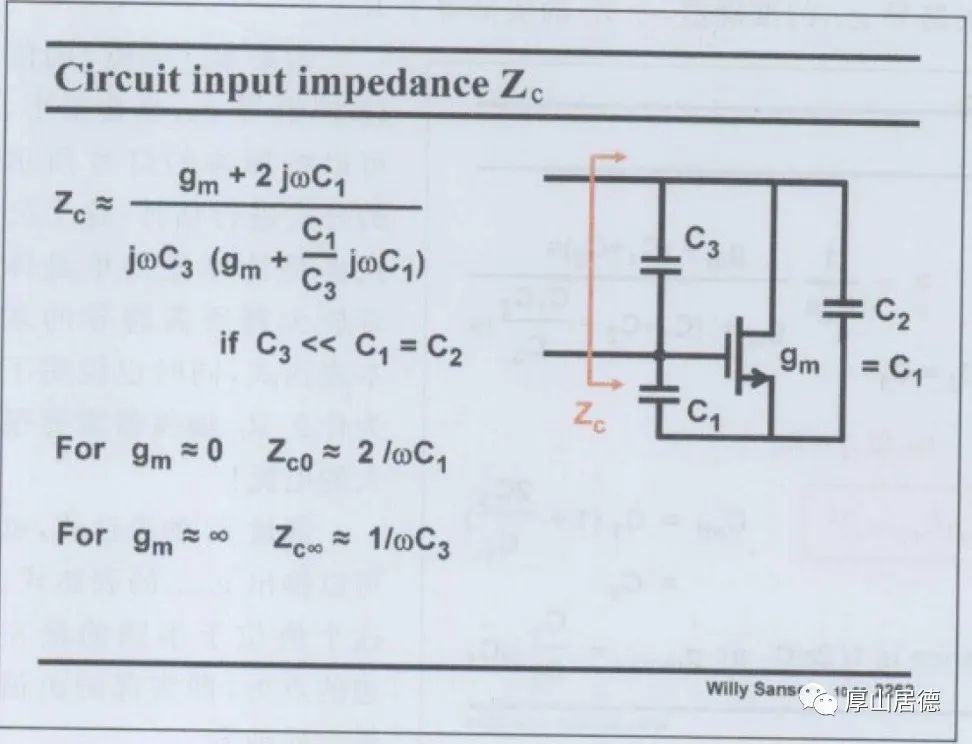

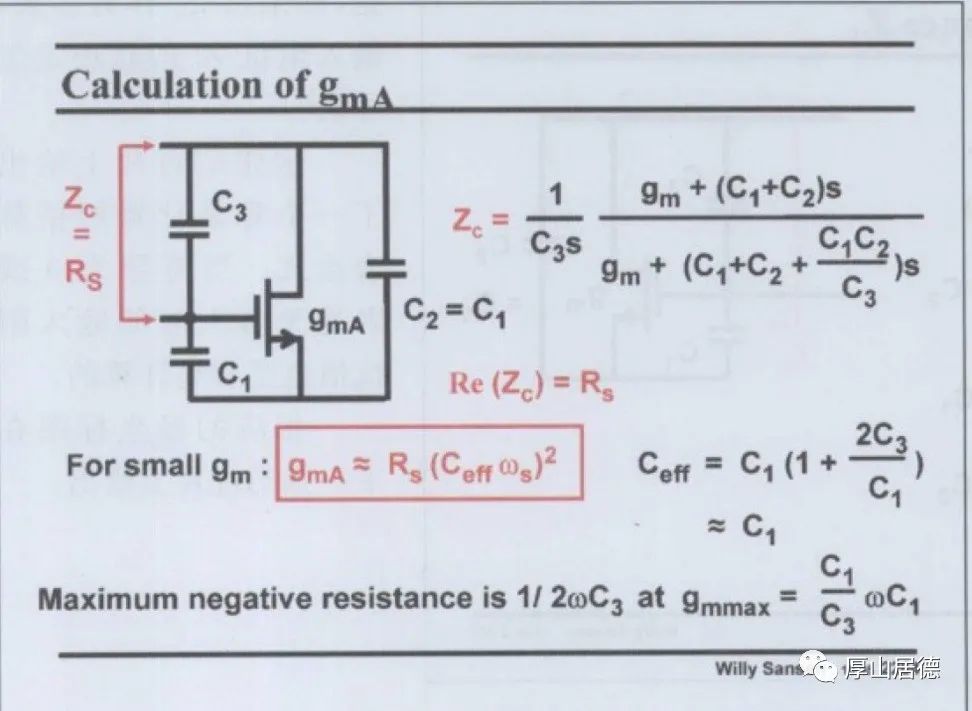

而在實際的應(yīng)用中,還包括由晶振的C0以及MOS的Cgd和pcb上的雜散電容等形成的電容C3, 包含C3的電路的阻抗如下圖所示。

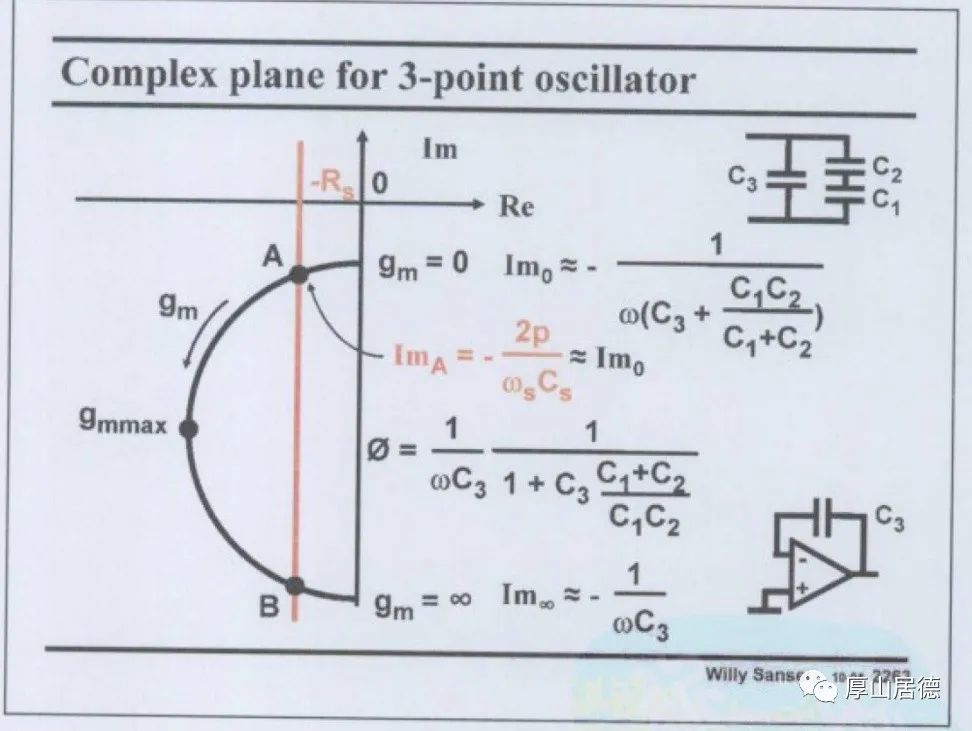

Zc值是一個關(guān)于gm的函數(shù),取Zc的實部,得到的即是振蕩電路的負(fù)阻值。關(guān)于Zc在復(fù)平面上,得到下面的圖。

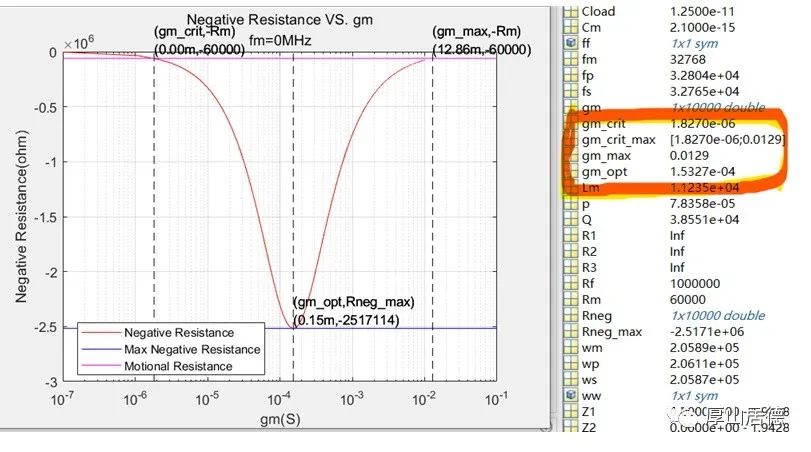

到這里,維持電路起振所需要的gm值可以近似計算出來,也可以通過matlab對上面的式子求解,得到精確的值。近似計算和matlab得到的值相差不大。

在Sanser的書中,近似計算表達(dá)式如下圖,包括gma, gmmax,以及最大負(fù)阻值。(此公式可以容易地近似計算。)

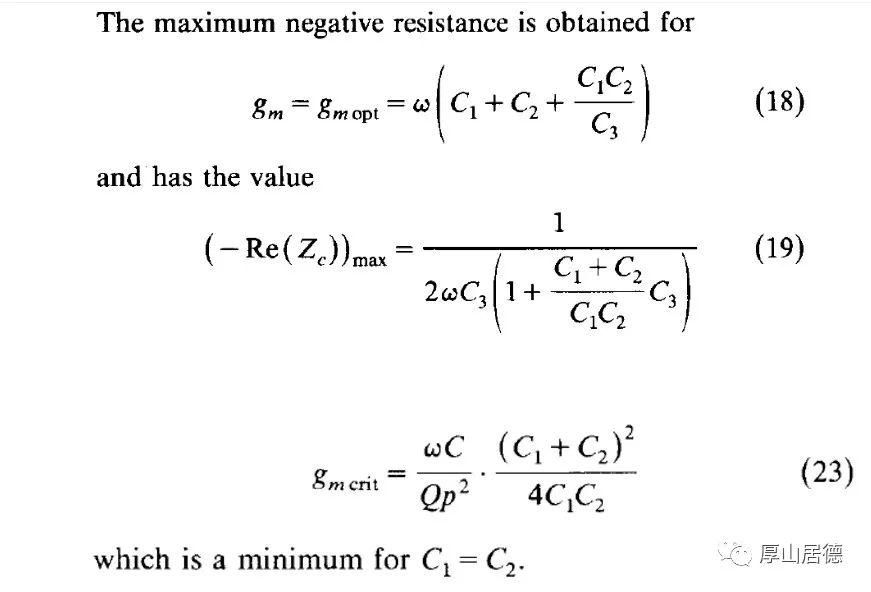

而在vittoz的論文中,給出的計算公式,可以精確計算出所需值。

設(shè)計示例:

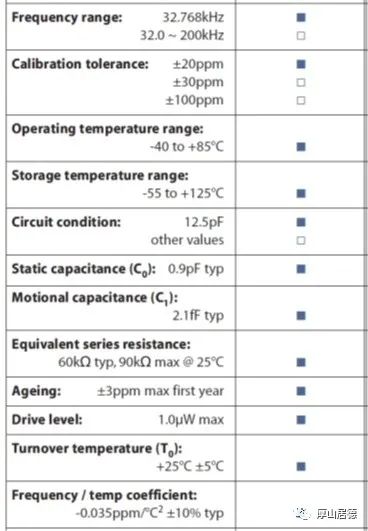

下面給一個設(shè)計example。一個32.768K的晶振,datasheet上給出的參數(shù)為

從表中得到:C1=C2=2*Cload=25pF, C0=0.9pF, Cs=2.1fF, Rs=60K.

使用matlab計算得到的值為

使用sansen書中的公式計算得到的值為:

gm_crit=1.6u, gm_max=12.9m, gm_opt=143u,

和matlab的計算值基本很接近,可以作為近似計算。

使用Vittoz論文中的公式計算得到的值為:

gm_crit=1.8266u, gm_max=12.9m, gm_opt=153.27u,

和matlab的計算值一致。

確定了電路的gm_crit值,也就是電路能起振的最小值后,在電路設(shè)計中,取實際的gm值約510倍gm_crit.即取gm約10u20u。

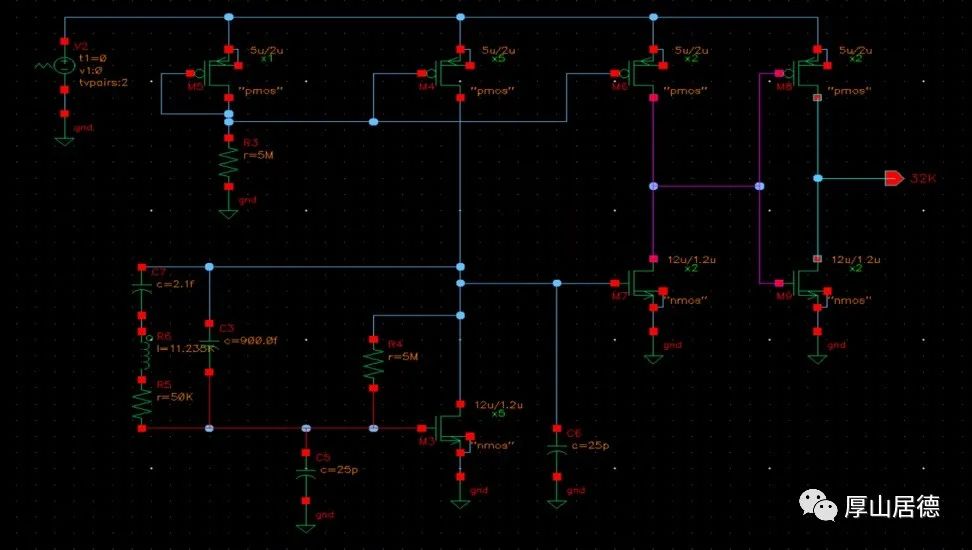

實際電路設(shè)計及仿真:

假設(shè)電路使用電流源驅(qū)動NMOS管。對于這類電路設(shè)計,一般提供gm的nmos管處于亞閾值區(qū),所以gm值主要與電流值成正比。

如果gm值按照計算出來的gm_opt取值,則需要的電流值大約,而在低功耗設(shè)計中,一般取5倍以上的最小gm值即可。本設(shè)計示例按照10倍取值,即gm=16uA/V。 仿真輸入輸出的gm=16uA/V, 穩(wěn)態(tài)電流為1uA。同時仿真其負(fù)阻值為-510K, 大約也是10倍的晶振ESR電阻。

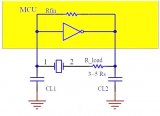

gm的仿真:輸入加AC電壓,加交流開關(guān)斷開直流,輸出利用交流開關(guān)接到地,測試輸出的交流電流值。

負(fù)阻的仿真:輸入輸出加交流電流,測量輸入輸出的交流電壓差,并使用計算器取實部(real函數(shù)),即可。也可以使用sp仿真,得到Z11的值。

最后對晶振電路進(jìn)行瞬態(tài)仿真,可以觀察晶振的起振過程。注意瞬態(tài)仿真時需要設(shè)置step=10ns。

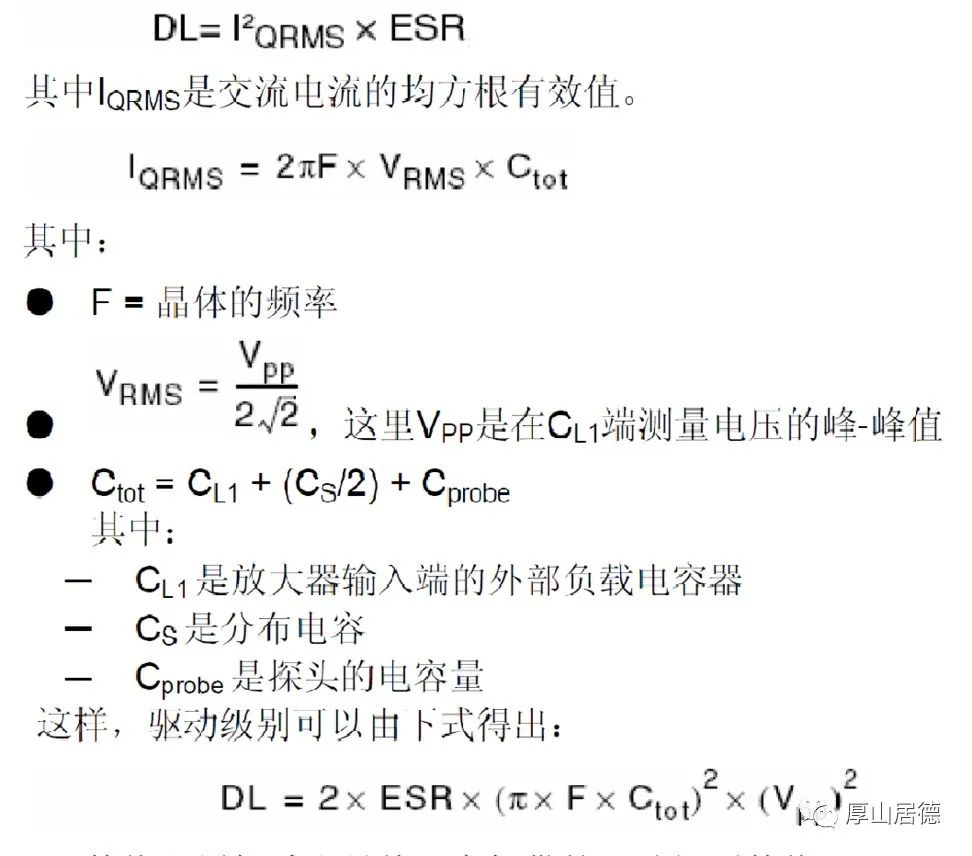

晶振的DL:

還有一個重要的參數(shù)就是晶振的驅(qū)動級別DL,如果設(shè)計的電路,使得晶振的DL大于晶振要求的DL值,則晶振可能會損壞。

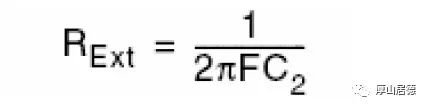

在晶振電路的設(shè)計中,最常見的一種電路結(jié)構(gòu)如下圖,可以看成一個反相器加反饋電阻做放大器,而外部的Rext的作用就是限制DL值。Rext的值可以用公式計算。

加入Rext后需要重新驗證電路的gm值和負(fù)阻值是否滿足起振要求。

設(shè)計要點總結(jié):

1.按照晶振的規(guī)格計算電路的gm值。

- 按照要求設(shè)計電路。

- 考慮DL,是否需要加入Rext電阻。

- 重新驗證,整體仿真。

-

晶體振蕩器

+關(guān)注

關(guān)注

9文章

616瀏覽量

29061 -

溫度補(bǔ)償電路

+關(guān)注

關(guān)注

0文章

21瀏覽量

10713 -

負(fù)載電容

+關(guān)注

關(guān)注

0文章

137瀏覽量

10430 -

晶體振蕩電路

+關(guān)注

關(guān)注

0文章

29瀏覽量

6204 -

NMOS管

+關(guān)注

關(guān)注

2文章

120瀏覽量

5398

發(fā)布評論請先 登錄

相關(guān)推薦

單片機(jī)振蕩電路晶振不起振原因分析與解決方法

【轉(zhuǎn)帖】晶振振蕩電路設(shè)計經(jīng)驗總結(jié)

晶振負(fù)載電容外匹配電容計算與晶振振蕩電路設(shè)計經(jīng)驗總結(jié)

三點式振蕩電路能否振蕩的判別方法

石英晶振振蕩電路的設(shè)計概述

《振蕩電路的設(shè)計與應(yīng)用》

由74HC04組成的并聯(lián)諧振振蕩電路

簡析晶振振蕩電路的設(shè)計資料下載

如何結(jié)合晶振的負(fù)載電容計算外匹配電容容值以及在晶振振蕩電路設(shè)計時需注意哪些事項?資料下載

晶振振蕩電路的設(shè)計方法和步驟

晶振振蕩電路的設(shè)計方法和步驟

評論