華為意大利研究中心與瑞士蘇黎世理工學(xué)院系統(tǒng)集成實驗室聯(lián)合發(fā)表了一篇論文《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》透露出華為或許正在開發(fā)下一代基于RISC-V的車載MCU,論文發(fā)表于2023年7月。目前,華為海思已有兩款基于RISC-V的芯片,分別是Hi3731v110和Hi3861,其中前者是一款全球模擬電視用芯片,后者就近似MCU。海思目前還在開發(fā)數(shù)據(jù)中心用RISC-V芯片,可能是AI加速器。

與華為同樣思路的還有瑞薩,瑞薩是全球第一大MCU廠家,也是RISC-V MCU投入力度最大的廠家。早在2021年,瑞薩就有RH850/U2B 汽車MCU采用RISC-V內(nèi)核的DR1000CCPU IP,這款I(lǐng)P來自日本豐田關(guān)聯(lián)公司電裝旗下的NSITEXE公司(成立于2017年,最初是電裝的一個實驗室,后從電裝剝離)。

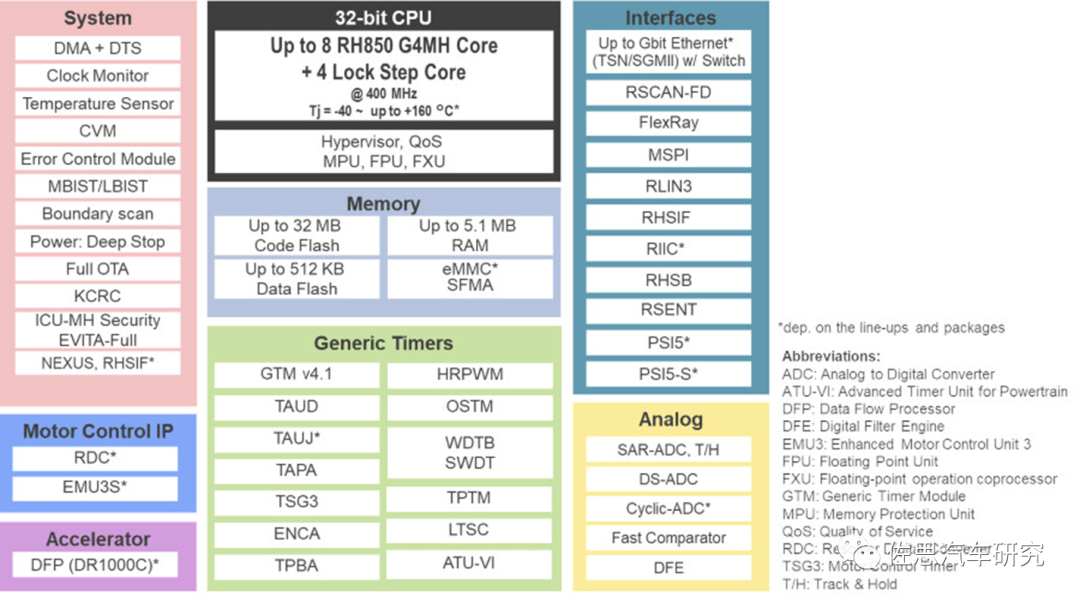

瑞薩RH850/U2B內(nèi)部框架

圖片來源:Renesas

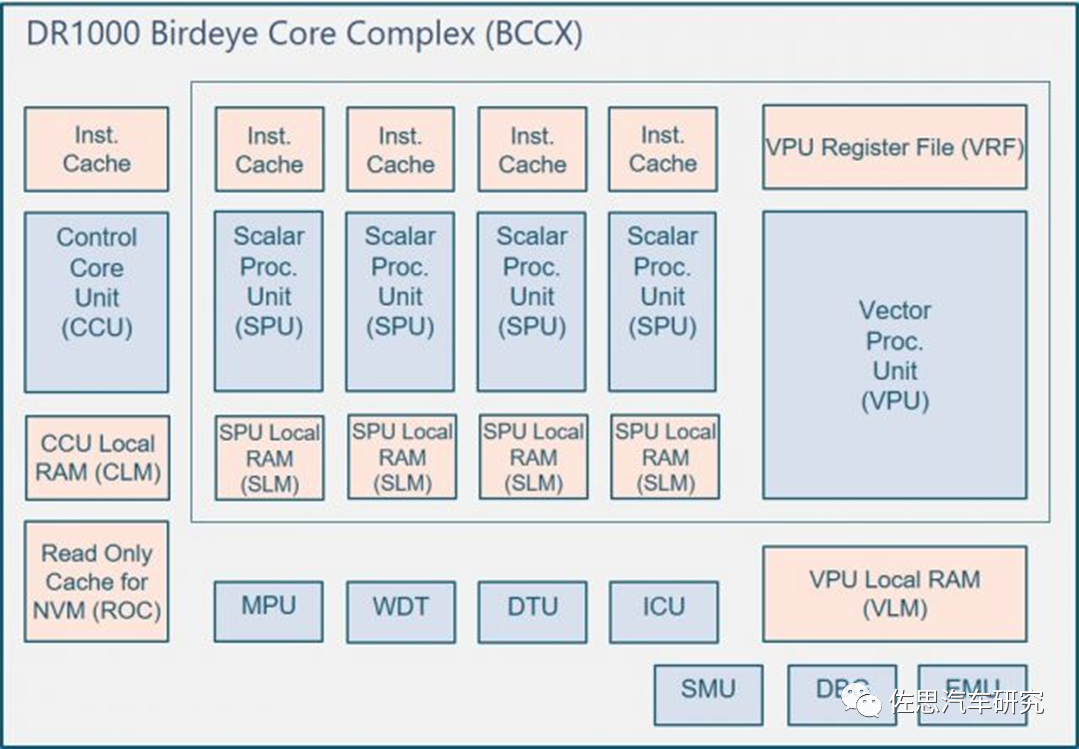

DR1000C內(nèi)部框架圖

DR1000C主要是加入了矢量計算單元。圖片來源:NISTEXE

除了RH850/U2B,瑞薩還有眾多32/64 bit的基于RISC-V內(nèi)核的MCU,包括非車載領(lǐng)域的RZ/Five系列(AX45MP@1.0GHz,附帶SIMD的FPU),語音HMI的R9A06G150,三相電機控制R9A02G020。

簡單介紹一下RISC-V。RISC-V中,RISC指的是精簡指令集架構(gòu)。指令集架構(gòu)(Instruction Set Architecture)是指一種類型CPU中用來計算和控制計算機系統(tǒng)的一套指令的集合。

指令集架構(gòu)主要規(guī)定了指令格式、尋址訪存(尋址范圍、尋址模式、尋址粒度、訪存方式、地址對齊等)、數(shù)據(jù)類型、寄存器。

指令集通常包括三大類主要指令類型:運算指令、分支指令和訪存指令。此外,還包括架構(gòu)相關(guān)指令、復(fù)雜操作指令和其他特殊用途指令。因此,一種CPU執(zhí)行的指令集架構(gòu)不僅決定了CPU所要求的能力,而且也決定了指令的格式和CPU的結(jié)構(gòu)。X86架構(gòu)和ARMv8架構(gòu)就是指令集架構(gòu)的范疇。指令集架構(gòu)依其復(fù)雜性可被分類為復(fù)雜指令集架構(gòu)(CISC,Complex Instruction Set Computer)和精簡指令集架構(gòu)(RISC,ReducedInstruction Set Computer)兩大類。發(fā)展至今,CISC和RISC的界限已變得模糊,二者互吸收了各自的優(yōu)點,變得你中有我,我中有你。

2010 年,RISC構(gòu)思在加州大學(xué)伯克利分校啟動,是一個用于開發(fā)芯片處理器的免費、非專有平臺。RISC的發(fā)源也是在伯克利,但RISC不是開源的。

2015年,RISC-V基金會成立,旨在建立一個基于RISC-V ISA的開放、協(xié)作的軟硬件創(chuàng)新者社區(qū)。該基金會是一家由其成員控制的非營利公司,負責(zé)指導(dǎo)開發(fā)以推動 RISC-V ISA 的初步應(yīng)用。

2020年3月,RISC-V基金會遷往瑞士,解決了受地緣政治干擾的風(fēng)險。RISC-V是開源的,這意味著 RISC-V 是免許可和免版稅的。RISC-V允許用戶免費使用新指令擴展ISA并創(chuàng)新RISC-V處理器的微架構(gòu),而當(dāng)前汽車業(yè)內(nèi)主流的ARM架構(gòu),要求用戶支付版稅。這使得RISC-V迅速受到眾多廠商的歡迎。

當(dāng)前主流的ARM 需要 IP 核許可批準,ARM的商品一是指令集,二是內(nèi)核架構(gòu)。不過ARM的內(nèi)核架構(gòu)自然要用ARM的指令集,買了ARM的內(nèi)核架構(gòu)自然就包含ARM指令集,或者也可以單獨設(shè)計物理架構(gòu),而只使用ARM的指令集,如蘋果一直以來都是如此。而高通、華為等則是直接買架構(gòu)。

ARM指令集的費用為100萬美元到1000萬美元之間。此外,如果您想更改設(shè)計中的任何內(nèi)容,將需要另外付費,當(dāng)然可以花上千萬美元一次性買斷內(nèi)核架構(gòu),這就不需要另外付費。另外每生產(chǎn)一塊芯片,ARM都要收取1-3%芯片價格的費用。ARM有大約60%的收入來自版稅,40%的收入來自IP授權(quán)。2023財年ARM的版稅收入只有16.8億美元,僅占芯片價值的1.7%。不過版稅的優(yōu)點在于一次開發(fā),一生收稅,舊芯片能帶來持續(xù)收入流。2023財年中,ARM約46%的版稅收入來自1990-2012年間發(fā)布的產(chǎn)品 。

RISC-V 是簡化ISA自下而上構(gòu)建的,可以處理最新的計算工作負載。而RISC-V與擁有數(shù)十年歷史且背負著遺留的指令專有架構(gòu)(X86和ARM)有很大不同。X86和ARM已經(jīng)持續(xù)運行了超30年,為應(yīng)對新應(yīng)用,指令集變得越來越龐大,效率越來越低,ARM早已不是當(dāng)年那個純粹的精簡指令。

最重要的是X86和ARM都是封閉的,廠家想要更改指令集完全不可能。在強調(diào)互聯(lián)互通的消費類電子領(lǐng)域,指令集由一家獨立公司完全掌控是優(yōu)勢;但在汽車領(lǐng)域是缺點,汽車是嵌入式領(lǐng)域,不用考慮互聯(lián)互通,各品牌之間完全不兼容是正常的,比如特斯拉的自然不會兼容比亞迪的軟件系統(tǒng)。也就是說,整車廠要掌握指令集才能做出自己的特色和體系,而這一點ARM和X86永遠無法提供,而目前ARM幾乎壟斷汽車產(chǎn)業(yè),這樣就造成了汽車芯片高度雷同,頭部廠家市場占有率極高。要打破這種現(xiàn)象,就必須使用RISC-V。

華為的研究工作剛開始,目前還是基于FPGA的研究。華為使用AMD旗下Xilinx的ZynqUltrascale+ FPGA,這款FPGA有4核ARM Cortex-A53,每核心有L1緩存32KiB,L2緩存1MiB,運行頻率1.2GHz,還有一個用于實時任務(wù)的ARM Cortex-R5F,RISC-V采用CVA6架構(gòu)。這種設(shè)計可以對比RISC-V和ARM之間的性能差別。

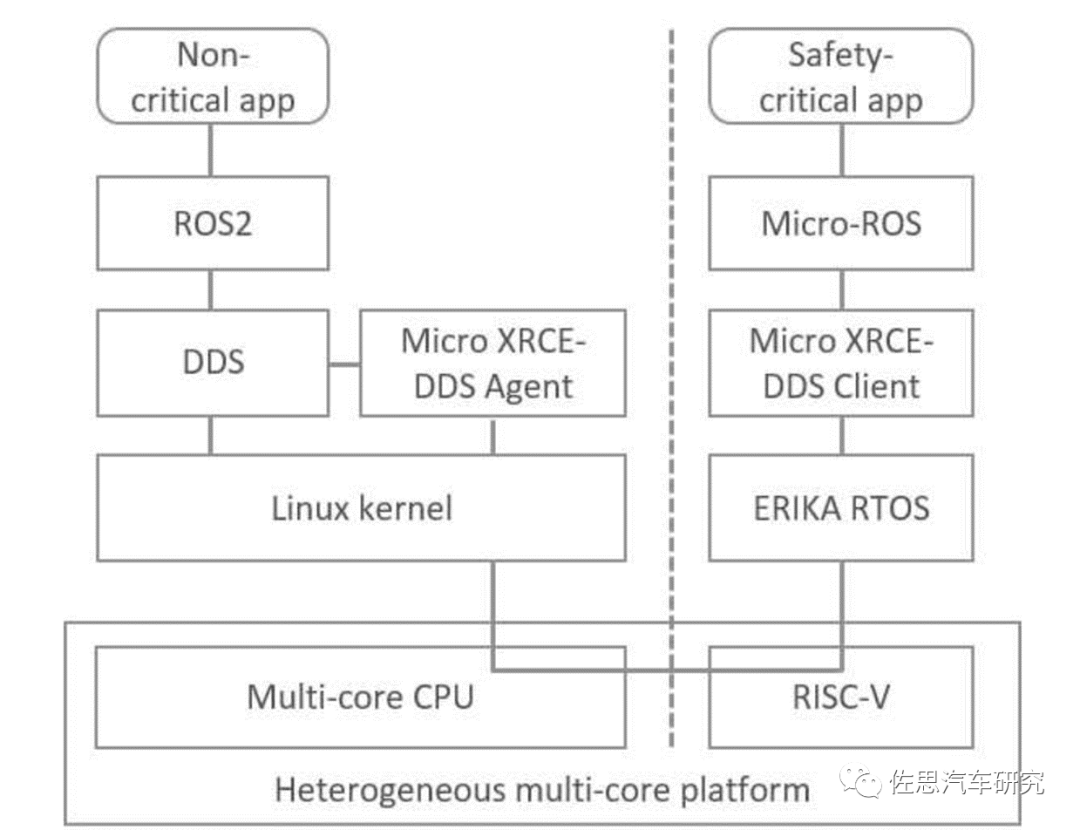

圖片來源:《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》

軟件架構(gòu)如上圖,非安全苛刻任務(wù)采用無人駕駛領(lǐng)域常見的ROS2,中間件采用DDS(數(shù)據(jù)分發(fā)服務(wù)),DDS負責(zé)管理分布式系統(tǒng)的數(shù)據(jù)和通信。DDS中間件協(xié)議基于對象管理組織(OMG)標準化的發(fā)布-訂閱模式。DDS已集成到各種關(guān)鍵的汽車平臺生態(tài)合作體系中,例如AUTOSAR Adaptive和ROS2。DDS提供低延遲數(shù)據(jù)連接、可靠性和可擴展的以數(shù)據(jù)為中心的通信。此外,DDS附帶了一組豐富的內(nèi)置服務(wù)質(zhì)量(QoS)策略,可控制DDS行為,如資源消耗和通信可靠性。面向資源極度受限環(huán)境的DDS通過使用OMG DDS-XRCE協(xié)議實現(xiàn)。這是客戶端到代理協(xié)議,意味著DDS-XRCE客戶端節(jié)點通過外部代理節(jié)點與DDS進行網(wǎng)絡(luò)通信。DDS-XRCE非常適合為物聯(lián)網(wǎng)設(shè)備開發(fā)輕量級DDS應(yīng)用。實時操作系統(tǒng)采用企業(yè)版ERIKA,這是一款免專利的汽車OSEK/VDX認證的硬實時操作系統(tǒng)(RTOS)。官網(wǎng)鏈接:http://www.erika-enterprise.com。

ERIKA主要特性

圖片來源:《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》

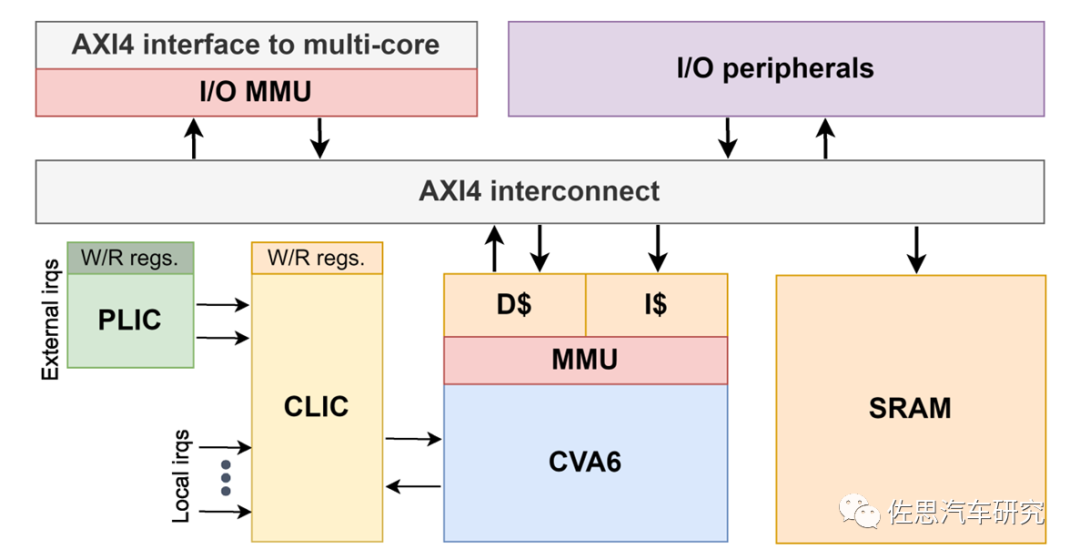

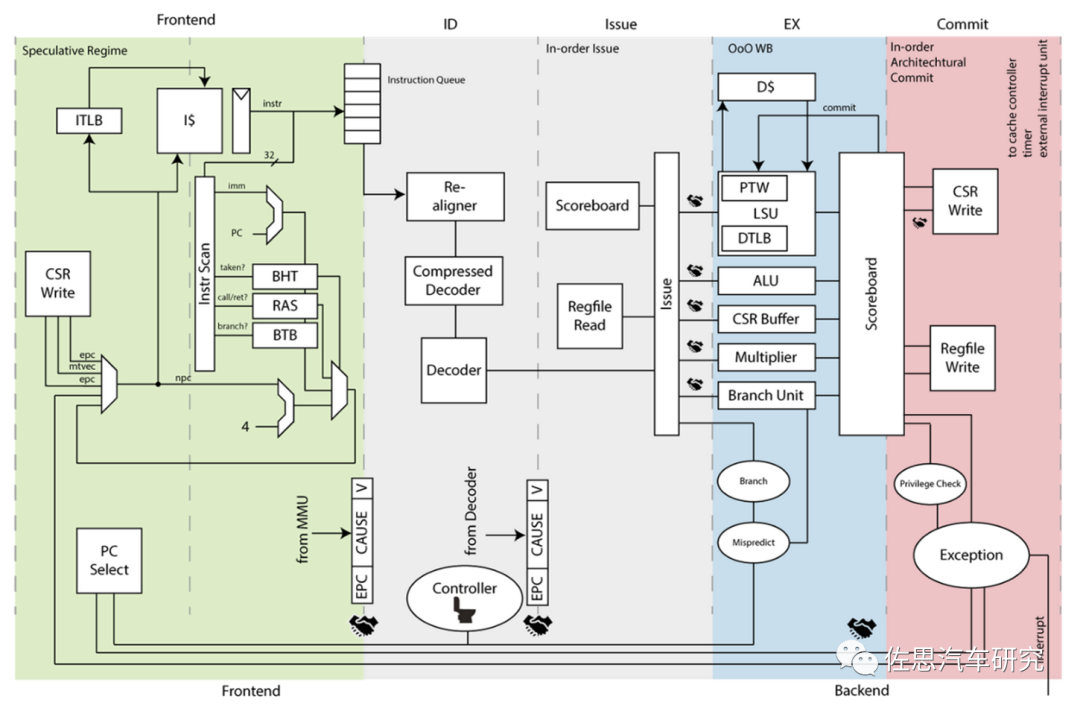

CVA6MCU結(jié)構(gòu)

圖片來源:《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》

CVA6架構(gòu)

CVA6是一顆具備6級流水、單發(fā)射、順序執(zhí)行的64bitRISC-V CPU,不僅實現(xiàn)了RV64IMAFDC(RV64GC)指令,也實現(xiàn)了RISC-V三種特權(quán)等級,因此具備運行Linux系統(tǒng)的能力。CVA6是蘇黎世理工學(xué)院與意大利博洛尼亞大學(xué)聯(lián)合的OPENHW機構(gòu)維護的開源硬件IP。順便說一句,博洛尼亞大學(xué)是全球最古老的大學(xué),成立于公元1088年,目前在意大利排名第五。

CVA6實現(xiàn)了RISC-V的三種特權(quán)模式,分別是機器模式(M-MachineMode)、監(jiān)督模式(S-Supervisor Mode)、用戶模式(U-User Mode);具備ITLB、DTLB、PTW實現(xiàn)虛擬地址到物理地址的快速翻譯;具備可靈活配置的4路組相連L1ICache與L1DCache。官方(即OPENHW)基于22nm-FDSOI流片,運行頻率可達1.7GHZ。

CVA6核心部分僅具有L1Cache,為了提高流水線效率,L1Cache又分為ICache、DCache。 L1ICache的默認配置是:

cache size:16Kib;

cache lines:128bit;

Associativity:Four-way set;

Replacement policies:使用LFSR進行隨機替換。

CVA6僅具有L1Cache,但結(jié)合Princeton開源的OpenPiton,可以拓展L2Cache。

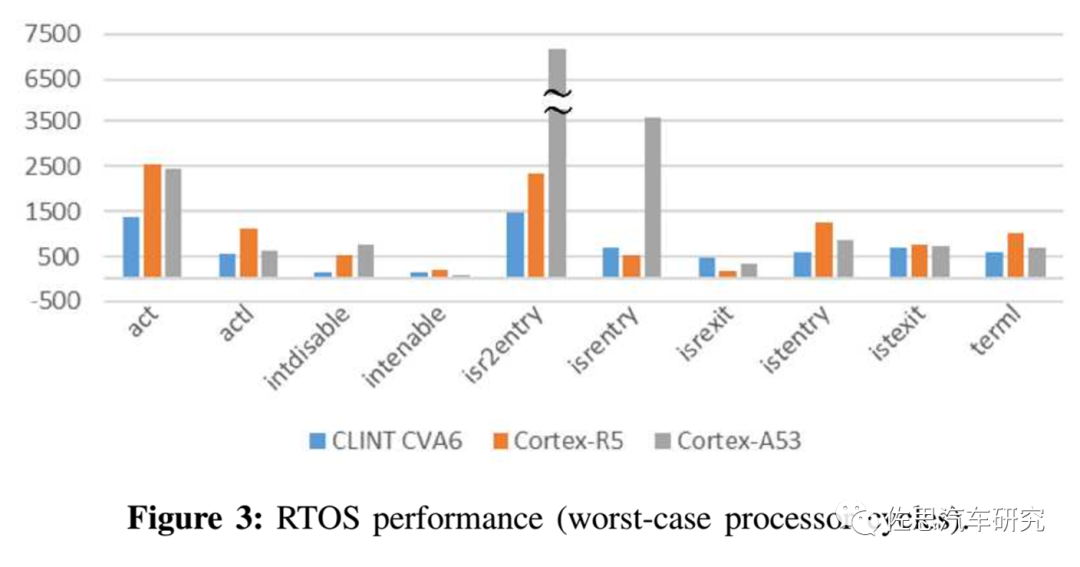

CLINTCVA6、Cortex-R5和Cortex-A53的RTOS性能對比

圖片來源:《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》

上圖,RTOS下表現(xiàn),RISC-V的CVA6全面勝出。

2023年8月,汽車行業(yè)四巨頭和挪威NORDIC半導(dǎo)體公司聯(lián)合投資建立一家致力于RISC-V的芯片公司,算是后知后覺者了。

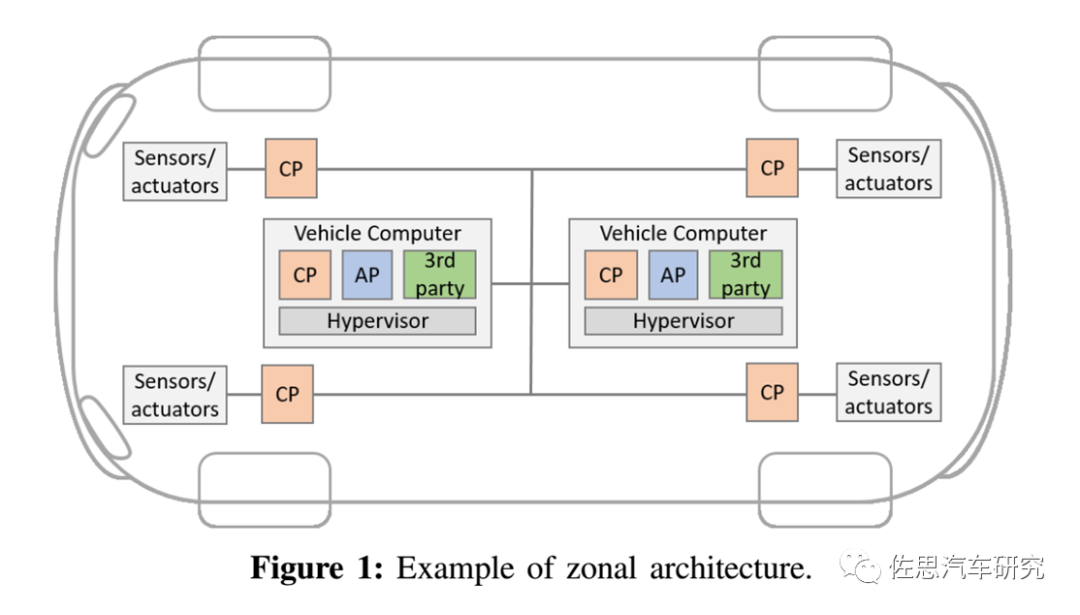

圖片來源:《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》

Zonal或者說SOA時代,對MCU的運算要求越來越高,同時還要應(yīng)對苛刻的功能安全以及復(fù)雜的操作系統(tǒng)、中間件和虛擬機,ARM的CORTEX-R系列已明顯力不從心,RISC-V將是未來高性能汽車MCU的首選。

-

mcu

+關(guān)注

關(guān)注

146文章

17019瀏覽量

350373 -

華為

+關(guān)注

關(guān)注

216文章

34327瀏覽量

251218 -

RISC-V

+關(guān)注

關(guān)注

44文章

2233瀏覽量

46045

原文標題:華為開發(fā)下一代基于RISC-V的車載MCU

文章出處:【微信號:zuosiqiche,微信公眾號:佐思汽車研究】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

RISC-V MCU開發(fā) (一):集成開發(fā)環(huán)境

擁抱RISC-V的開發(fā)世界 兆易創(chuàng)新推GD32VF103系列RISC-V MCU

改變加速器格局,下一代千核RISC-V芯片

RISC-V中***會子活動之一:基于RISC-V的鴻蒙開發(fā)板設(shè)計

RISC-V MCU開發(fā) (一):集成開發(fā)環(huán)境

用Java開發(fā)下一代嵌入式產(chǎn)品

RISC-V MCU開發(fā)相關(guān)資料分享

RISC-V MCU開發(fā)相關(guān)資料分享

RISC-V MCU開發(fā)的相關(guān)資料分享

RISC-V MCU開發(fā)實戰(zhàn)(一) :DHT11

英特爾與豐田聯(lián)合研發(fā)下一代車載信息娛樂系統(tǒng)

電裝將與高通共同開發(fā)下一代座艙系統(tǒng)

RISC-V MCU開發(fā)(一):集成開發(fā)環(huán)境

關(guān)于RISC-V MCU開發(fā)實例(一):環(huán)境搭建

KYOCERA AVX和VisIC Technologies合作開發(fā)下一代電車應(yīng)用GaN技術(shù)

華為開發(fā)下一代基于RISC-V的車載MCU

華為開發(fā)下一代基于RISC-V的車載MCU

評論