SoC(System on-chip)與NoC(network-on-chip)

NoC是相對于SoC的新一代片上互連技術,要深入了解NoC必須深刻認識SoC,故本文組織結構為:

l SoC架構

l SoC的局限性

l SoC設計流程

l NoC架構

l NOC架構優勢

l NoC 和 SoC 的區別

一.SoC基本架構

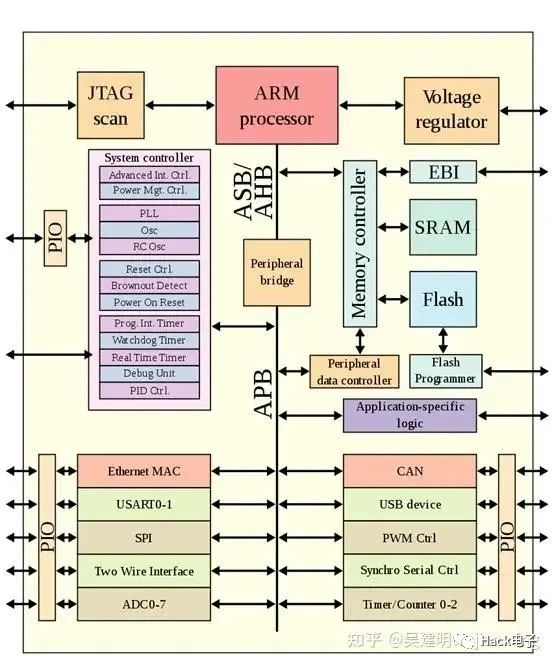

典型的系統級芯片結構包括以下部分:

·至少一個微控制器(MCU)或微處理器(MPU)或數字信號處理器(DSP),但是也可以有多個處理器內核;

·存儲器可以是RAM、ROM、EEPROM和閃存中的一種或多種;

·由計數器和計時器、電源電路組成的外設;

·不同標準的連線接口,如USB、火線、以太網、通用異步收發和序列周邊接口等;

·電壓調理電路及穩壓器。

片上系統通訊架構(System on chip, SoC)SoC整體架構圖如下:

二.SoC的局限性

目前,SoC通訊架構的設計相對比較成熟。大部分芯片公司芯片制造都采用SoC架構。然而,隨著商業應用開始不斷追求指令運行并存性和預測性,芯片中集成的核數目將不斷增多,基于總線架構的SoC將逐漸難以不斷增長的計算需求。其主要表現為:

1、可擴展性差。SoC系統設計是從系統需求分析開始,確定硬件系統中的模塊。為了使系統能夠正確工作,SoC中各物理模塊在芯片上的位置是相對固定的。一旦在物理設計完畢后,要進行修改,實際上就有可能是一次重新設計的過程。另一方面,基于總線架構的SoC,由于總線架構固有的仲裁通信機制,即同一時刻只能有一對處理器核心進行通信,限制了可以在其上擴展的處理器核心的數量。

2、平均通信效率低。SoC中采用基于獨占機制的總線架構,其各個功能模塊只有在獲得總線控制權后才能和系統中其他模塊進行通信。從整體來看,一個模塊取得總線仲裁權進行通信時,系統中的其他模塊必須等待,直到總線空閑。

3、單一時鐘同步問題。總線結構要求全局同步,然而隨著工藝特征尺寸越來越小,工作頻率迅速上升,達到10GHz以后,連線延時造成的影響將嚴重到無法設計全局時鐘樹的程度,而且由于時鐘網絡龐大,其功耗將占據芯片總功耗的大部分。

三.SoC設計流程

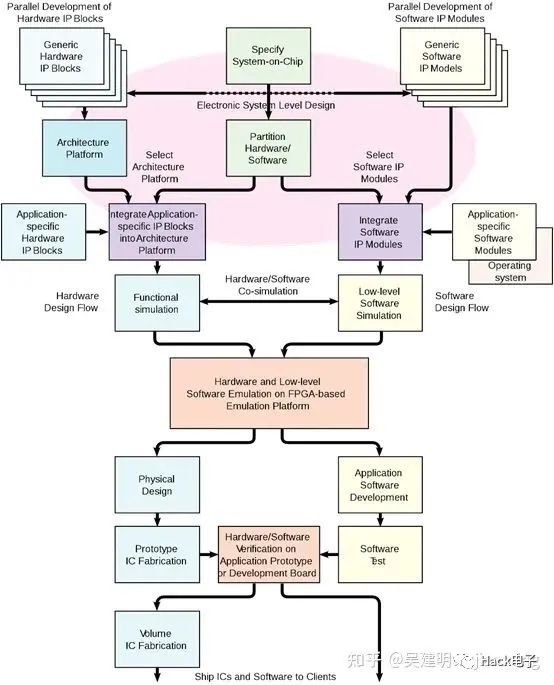

一個完整的系統級芯片由硬件和軟件兩部分組成,其中軟件用于控制硬件部分的微控制器、微處理器或數字信號處理器內核,以及外部設備和接口。系統級芯片的設計流程主要是其硬件和軟件的協同設計。

由于系統級芯片的集成度越來越高,設計工程師必須盡可能采取可復用的設計思路。大部分現今SoC都使用預定義的IP核(包括軟核、硬核和固核),以可復用設計的方式來完成快速設計。在軟件開發方面,協議棧是一個重要的概念,它用來驅動USB等行業標準接口。在硬件設計方面,設計人員通常使用EDA工具將已經設計好(或者購買)的IP核連接在一起,在一個集成開發環境(IDE)下集成各種子功能模塊。

下圖不是系統級芯片的設計流程示意圖。

芯片設計在被送到晶圓廠進行流片生產之前,設計人員會采取不同方式對其邏輯功能進行驗證。仿真與驗證是SoC設計流程中最復雜,最耗時的環節,約占整個芯片開發周期的50%~80% ,采用先進的設計與仿真驗證方法已成為SoC設計成功的關鍵。

四、NoC架構

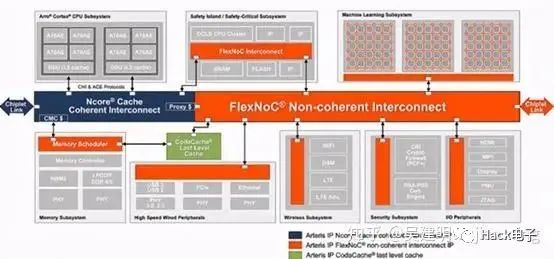

Noc的發展是以SoC為基礎。SoC通常是指在單一芯片上實現的數字計算機系統,通過總線完成其中各模塊之間的交互,但隨著半導體工藝和需求的快速發展,總線的寬度已經成為SoC發展的瓶頸,大大限制了SoC內部通信的速度。90年代NoC技術的提出也是因為借鑒了并行計算機的互聯網絡和以太網絡的分層思想,二者的相同點有:支持包交換、路由協議、任務調度、可擴展等。NoC更關注交換電路和緩存器的面積占用,在設計時主要考量的方面也是這些。

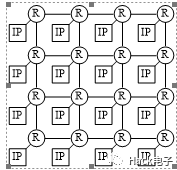

NoC將宏觀網絡的通訊措施應用于芯片上,每個核當做一個獨立的單元,IP核經過網絡接口與特定的路由器相連。將IP核之間的通信轉換為路由器與路由器的通信。通常情況下的NoC架構如下圖所示:

R為路由節點,IP為計算節點。

傳統的NoC架構主要由路由器節點、IP核、資源網絡接口、通道組成。

1、資源節點:主要包含計算節點和存儲節點。計算節點包含處理器即IP核(CPU、DSP等),存儲節點包含ROM、RAM、DRAM、SDRAM等

2、通信節點:即路由節點或路由器,主要負責完成IP核之間的數據通信任務。NoC中資源節點產生一個數據包后,會通過特定的接口發送到源路由器中,源路由器會讀取數據包的頭微片中的地址信息,通過特定的路由算法計算出最佳路由路徑,從而樹立可靠的傳輸到目的節點,最終由目的IP核接收此信息。

3、資源網絡接口:其功能就是作為通信節點與功能節點之間的接口。主要功能有完成數據包的封裝與解封裝,在源節點的資源網絡接口中將原地址信息以及目的地址信息等封裝到數據包的頭微片中;在目的節點的資源網絡接口中將原地址信息以及目的地址信息等刪除。

4、通道:實質為雙向金屬鏈路,用以保證節點間的數據傳輸。分為內部通道和外部通道,內部通道為資源節點和通信節點之間的金屬鏈路,外部通道指通信節點之間的金屬鏈路。

五.NOC架構優勢

1、良好的可擴展能力。一方面,相比于SoC架構,不在受限于總線架構,可以擴展任意數量的計算節點。另一方面,需要對系統功能進行擴展時,只需要將設計好的功能模塊通過資源網絡接口植入網絡,無需重新設計網絡整體架構。

2、較高的通信效率。一方面NoC將IP核之間的數據傳輸演變成為路由器之間的數據轉發,IP核節約了一部分的計算資源。另一方面避免了總線架構同一時刻只能有一對通信節點進行通信的問題,可以實現同一時刻多對節點通信。

3、功耗。NoC中采用全局異步局部同步的時鐘機制,其功耗開銷遠低于SoC。NoC中局部模塊運用同步時鐘域,而全局上采用異步時鐘,降低了由于全局時鐘同步所帶來的動態開銷,同時,NoC中的時鐘樹設計復雜度也低于SoC。

4、數據傳輸可靠性。隨著集成電路特征尺寸的不斷減小,電路規模的不斷增大,互連線的寬度和間距也在不斷地減小,線間耦合電容相應增大,長的全局并行總線會引起較大的串擾噪聲,從而影響信號的完整性以及信號傳輸的正確性。同時,互連線上的延遲將成為影響信號延遲的主要因素,總線結構全局互連線上的延遲將大于一個時鐘周期,從而使得時鐘的偏移很難管理。

六.NoC 和 SoC 的區別

SoC:System on Chip,中文稱為片上系統,主要是針對 ASIC 或者 chip 來講的。在 ASIC 設計的早期,由于制造工藝和性能等的約束,大部分芯片都單純地實現某個特定功能,如處理器內核、總線、內存控制器、藍牙等都由各自獨立的芯片分別實現,處理器之間的通信也以多顆芯片互連的方式實現。

隨著制造工藝的提升,以及設計能力的增強,單顆 ASIC 的功能越來越全面和強大,在一顆芯片內完全可以實現諸如處理器內核、總線、內存控制器、藍牙等所有的功能。同時,ASIC 規模增大導致設計愈來愈復雜,因此,以 IP 核互連為核心的設計方法學應用而生。

這樣,就出現了在一顆芯片里集成了大量的處理器內核、總線、控制器等 IP,而處理器內核數量也由曾經的單核增大到多核、眾核。在這種情況下,設計方法學完全不同于以往 ASIC 的設計方法學,因此,誕生了 SoC 的概念,以和 ASIC 進行區別。不嚴格地說,一顆 SoC 可以實現以前多顆 ASIC 構成的系統。

NoC:Network on Chip,中文稱之為片上網絡。隨著 SoC 技術的發展,芯片內部的 IP 核越來越多,有可能在一顆芯片中集成了數以百記的處理器內核(包括同構處理器內核和異構處理器內核)、數以千計控制器 IP 核等等,那么這種情況下 IP 核之間的互聯就成為 SoC 性能一個重要組成部分。

而 NoC 技術的誕生就是為了能夠讓 IP 核之間的通信能夠實現高效、高吞吐量、低功耗的目的。因此 NoC 技術主要研究對象就是各種互連方法、互連結構,以及 IP 核互聯網絡中路由算法。NoC 技術目前還處于學術研究階段,大部分學術論文里都是仿真結果,工業界也有應用實例,但是比較少。

-

處理器

+關注

關注

68文章

19159瀏覽量

229115 -

soc

+關注

關注

38文章

4118瀏覽量

217932 -

總線

+關注

關注

10文章

2866瀏覽量

87984 -

架構

+關注

關注

1文章

509瀏覽量

25447

原文標題:SoC(System on chip)與NoC(network-on-chip)

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SOC(system-on-a-chip) Verficat

System-on-a-Chip Design

A True System-on-Chip solution

基于電路交換的NoC路由器設計與實現

CC2511F16,pdf(Low-Power SoC (System-on-Chip))

CC2431,pdf(System-on-Chip for

基于FPGA的NoC驗證平臺的構建

CC253x System-on-Chip Solution for 2.4-GHz

片上網絡概述與FPGA研究(連載1)

走近SoC 預告篇

傳智驛芯聯手Arteris,利用創新NoC技術駕馭復雜SoC設計

SoC(System on chip)與NoC(network-on-chip)

SoC(System on chip)與NoC(network-on-chip)

評論