在電路設計過程中,應用工程師往往會忽略印刷電路板 (PCB)的布局 。一個常見的問題是電路原理圖是正確的,但它不起作用,或者只能在低性能下運行。我將向您展示如何正確布置運算放大器的電路板以確保其功能、性能和穩健性。

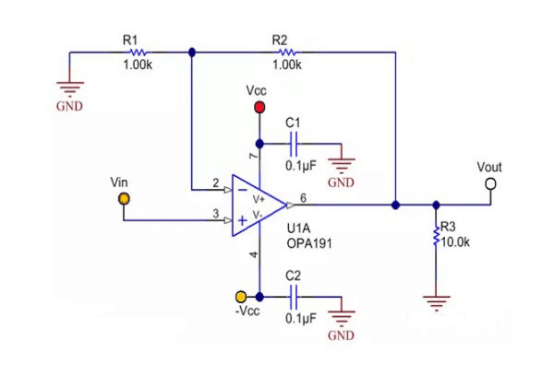

最近,我與一名實習生一起研究了增益為2V/V、負載為10kΩ、電源電壓為+/-15V的同相配置OPA191運算放大器。圖1顯示了設計的原理圖。

圖1:具有同相配置的OPA191原理圖OPA191原理圖

我讓實習生為設計做布板,同時給了他關于PCB布局的一般指導(例如:盡量減少電路板的走線路徑,盡量保持元件排列緊密,以減少電路板占用空間) )空間),然后讓他自己設計。設計過程有多難?其實就是幾個電阻電容而已,不是嗎?圖2顯示了他最初嘗試設計的布局。紅線是到板子頂部的路徑,藍線是底部路徑。

圖 2:第一次布局嘗試

看到他的第一次布局嘗試,我意識到電路板布局并不像我想象的那么直觀;我至少應該給他做一些更詳細的指導。他在設計上完全遵循了我的建議:縮短布線路徑并將零件緊密地放在一起。但是,為了降低電路板的寄生阻抗并優化其性能,這種布局仍有很大的改進空間。

下一步是改進布局。我們所做的第一個改進是將電阻器R1和R2移到OPA191的反相引腳(引腳 2);這有助于減少反相引腳的雜散電容。運算放大器的反相引腳是一個高阻抗節點,因此具有高靈敏度。較長的走線路徑可用作將高頻噪聲耦合到信號鏈中的導線。反相引腳上的PCB電容會導致穩定性問題。因此,反相引腳上的觸點應盡可能小。

將R1和R2移至引腳2允許負載電阻器R3旋轉180度,從而使去耦電容器C1更靠近 OPA191的正電源引腳(引腳 7)。去耦電容盡可能靠近電源引腳非常重要。如果去耦電容和電源引腳之間的走線路徑很長,電源引腳的電感會增加,從而降低性能。

圖 3:改進布局各部分的位置

將零件移動到新位置后,您仍然可以進行一些其他改進。您可以加寬走線路徑以降低電感,這相當于走線路徑所連接的焊盤的尺寸。還可以對電路板的頂部和底部接地層進行灌注,從而為返回電流創建可靠的低阻抗路徑。圖4顯示了我們的最終布局。

圖4:最終布局

下次布局印刷電路板時,建議您遵循以下布局約定:

- 盡量減少反相引腳的連接。

- 將去耦電容盡可能靠近電源引腳放置。

- 如果使用多個去耦電容,請將最小的去耦電容放置在最靠近電源引腳的位置。

- 不要在去耦電容和電源引腳之間放置過孔。

- 盡可能擴展路由路徑。

在上文中,我們談到了儀表放大器(運放)PCB 的正確布局方式,并提供了一系列良好的布局實踐以供參考。接下來,我們將探討布置儀表放大器 (INA) 時的常見錯誤,然后展示如何正確布置INA PCB。

INA 用于需要放大差分電壓的應用,例如在高端電流檢測應用中測量分流電阻器兩端的電壓。圖5顯示了典型的單電源高側電流檢測電路的原理圖。

圖5:高端電流檢測原理圖

圖5通過RSHUNT測量差分電壓,R1、R2、C1、C2和C3用于提供共模和差模濾波,R3和C4為U1 INA提供輸出濾波,U2用于緩沖INA參考引腳. R4和C5用于形成一個低通濾波器,大限度地減少由運算放大器引入到INA參考引腳的噪聲。

雖然圖5中的原理圖布局看起來很直觀,但在PCB布局中很容易出錯,導致電路性能降低。圖6顯示了工作人員在檢查 INA 布局時常見的三個錯誤。

圖 6:INA通用PCB布局

從上圖可以看出,第一個誤差是通過電阻測量差分電壓Rshunt。可以看出Rshunt to R2線較短,因此其電阻小于Rshunt to R1線電阻。線路阻抗的這種差異可能會將輸入偏置電流引入 INA,從而在U1輸入側產生差分電壓。由于INA的任務是放大差分電壓,輸入側的不平衡線路可能會導致錯誤。因此,需要保證INA輸入線是平衡的,并且盡可能短。

第二個誤差與INA增益設置電阻Rgain有關。U1引腳到Rgain焊盤的長度比實際需要的長度要長,因此會產生額外的電阻和電容。由于增益取決于INA增益設置引腳、引腳1和引腳8之間的電阻,因此額外的電阻可能會帶來錯誤的目標增益。由于INA的增益設置引腳連接到INA中的反饋部分,額外的電容可能會導致穩定性問題。因此,確保連接增益設置電阻的線路盡可能短。

然后,可能需要改進緩沖電路參考引腳的位置。參考引腳緩沖電路遠離參考引腳,這可能會增加參考引腳的電阻,導致噪聲或其他信號耦合到線路中。參考引腳上的額外電阻可能會降低大多數INA提供的高共模抑制比 (CMRR)。因此,參考引腳緩沖電路應盡可能靠近INA參考引腳放置。

圖7顯示了糾正這三種錯誤后的布局。

在圖7中,可以看到R1和R2到分流電阻器的線長相同,并且使用了開爾文連接。INA引腳的增益設置電阻盡可能短,基準緩沖電路盡可能靠近基準引腳。

如果您想在未來為INA布置PCB,請務必遵循以下指南:

1、確保輸入端所有線路完全平衡;

- 減少線路長度并最小化增益設置引腳上的電容;

- 將參考緩沖電路布置在盡可能靠近INA參考引腳的位置;

4、去耦電容盡量靠近電源引腳布置;

- 至少覆蓋一層實心地平面;

6.不要為了電子元件使用絲印而犧牲良好的布局 ;

- 遵循本文第一部分中提到的準則。

-

電路板

+關注

關注

140文章

4911瀏覽量

97456 -

運算放大器

+關注

關注

215文章

4900瀏覽量

172608 -

PCB

+關注

關注

1文章

1777瀏覽量

13204

發布評論請先 登錄

相關推薦

同相放大器和鎖相放大器的區別

差分放大器可以放大什么信號

互阻抗放大器怎么接線

如何設置放大器的型號

運算放大器和儀表放大器的區別

反相放大器與非反相放大器的區別

什么是放大器?

放大器放大倍數的影響因素有哪些?

談談放大器放大的是什么

放大器PCB的接線技巧

放大器PCB的接線技巧

評論