PG066中文文檔簡(jiǎn)介

概述

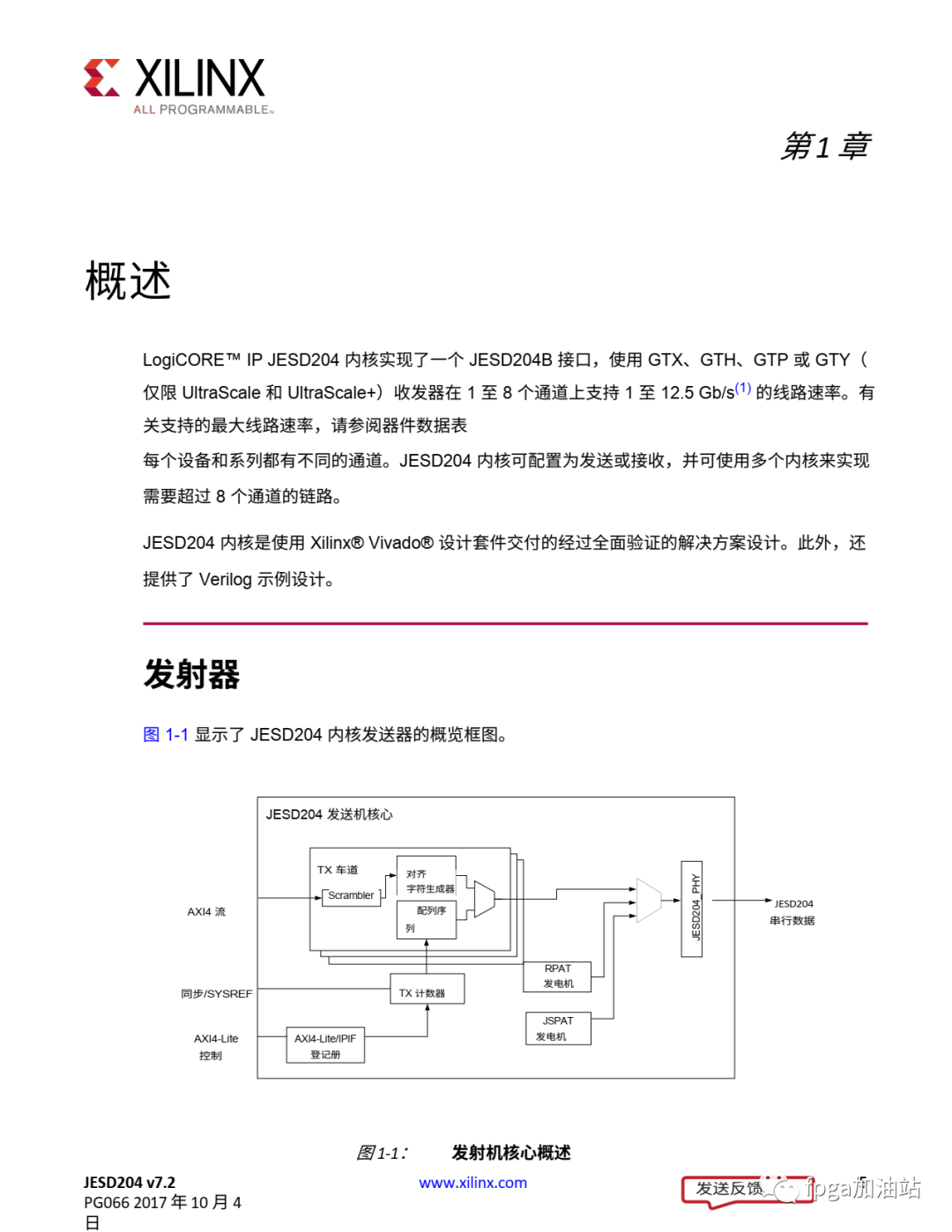

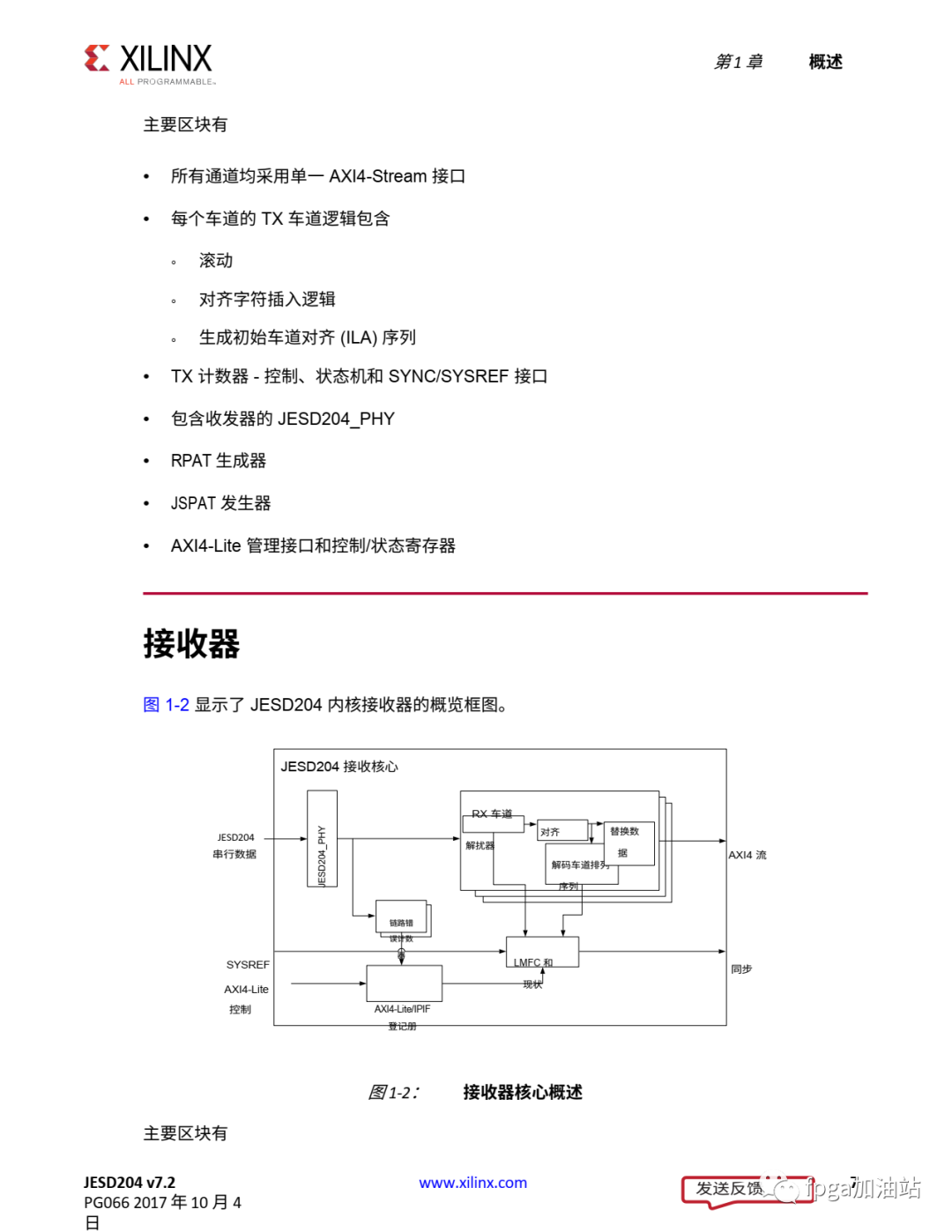

LogiCORE IP JESD204內(nèi)核實(shí)現(xiàn)了一個(gè)JESD204B接口,使用GTX、GTH、GTP或GTY(僅限UltraScale和UltraScale+)收發(fā)器在1至8個(gè)通道上支持1至12.5 Gb/s(1)的線路速率。有關(guān)支持的最大線路速率,請(qǐng)參閱器件數(shù)據(jù)表。 每個(gè)設(shè)備和系列都有不同的通道。JESD204內(nèi)核可配置為發(fā)送或接收,并可使用多個(gè)內(nèi)核來實(shí)現(xiàn)需要超過8個(gè)通道的鏈路。JESD204內(nèi)核是使用Xilinx Vivado設(shè)計(jì)套件交付的經(jīng)過全面驗(yàn)證的解決方案設(shè)計(jì)。此外,還提供了Verilog示例設(shè)計(jì)。

導(dǎo)言

Xilinx LogiCORE IP JESD204內(nèi)核實(shí)現(xiàn)了JESD204B接口,支持1 Gb/s至12.5 Gb/s(1)的線路速率。JESD204內(nèi)核可配置為發(fā)射器或

接收器(2)。

特點(diǎn)

?按照J(rèn)EDEC JESD204B[參考文獻(xiàn)1]設(shè)計(jì)

?每個(gè)內(nèi)核最多支持8條通道,使用多個(gè)內(nèi)核最多支持32條通道

?支持最初的車道排列

?支持?jǐn)_頻

?每個(gè)幀支持1-256個(gè)字節(jié)(3)

?每個(gè)多幀支持1-32個(gè)幀(3)

?支持子類0、1和2

?提供物理層和數(shù)據(jù)鏈路層功能

?AXI4-Lite配置接口[參考文獻(xiàn)2]

?AXI4流數(shù)據(jù)接口[參考文獻(xiàn)3]

?使用JESD204_PHY內(nèi)核,支持TX和RX內(nèi)核之間共享收發(fā)器

PG066中文文檔部分翻譯預(yù)覽

審核編輯:湯梓紅

-

接收器

+關(guān)注

關(guān)注

14文章

2458瀏覽量

71795 -

內(nèi)核

+關(guān)注

關(guān)注

3文章

1362瀏覽量

40228 -

接口

+關(guān)注

關(guān)注

33文章

8496瀏覽量

150834 -

Xilinx

+關(guān)注

關(guān)注

71文章

2163瀏覽量

121002

原文標(biāo)題:中文文檔PG066 | JESD204 v7.2

文章出處:【微信號(hào):fpga加油站,微信公眾號(hào):fpga加油站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

請(qǐng)問AD9683的引腳如何與zynq 7015芯片中的 JESD204 ip核端口對(duì)應(yīng)相連?

在Xilinx FPGA上快速實(shí)現(xiàn)JESD204B

JESD204 v5.2約束使用生成的dcp構(gòu)建邏輯計(jì)時(shí)失敗

無法在Vivado 2013.4中為JESD204B v5.1生成比特流

JESD204不允許生成比特流

JESD204接口簡(jiǎn)介

JESD204標(biāo)準(zhǔn)解析

JESD204評(píng)估許可證問題

為什么JESD204內(nèi)核不使用GTX通道綁定功能來對(duì)齊通道?

JESD204C標(biāo)準(zhǔn)值得注意的新特性

AD9683的引腳如何與zynq 7015芯片中的JESD204 ip核端口對(duì)應(yīng)相連?

ADI公司和Xilinx聯(lián)手實(shí)現(xiàn)JEDEC JESD204B互操作性

采用JESD204標(biāo)準(zhǔn)的高速串行接口的應(yīng)用

JESD204——它是什么?

LogiCORE IP JESD204內(nèi)核概述

LogiCORE IP JESD204內(nèi)核概述

評(píng)論