軟硬件聯(lián)合仿真在確保高效云解決方案的質(zhì)量、降低風(fēng)險(xiǎn)、節(jié)省時(shí)間和成本方面發(fā)揮著關(guān)鍵作用。達(dá)坦科技致力于打通云間壁壘、實(shí)現(xiàn)數(shù)據(jù)高效跨云訪問(wèn),為云上應(yīng)用提供高性能安全存儲(chǔ)支持。在研發(fā)過(guò)程中,軟硬件聯(lián)合仿真顯得尤為重要。這一綜合仿真方法有助于驗(yàn)證系統(tǒng)的一致性,分析和修復(fù)潛在故障,評(píng)估性能并優(yōu)化資源分配。同時(shí),它也用于評(píng)估系統(tǒng)的安全性,確保數(shù)據(jù)在跨云環(huán)境中得到充分的保護(hù)。我們將這一理論與實(shí)踐心得集結(jié)成: 軟硬件協(xié)同仿真系列 。本文是該系列的第一篇文章,著重介紹 原理及概述各部分的主要概念 。

01、為什么要仿真

在芯片設(shè)計(jì)領(lǐng)域,仿真驗(yàn)證是保證設(shè)計(jì)正確的關(guān)鍵步驟。芯片生產(chǎn)成本高昂,因此需要在生產(chǎn)前盡可能對(duì)其進(jìn)行仿真驗(yàn)證以確保其功能和性能符合預(yù)期。另外,在芯片上運(yùn)行的軟件也需要與芯片同步進(jìn)行設(shè)計(jì)和測(cè)試,以縮短整個(gè)系統(tǒng)的生產(chǎn)和迭代周期,因此其載體只能是仿真的芯片。

02、硬件仿真方法

軟件仿真

傳統(tǒng)的仿真方法包括基于軟件的仿真和基于硬件的仿真。基于軟件的仿真利用軟件仿真電路邏輯。例如,QEMU可以模擬真實(shí)CPU的指令執(zhí)行,兩者在執(zhí)行同一條指令后寄存器發(fā)生同樣的變化,運(yùn)行在CPU上的軟件不會(huì)分辨出其差別。這種使用高級(jí)語(yǔ)言編寫(xiě)的模擬硬件行為的軟件一般也被用作硬件實(shí)現(xiàn)的參考模型,兩者可交叉驗(yàn)證。

此外,描述硬件邏輯的RTL(Register Transfer Level)代碼也可以轉(zhuǎn)化高級(jí)軟件語(yǔ)言代碼,并最終生成可執(zhí)行的仿真程序。這賦予了設(shè)計(jì)者在不需要真實(shí)硬件的情況下快速驗(yàn)證硬件邏輯的能力。

硬件仿真

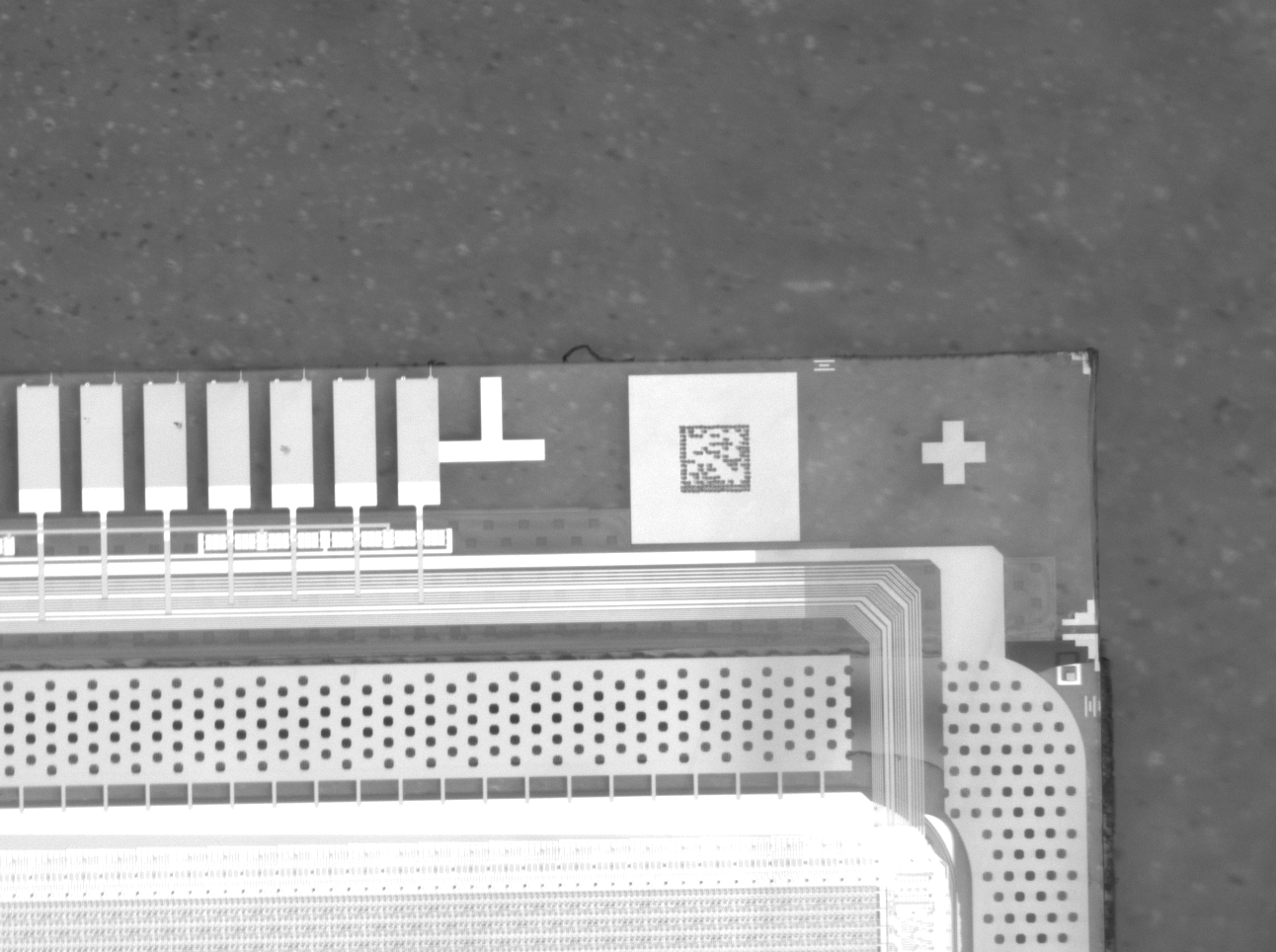

基于硬件的仿真則使用可編程的硬件平臺(tái)來(lái)模擬硬件邏輯。常見(jiàn)的如FPGA(Field Programmable Gate Array)板卡,其內(nèi)部為可編程的硬件結(jié)構(gòu),允許設(shè)計(jì)者將電路邏輯燒錄進(jìn)去,成為一個(gè)接近真實(shí)芯片的硬件原型,可實(shí)時(shí)模擬并觀察硬件邏輯的運(yùn)行狀態(tài)。

相比于基于軟件的仿真,基于硬件的仿真速度更快,可以提供更接近真實(shí)硬件的性能,但在調(diào)試和修改時(shí)的靈活性較低。其能模擬的硬件規(guī)模受自身規(guī)模限制,仿真成本隨規(guī)模上升速度也遠(yuǎn)高于軟件方法。

03、軟硬件協(xié)同仿真

軟硬件協(xié)同仿真指同時(shí)模擬硬件和軟件集成在一起的整個(gè)系統(tǒng)。其中硬件的仿真可能是在硬件仿真器中,或由軟件模擬。軟件模擬又可分為直接由RTL轉(zhuǎn)譯,或是另外開(kāi)發(fā)的事務(wù)級(jí)參考模型,亦或是兩者的結(jié)合。

例如,當(dāng)我們仿真驗(yàn)證一塊采用PCIe接口的網(wǎng)卡時(shí),在使用軟件仿真時(shí),可以將PCIe部分的硬件邏輯由軟件模型代替,將網(wǎng)卡的RTL代碼轉(zhuǎn)譯為可執(zhí)行程序進(jìn)行仿真,再將兩者結(jié)合后接入到運(yùn)行網(wǎng)卡驅(qū)動(dòng)程序的QEMU虛擬機(jī)中,即完成了整個(gè)系統(tǒng)的仿真。

以上例子中,PCIe部分不是我們的驗(yàn)證重點(diǎn),因此用事務(wù)級(jí)軟件模型仿真。由于省略了對(duì)具體電路行為的仿真,提高了仿真抽象水平,軟件模型相較由RTL轉(zhuǎn)譯的仿真程序執(zhí)行速度更快。使用硬件仿真時(shí),PCIe部分邏輯可由硬核實(shí)現(xiàn),網(wǎng)卡邏輯燒錄在可編程門(mén)陣列中,以提高仿真速度,降低仿真器占用。QEMU中的應(yīng)用軟件和驅(qū)動(dòng)程序可不感知以上硬件仿真的具體實(shí)現(xiàn)。

軟硬件協(xié)同仿真試圖結(jié)合軟件仿真和硬件仿真,使開(kāi)發(fā)者可以同時(shí)驗(yàn)證和調(diào)試系統(tǒng)的軟件和硬件部分。對(duì)硬件邏輯實(shí)現(xiàn)復(fù)雜的、非驗(yàn)證重點(diǎn)的部分使用事務(wù)級(jí)模型仿真,對(duì)性能有要求或需要重點(diǎn)驗(yàn)證的部分則采用基于硬件的仿真,亦可結(jié)合對(duì)成本和工期的要求進(jìn)行配置。通過(guò)這種混合仿真的方式,設(shè)計(jì)者可以以較低的成本和較高的性能驗(yàn)證整個(gè)系統(tǒng)。

04、主要組成部分

軟硬件協(xié)同仿真涉及多個(gè)關(guān)鍵組件和工具,其中最核心的有QEMU、SystemC/TLM、RTL Simulation和Bridge。在此簡(jiǎn)要介紹一下組件的基本概念和它們之間的關(guān)系。

QEMU

QEMU是一個(gè)廣泛應(yīng)用的開(kāi)源機(jī)器模擬器和虛擬化工具。QEMU能夠模擬整個(gè)系統(tǒng)級(jí)別的操作,如模擬一臺(tái)計(jì)算機(jī),包括硬件部件操作系統(tǒng)以及驅(qū)動(dòng)等。其可以模擬任意硬件,或?yàn)橛布峁┮粋€(gè)真實(shí)的軟件運(yùn)行環(huán)境。

SystemC/TLM

SystemC是用于系統(tǒng)級(jí)建模的開(kāi)源C++庫(kù),而TLM(Transaction Level Modeling)是一個(gè)在SystemC環(huán)境下描述與仿真硬件行為的模型。相比于傳統(tǒng)的RTL設(shè)計(jì),TLM能夠更高層次地描述硬件行為,從而提供更快的仿真速度。使用SystemC/TLM構(gòu)建的模型通常作為“膠水”連接QEMU和RTL。例如,在上述網(wǎng)卡仿真例子中,PCIe部分由一個(gè)事務(wù)級(jí)的TLM模型描述,兩端分別連接軟件和仿真的硬件。

RTL Simulation

RTL仿真可以基于軟件或硬件進(jìn)行。軟件如Verilator,一個(gè)開(kāi)源的Verilog仿真器,它可以將Verilog代碼轉(zhuǎn)換為C++模型,然后通過(guò)C++進(jìn)行快速仿真。硬件如FPGA,其中包含可編程的硬件邏輯,可用于仿真硬件原型。

Bridge

要將軟件與硬件集成,還需要各類(lèi)橋接器連接軟硬件邏輯。例如TLM到PCIe等各類(lèi)硬件接口到軟件接口互聯(lián)橋。這部分需要根據(jù)具體的軟硬件平臺(tái)開(kāi)發(fā),或使用開(kāi)源項(xiàng)目LibSystemCTLM-SoC提供的常見(jiàn)接口轉(zhuǎn)換橋。

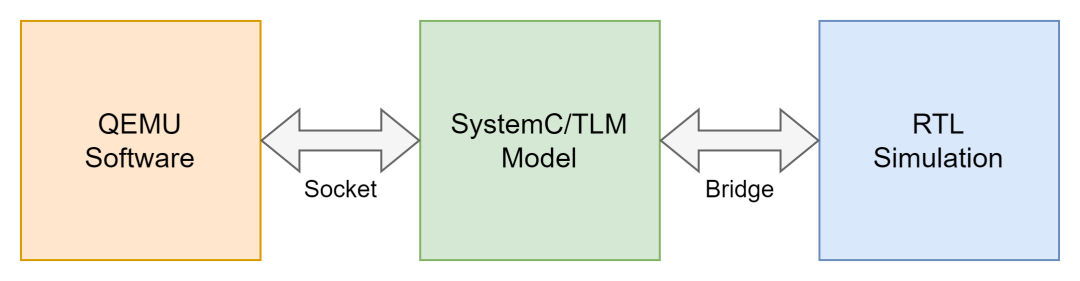

下圖展示了一種組件之間的連接關(guān)系。假設(shè)我們模擬一個(gè)PCIe設(shè)備(如網(wǎng)卡),QEMU模擬了一臺(tái)計(jì)算機(jī),承載操作系統(tǒng)和設(shè)備驅(qū)動(dòng)程序。TLM模型和RTL仿真共同實(shí)現(xiàn)了設(shè)備邏輯,并通過(guò)Socket連接到QEMU中,表現(xiàn)為一個(gè)PCIe設(shè)備。

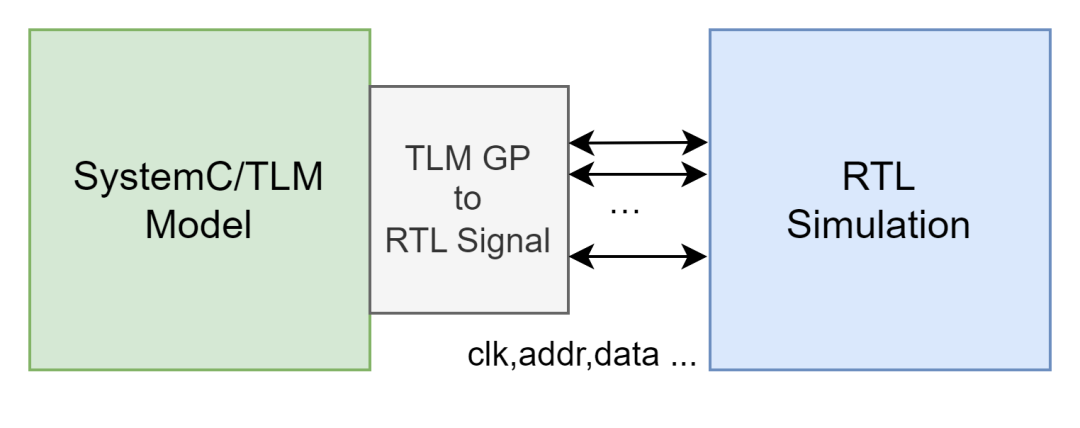

下圖展示了TLM級(jí)仿真和RTL級(jí)仿真的橋接細(xì)節(jié)。其中TLM GP(Generic Payload)指一個(gè)一般的總線讀/寫(xiě)操作。Bridge的作用就是將TLM事務(wù)級(jí)的操作轉(zhuǎn)化為RTL級(jí)的信號(hào)。例如,TLM的一個(gè)讀事務(wù)可能會(huì)被轉(zhuǎn)換為在RTL級(jí)別的一個(gè)地址信號(hào)、一個(gè)讀使能信號(hào)等。由于TLM模型通常是與時(shí)間無(wú)關(guān)的或粗粒度的,所以在轉(zhuǎn)換為RTL信號(hào)時(shí),橋必須考慮時(shí)序問(wèn)題。這可能涉及到模型之間的時(shí)間同步,以確保所有事務(wù)和信號(hào)都在正確的模擬時(shí)間內(nèi)發(fā)生。

05、仿真案例

下面以一個(gè)例子介紹SystemC/TLM軟件模型與仿真的硬件設(shè)備的對(duì)接流程和實(shí)現(xiàn)原理。

在Xilinx的libsystemctlm-soc倉(cāng)庫(kù)中包含一個(gè)AXI4從設(shè)備與SystemC/TLM模型交互的樣例程序(example-rtl-axi4)。其中axifull_dev_s00_AXI.v是由 Xilinx IP Integrator自動(dòng)生成的Verilog模塊,其功能是一塊可通過(guò)AXI4總線讀寫(xiě)的存儲(chǔ)器。axifull_dev.v對(duì)其進(jìn)行了一層封裝,并預(yù)留了用戶(hù)增加額外邏輯的空間。以上即為硬件部分。

在http://example-rtl-axi4.cc中描述了TLM模型與AXI設(shè)備的連接和交互邏輯。主要包括將axifull_dev設(shè)備實(shí)例化為DUT(Device Under Test),并通過(guò)軟件生成的仿真測(cè)試激勵(lì),對(duì)硬件進(jìn)行讀寫(xiě)操作測(cè)試。

如下是http://example-rtl-axi4.cc部分代碼。首先是通過(guò)TrafficDesc transactions定義了一組要在仿真環(huán)境中執(zhí)行的事務(wù),分別是寫(xiě),讀,以及期望讀到的值。TrafficDesc在此用于簡(jiǎn)化生成TLM GP的操作。激勵(lì)生成器 (TLMTrafficGenerator tg) 根據(jù)transactions對(duì)事務(wù)的描述生成TLM GP。再通過(guò)TLM到AXI的橋接器 (tlm2axi_bridge bridge) 被轉(zhuǎn)換為AXI信號(hào),最后由被測(cè)設(shè)備 (Vaxifull_dev dut) 處理。

TrafficDesc transactions(merge({

// 寫(xiě)數(shù)據(jù)到地址8

Write(8, DATA(0x1, 0x2, 0x3, 0x4)),

// 讀回并判斷讀到的是否是預(yù)期數(shù)據(jù)

Read(8, 4),

Expect(DATA(0x1, 0x2, 0x3, 0x4), 4)

}));

SC_MODULE(Top)

{

sc_clock clk;

sc_signal

TLM GP定義了一個(gè)總線讀寫(xiě)事務(wù)的抽象,包括讀寫(xiě)命令、響應(yīng)狀態(tài)、地址和數(shù)據(jù)相關(guān)信息。以下截取了定義的一部分,完整代碼可見(jiàn)tlm_gp.h。當(dāng)然,TLM GP只包含最一般的信息,沒(méi)有攜帶與AXI協(xié)議相關(guān)的一些具體概念。為了建模此類(lèi)與硬件總線協(xié)議相關(guān)的具體行為,庫(kù)中還包含了可選的拓展屬性Generic Attributes,用以更細(xì)致地建模,在此就不展開(kāi)了。

class SC_API tlm_generic_payload {

···

private:

/* --------------------------------------------------------------------- */

/* Generic Payload attributes: */

/* --------------------------------------------------------------------- */

/* - m_command : Type of transaction. Three values supported: */

/* - TLM_WRITE_COMMAND */

/* - TLM_READ_COMMAND */

/* - TLM_IGNORE_COMMAND */

/* - m_address : Transaction base address (byte-addressing). */

/* - m_data : When m_command = TLM_WRITE_COMMAND contains a */

/* pointer to the data to be written in the target.*/

/* When m_command = TLM_READ_COMMAND contains a */

/* pointer where to copy the data read from the */

/* target. */

/* - m_length : Total number of bytes of the transaction. */

/* - m_response_status : This attribute indicates whether an error has */

/* occurred during the transaction. */

sc_dt::uint64 m_address;

tlm_command m_command;

unsigned char* m_data;

unsigned int m_length;

tlm_response_status m_response_status;

···

}

從TLM GP到AXI信號(hào)的轉(zhuǎn)換邏輯在Bridge中完成,具體實(shí)現(xiàn)在文件tlm2axi_bridge.h中。概括其內(nèi)容,就是根據(jù)總線協(xié)議手冊(cè),將TLM GP對(duì)一個(gè)事務(wù)的抽象描述翻譯為一個(gè)時(shí)間序列上硬件信號(hào)線上的高低電平。以寫(xiě)數(shù)據(jù)的實(shí)現(xiàn)為例,如下是截取的一個(gè)代碼片段,描述的內(nèi)容是將wready位置高,等待wvalid變?yōu)楦撸龅絩eset信號(hào)則需要等到其被釋放,然后是向一組wdata信號(hào)線填充數(shù)據(jù)位等等。

void write_data_phase()

{

while (true) {

···

wready.write(true);

wait_abort_on_reset(wvalid);

if (reset_asserted()) {

wait_for_reset_release();

continue;

}

···

}

wt- >FillData(wdata, wstrb);

···

}

在軟件仿真環(huán)境中,如SystemC和Verilator,軟件定義的信號(hào)狀態(tài)會(huì)周期性地更新同步到仿真的硬件描述語(yǔ)言中的信號(hào)線上。由于硬件被仿真器轉(zhuǎn)譯為軟件,因此信號(hào)間的同步實(shí)質(zhì)是軟件變量間的賦值。

在硬件仿真環(huán)境下,軟件定義的信號(hào)到硬件信號(hào)的映射需要更多橋接工作。例如當(dāng)采用PCIe接口的FPGA進(jìn)行仿真時(shí),上述DUT運(yùn)行在FPGA上,TLM模型在CPU中運(yùn)行,PCIe作為通信媒介。TLM模型需要通過(guò)PCIe,間接控制FPGA上的AXI設(shè)備。這中間涉及到對(duì)PCIe設(shè)備的控制,以及PCIe到AXI的映射等橋接工作,libsystemctlm-soc也封裝了此硬件橋,如tlm2axi_hw_bridge。在這些橋接工具庫(kù)的幫助下,開(kāi)發(fā)者可以方便地在純軟件和軟硬件混合的仿真平臺(tái)之間切換,而不用對(duì)程序做大幅修改。

以上例子只是簡(jiǎn)單地展示了SystemC/TLM部分與硬件的連接方法,并使用兩個(gè)簡(jiǎn)單的事務(wù)對(duì)硬件進(jìn)行了測(cè)試。在此基礎(chǔ)上,我們可以使用軟件高級(jí)語(yǔ)言如C++模擬任意硬件行為,構(gòu)建高抽象水平的模型,并通過(guò)SystemC提供的工具庫(kù)賦予模型與硬件邏輯交互的能力。軟件模型又可以通過(guò)Socket接入到QEMU,由QEMU中的應(yīng)用軟件生成測(cè)試激勵(lì),以完成從應(yīng)用、驅(qū)動(dòng)、到設(shè)備的整個(gè)軟硬件系統(tǒng)的集成測(cè)試。

06、總結(jié)

本文介紹了軟硬件協(xié)同仿真的原因,概念和方法。通過(guò)結(jié)合軟硬件仿真,TLM級(jí)仿真和RTL級(jí)仿真的優(yōu)勢(shì),降低仿真成本,提高仿真速度。使得開(kāi)發(fā)者可以在流片前驗(yàn)證從硬件到軟件的整個(gè)系統(tǒng),確保軟硬件設(shè)計(jì)的正確性和性能滿(mǎn)足預(yù)期要求,縮短迭代周期。

軟硬件協(xié)同仿真的技術(shù)鏈條長(zhǎng),涉及多個(gè)技術(shù)組件和工具,混合了不同抽象級(jí)別的軟硬件系統(tǒng)。本文受篇幅所限,只概述了其主要組成部分,后續(xù)在“軟硬件協(xié)同仿真”系列里將結(jié)合實(shí)例,為大家分享鏈路每個(gè)環(huán)節(jié)背后的實(shí)現(xiàn)原理。

-

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1001瀏覽量

54811 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59697 -

TLM

+關(guān)注

關(guān)注

1文章

32瀏覽量

24733 -

虛擬機(jī)

+關(guān)注

關(guān)注

1文章

908瀏覽量

28086 -

FPGA芯片

+關(guān)注

關(guān)注

3文章

246瀏覽量

39780

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

物聯(lián)網(wǎng)泵房的功能和組成部分

嵌入式系統(tǒng)的硬件組成部分

BUCK開(kāi)關(guān)電源的主要組成部分

嵌入式系統(tǒng)軟硬件基礎(chǔ)知識(shí)大全

東軟睿馳與瑞薩電子達(dá)成合作伙伴關(guān)系,強(qiáng)化汽車(chē)軟硬件協(xié)同創(chuàng)新

電池管理系統(tǒng)(BMS)軟硬件介紹

什么是EMSS?它包括哪些組成部分?

【小門(mén)衛(wèi)】 小門(mén)衛(wèi)、守好門(mén); 小門(mén)衛(wèi)是一家以AI技術(shù)驅(qū)動(dòng),集軟硬件一體化,為生產(chǎn)生活提供安防場(chǎng)景應(yīng)用解決方案。

【小門(mén)衛(wèi)】 小門(mén)衛(wèi)、守好門(mén); 小門(mén)衛(wèi)是一家以AI技術(shù)驅(qū)動(dòng),集軟硬件一體化,為生產(chǎn)生活提供安防場(chǎng)景應(yīng)用解決方案。

KubeCASH:基于軟硬件融合的容器管理平臺(tái)

軟硬件協(xié)同仿真原理及主要組成部分概述

軟硬件協(xié)同仿真原理及主要組成部分概述

評(píng)論