前言

前面的文章詳細介紹了Autosar架構圖下的SPI模塊,但是沒有介紹SPI通信總線,本文轉載一篇個人認為寫的比較好的SPI通信協議介紹的文章,供大家參考。

參考文章:

AUTOSAR-MCAL--SPI模塊詳解(一)

AUTOSAR-MCAL--SPI模塊詳解(二)

AUTOSAR-MCAL--SPI模塊詳解(三)

注:本文轉載自CSDN,由硬件十萬個為什么公眾號整理。

正文

1、 SPI簡介

SPI,是英語Serial Peripheral interface的縮寫,顧名思義就是串行外圍設備接口。是Motorola首先在其MC68HCXX系列處理器上定義的。SPI接口主要應用在 EEPROM,FLASH,實時時鐘,AD轉換器,還有數字信號處理器和數字信號解碼器之間。SPI,是一種高速的,全雙工,同步的通信總線,并且在芯片的管腳上只占用四根線,節約了芯片的管腳,同時為PCB的布局上節省空間,提供方便,正是出于這種簡單易用的特性,現在越來越多的芯片集成了這種通信協議。

2、 SPI特點

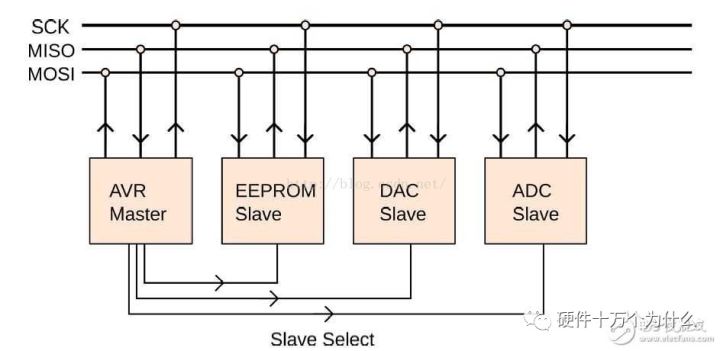

2.1采用主-從模式(Master-Slave) 的控制方式

SPI 規定了兩個 SPI 設備之間通信必須由主設備 (Master) 來控制次設備 (Slave). 一個 Master 設備可以通過提供 Clock 以及對 Slave 設備進行片選 (Slave Select) 來控制多個 Slave 設備, SPI 協議還規定 Slave 設備的 Clock 由 Master 設備通過 SCK 管腳提供給 Slave 設備, Slave 設備本身不能產生或控制 Clock, 沒有 Clock 則 Slave 設備不能正常工作。

2.2采用同步方式(Synchronous)傳輸數據

Master 設備會根據將要交換的數據來產生相應的時鐘脈沖(Clock Pulse), 時鐘脈沖組成了時鐘信號(Clock Signal) , 時鐘信號通過時鐘極性 (CPOL) 和 時鐘相位 (CPHA) 控制著兩個 SPI 設備間何時數據交換以及何時對接收到的數據進行采樣, 來保證數據在兩個設備之間是同步傳輸的。

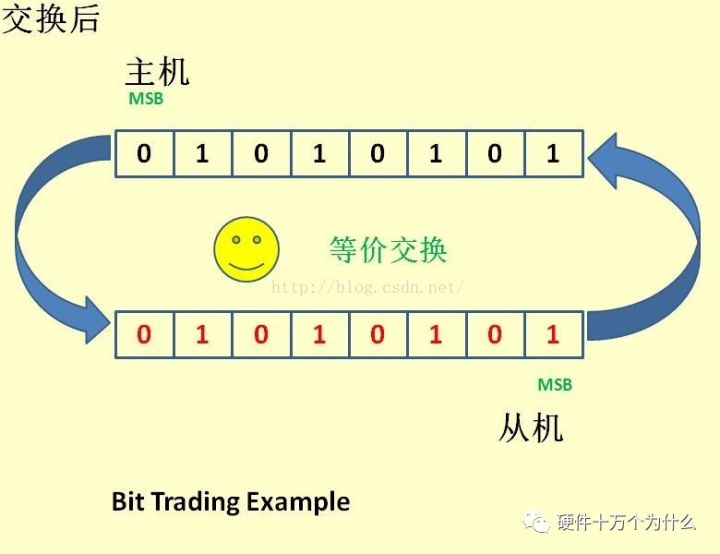

2.3數據交換(Data Exchanges)

SPI 設備間的數據傳輸之所以又被稱為數據交換, 是因為 SPI 協議規定一個 SPI 設備不能在數據通信過程中僅僅只充當一個 "發送者(Transmitter)" 或者 "接收者(Receiver)". 在每個 Clock 周期內, SPI 設備都會發送并接收一個 bit 大小的數據, 相當于該設備有一個 bit 大小的數據被交換了. 一個 Slave 設備要想能夠接收到 Master 發過來的控制信號, 必須在此之前能夠被 Master 設備進行訪問 (Access). 所以, Master 設備必須首先通過 SS/CS pin 對 Slave 設備進行片選, 把想要訪問的 Slave 設備選上. 在數據傳輸的過程中, 每次接收到的數據必須在下一次數據傳輸之前被采樣. 如果之前接收到的數據沒有被讀取, 那么這些已經接收完成的數據將有可能會被丟棄, 導致 SPI 物理模塊最終失效. 因此, 在程序中一般都會在 SPI 傳輸完數據后, 去讀取 SPI 設備里的數據, 即使這些數據(Dummy Data)在我們的程序里是無用的。

2.4 SPI有四種傳輸模式

上升沿、下降沿、前沿、后沿觸發。當然也有MSB和LSB傳輸方式。

2.5 SPI只有主模式和從模式之分。

沒有讀和寫的說法,因為實質上每次SPI是主從設備在交換數據。也就是說,你發一個數據必然會收到一個數據;你要收一個數據必須也要先發一個數據。

3、 工作機制

3.1概述

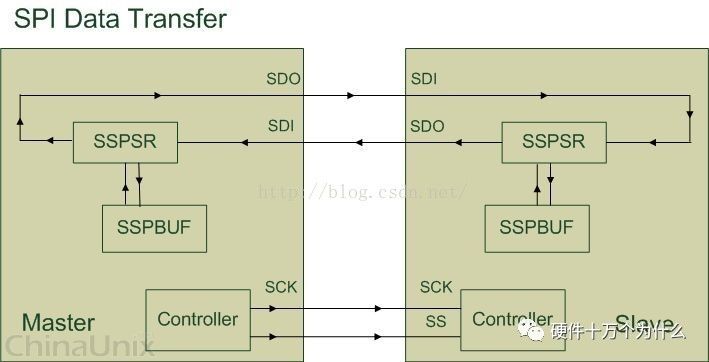

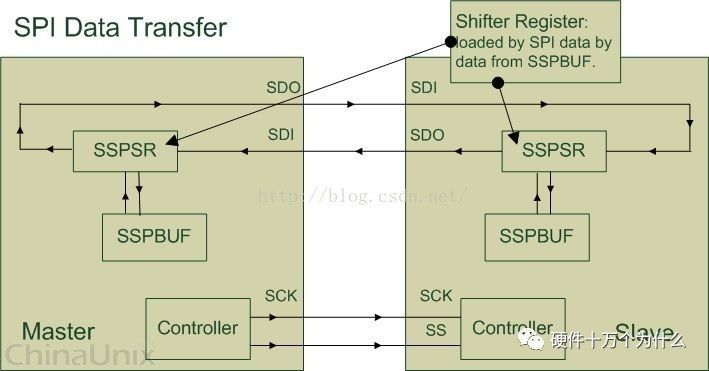

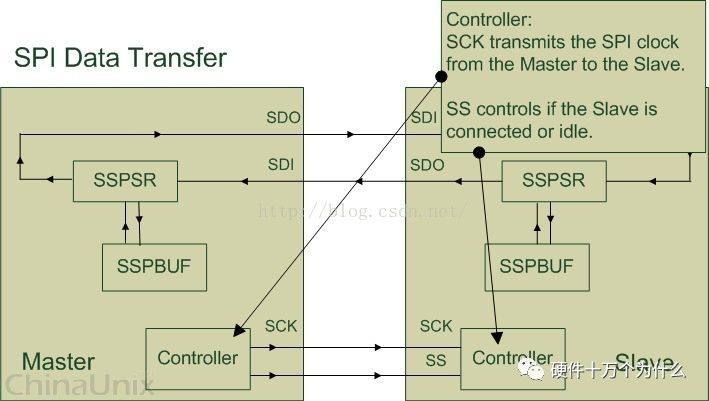

上圖只是對 SPI 設備間通信的一個簡單的描述, 下面就來解釋一下圖中所示的幾個組件(Module):

SSPBUF,Synchronous Serial Port Buffer, 泛指 SPI 設備里面的內部緩沖區, 一般在物理上是以 FIFO 的形式, 保存傳輸過程中的臨時數據;

SSPSR, Synchronous Serial Port Register, 泛指 SPI 設備里面的移位寄存器(Shift Regitser), 它的作用是根據設置好的數據位寬(bit-width) 把數據移入或者移出 SSPBUF;

Controller, 泛指 SPI 設備里面的控制寄存器, 可以通過配置它們來設置 SPI 總線的傳輸模式。

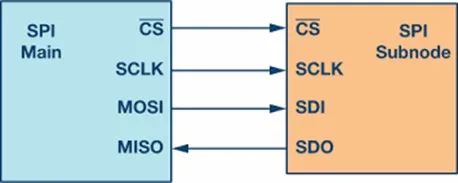

通常情況下, 我們只需要對上圖所描述的四個管腳(pin) 進行編程即可控制整個 SPI 設備之間的數據通信:

SCK, Serial Clock, 主要的作用是 Master 設備往 Slave 設備傳輸時鐘信號, 控制數據交換的時機以及速率;

SS/CS, Slave Select/Chip Select, 用于 Master 設備片選 Slave 設備, 使被選中的 Slave 設備能夠被 Master 設備所訪問;

SDO/MOSI, Serial Data Output/Master Out Slave In, 在 Master 上面也被稱為 Tx-Channel, 作為數據的出口, 主要用于 SPI 設備發送數據;

SDI/MISO, Serial Data Input/Master In Slave Out, 在 Master 上面也被稱為 Rx-Channel, 作為數據的入口, 主要用于SPI 設備接收數據;

SPI 設備在進行通信的過程中, Master 設備和 Slave 設備之間會產生一個數據鏈路回環(Data Loop), 就像上圖所畫的那樣, 通過 SDO 和 SDI 管腳, SSPSR 控制數據移入移出 SSPBUF, Controller 確定 SPI 總線的通信模式, SCK 傳輸時鐘信號。

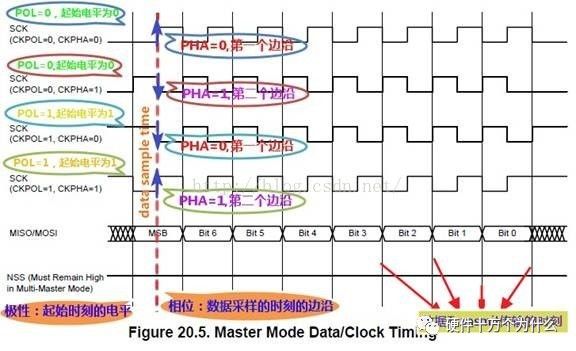

3.2 Timing

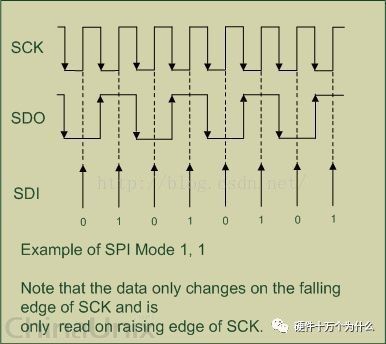

上圖通過 Master 設備與 Slave 設備之間交換1 Byte 數據來說明 SPI 協議的工作機制。

首先, 在這里解釋一下相位和極性的概念

3.2.1 SPI相關的縮寫或說法

SPI的極性Polarity和相位Phase,最常見的寫法是CPOL和CPHA,不過也有一些其他寫法,簡單總結如下:

(1) CKPOL (Clock Polarity) = CPOL = POL = Polarity = (時鐘)極性

(2) CKPHA (Clock Phase) = CPHA = PHA = Phase = (時鐘)相位

(3) SCK=SCLK=SPI的時鐘

(4) Edge=邊沿,即時鐘電平變化的時刻,即上升沿(rising edge)或者下降沿(falling edge)

對于一個時鐘周期內,有兩個edge,分別稱為:

Leading edge=前一個邊沿=第一個邊沿,對于開始電壓是1,那么就是1變成0的時候,對于開始電壓是0,那么就是0變成1的時候;

Trailing edge=后一個邊沿=第二個邊沿,對于開始電壓是1,那么就是0變成1的時候(即在第一次1變成0之后,才可能有后面的0變成1),對于開始電壓是0,那么就是1變成0的時候;

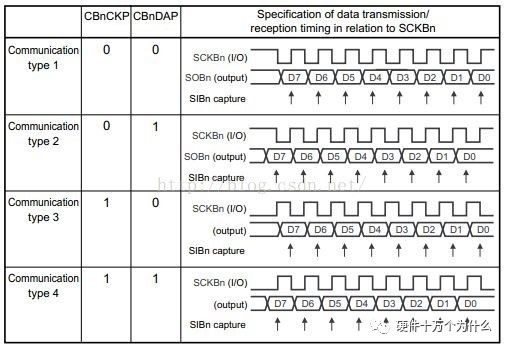

3.2.2 SPI的相位和極性

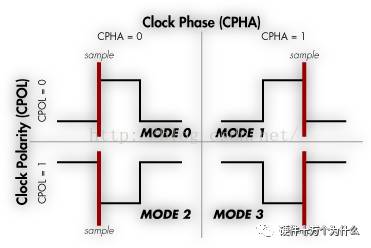

CPOL和CPHA,分別都可以是0或時1,對應的四種組合就是:

Mode 0 CPOL=0, CPHA=0

Mode 1 CPOL=0, CPHA=1

Mode 2 CPOL=1, CPHA=0

Mode 3 CPOL=1, CPHA=1

3.2.3 CPOL極性

先說什么是SCLK時鐘的空閑時刻,其就是當SCLK在數發送8個bit比特數據之前和之后的狀態,于此對應的,SCLK在發送數據的時候,就是正常的工作的時候,有效active的時刻了。

先說英文,其精簡解釋為:Clock Polarity = IDLE state of SCK。

再用中文詳解:

SPI的CPOL,表示當SCLK空閑idle的時候,其電平的值是低電平0還是高電平1:

CPOL=0,時鐘空閑idle時候的電平是低電平,所以當SCLK有效的時候,就是高電平,就是所謂的active-high;

CPOL=1,時鐘空閑idle時候的電平是高電平,所以當SCLK有效的時候,就是低電平,就是所謂的active-low;

3.2.4 CPHA相位

首先說明一點,capture strobe = latch = read = sample,都是表示數據采樣,數據有效的時刻。相位,對應著數據采樣是在第幾個邊沿(edge),是第一個邊沿還是第二個邊沿,0對應著第一個邊沿,1對應著第二個邊沿。

對于:

CPHA=0,表示第一個邊沿:

對于CPOL=0,idle時候的是低電平,第一個邊沿就是從低變到高,所以是上升沿;

對于CPOL=1,idle時候的是高電平,第一個邊沿就是從高變到低,所以是下降沿;

CPHA=1,表示第二個邊沿:

對于CPOL=0,idle時候的是低電平,第二個邊沿就是從高變到低,所以是下降沿;

對于CPOL=1,idle時候的是高電平,第一個邊沿就是從低變到高,所以是上升沿;

還是上圖大家更容易看懂

3.2.5 軟件中如何設置SPI的極性和相位

SPI分主設備和從設備,兩者通過SPI協議通訊。

而設置SPI的模式,是從設備的模式,決定了主設備的模式。

所以要先去搞懂從設備的SPI是何種模式,然后再將主設備的SPI的模式,設置和從設備相同的模式,即可正常通訊。

對于從設備的SPI是什么模式,有兩種:

3.2.5.1固定的,有SPI從設備硬件決定的

SPI從設備,具體是什么模式,相關的datasheet中會有描述,需要自己去datasheet中找到相關的描述,即:

關于SPI從設備,在空閑的時候,是高電平還是低電平,即決定了CPOL是0還是1;

然后再找到關于設備是在上升沿還是下降沿去采樣數據,這樣就是,在定了CPOL的值的前提下,對應著可以推算出CPHA是0還是1了。

3.2.5.2 可配置的,由軟件自己設定

從設備也是一個SPI控制器,4種模式都支持,此時只要自己設置為某種模式即可。

然后知道了從設備的模式后,再去將SPI主設備的模式,設置為和從設備模式一樣,即可。

對于如何配置SPI的CPOL和CPHA的話,不多細說,多數都是直接去寫對應的SPI控制器中對應寄存器中的CPOL和CPHA那兩位,寫0或寫1即可。

3.3 SSPSR

SSPSR 是 SPI 設備內部的移位寄存器(Shift Register). 它的主要作用是根據 SPI 時鐘信號狀態, 往 SSPBUF 里移入或者移出數據, 每次移動的數據大小由 Bus-Width 以及 Channel-Width 所決定。

Bus-Width 的作用是指定地址總線到 Master 設備之間數據傳輸的單位。

例如, 我們想要往 Master 設備里面的 SSPBUF 寫入 16 Byte 大小的數據: 首先, 給 Master 設備的配置寄存器設置 Bus-Width 為 Byte; 然后往 Master 設備的 Tx-Data 移位寄存器在地址總線的入口寫入數據, 每次寫入 1 Byte 大小的數據(使用 writeb 函數); 寫完 1 Byte 數據之后, Master 設備里面的 Tx-Data 移位寄存器會自動把從地址總線傳來的1 Byte 數據移入 SSPBUF 里; 上述動作一共需要重復執行 16 次.

Channel-Width 的作用是指定 Master 設備與 Slave 設備之間數據傳輸的單位. 與 Bus-Width 相似, Master 設備內部的移位寄存器會依據 Channel-Width 自動地把數據從 Master-SSPBUF 里通過 Master-SDO 管腳搬運到 Slave 設備里的 Slave-SDI 引腳, Slave-SSPSR 再把每次接收的數據移入 Slave-SSPBUF里.通常情況下, Bus-Width 總是會大于或等于 Channel-Width, 這樣能保證不會出現因 Master 與 Slave 之間數據交換的頻率比地址總線與 Master 之間的數據交換頻率要快, 導致 SSPBUF 里面存放的數據為無效數據這樣的情況。

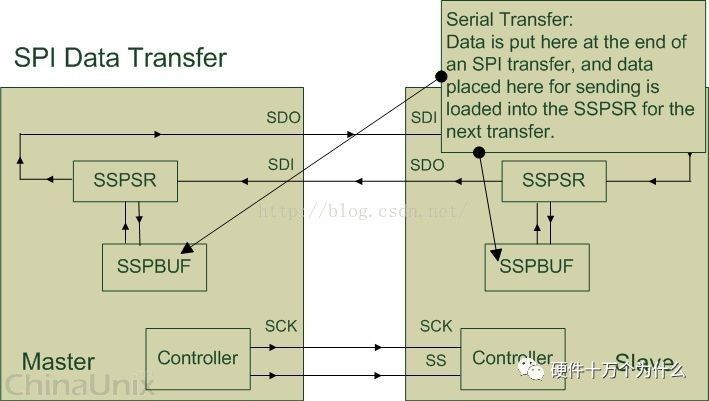

3.4 SSPBUF

我們知道, 在每個時鐘周期內, Master 與 Slave 之間交換的數據其實都是 SPI 內部移位寄存器從 SSPBUF 里面拷貝的. 我們可以通過往 SSPBUF 對應的寄存器 (Tx-Data / Rx-Data register) 里讀寫數據, 間接地操控 SPI 設備內部的 SSPBUF.

例如, 在發送數據之前, 我們應該先往 Master 的 Tx-Data 寄存器寫入將要發送出去的數據, 這些數據會被 Master-SSPSR 移位寄存器根據 Bus-Width 自動移入 Master-SSPBUF 里, 然后這些數據又會被 Master-SSPSR 根據 Channel-Width 從 Master-SSPBUF 中移出, 通過 Master-SDO 管腳傳給 Slave-SDI 管腳, Slave-SSPSR 則把從 Slave-SDI 接收到的數據移入 Slave-SSPBUF 里. 與此同時, Slave-SSPBUF 里面的數據根據每次接收數據的大小(Channel-Width), 通過 Slave-SDO 發往 Master-SDI, Master-SSPSR 再把從 Master-SDI 接收的數據移入 Master-SSPBUF.在單次數據傳輸完成之后, 用戶程序可以通過從 Master 設備的 Rx-Data 寄存器讀取 Master 設備數據交換得到的數據。

3.5 Controller

Master 設備里面的 Controller 主要通過時鐘信號(Clock Signal)以及片選信號(Slave Select Signal)來控制 Slave 設備. Slave 設備會一直等待, 直到接收到 Master 設備發過來的片選信號, 然后根據時鐘信號來工作。

Master 設備的片選操作必須由程序所實現. 例如: 由程序把 SS/CS 管腳的時鐘信號拉低電平, 完成 SPI 設備數據通信的前期工作; 當程序想讓 SPI 設備結束數據通信時, 再把 SS/CS 管腳上的時鐘信號拉高電平。

4. SPI舉例

上面說了那么多,在這里我來舉一個例子幫助大家理解。

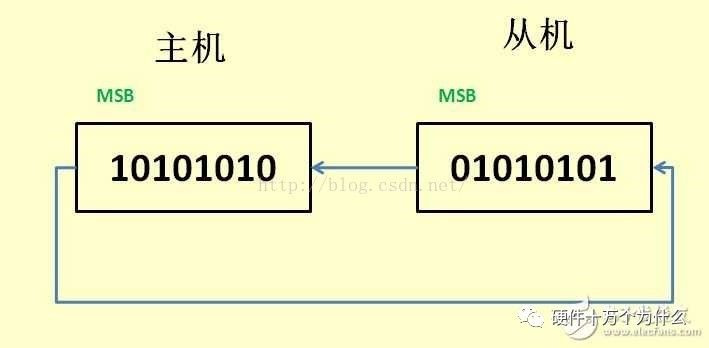

SPI是一個環形總線結構,由ss(cs)、sck、sdi、sdo構成,其時序其實很簡單,主要是在sck的控制下,兩個雙向移位寄存器進行數據交換。

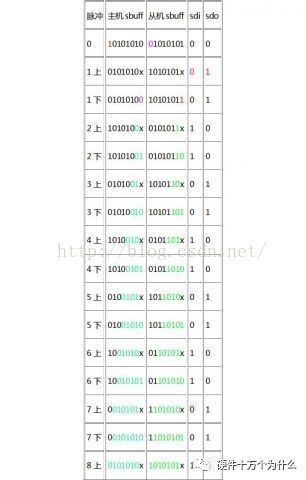

假設下面的8位寄存器裝的是待發送的數據10101010,上升沿發送、下降沿接收、高位先發送。

那么第一個上升沿來的時候 數據將會是sdo=1;寄存器=0101010x。下降沿到來的時候,sdi上的電平將所存到寄存器中去,那么這時寄存器=0101010sdi,這樣在 8個時鐘脈沖以后,兩個寄存器的內容互相交換一次。這樣就完成里一個spi時序。

舉例:

假設主機和從機初始化就緒:并且主機的sbuff=0xaa,從機的sbuff=0x55,下面將分步對spi的8個時鐘周期的數據情況演示一遍:假設上升沿發送數據。

這樣就完成了兩個寄存器8位的交換,上面的上表示上升沿、下表示下降沿,sdi、sdo相對于主機而言的。已經很接近理解了,下一步就是把 上面的過程轉為動畫。

-

脈沖

+關注

關注

20文章

885瀏覽量

95546 -

SPI

+關注

關注

17文章

1701瀏覽量

91335 -

傳輸數據

+關注

關注

1文章

116瀏覽量

16090

原文標題:SPI詳解

文章出處:【微信號:汽車電子嵌入式,微信公眾號:汽車電子嵌入式】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

常用的串口通信協議之SPI協議簡析

TMS320f2809從機選擇信號cs無效時,請問spi時鐘此時應處于什么狀態?

SPI通信協議

通信協議IIC與SPI最全對比

通信協議IIC與SPI之間有何區別?

SPI通信協議原理是什么

SPI通信協議介紹

SPI通信協議介紹

評論