本文主要介紹連接器金屬外殼和金屬外殼搭接不良對靜電放電抗擾度測試的影響。

Part 1

現象描述

某產品在進行靜電放電抗擾度測試時,當對產品中某PCB的DB連接器外殼(如下圖所示)進行靜電放電(-4KV 接觸放電)時,出現系統復位的現象。

后來檢查該DB連接器,發現該連接器的外殼沒有和金屬外殼形成良好的搭接,用導電膠將DB連接器與外殼良好搭接后,再進行測試(-6KV接觸放電),工作正常,系統不再復位。

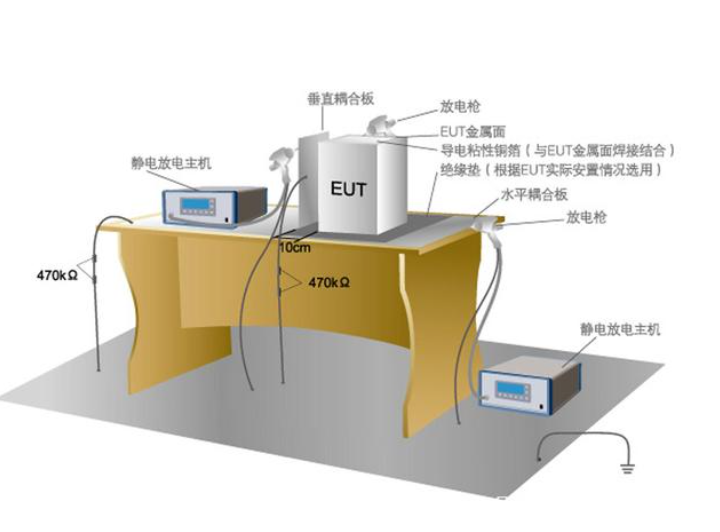

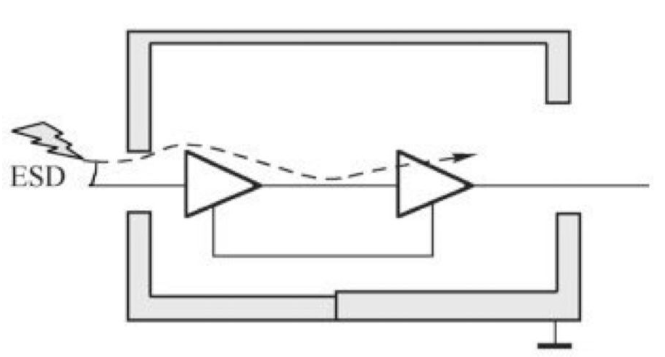

靜電測試的示意圖如下圖所示,想要詳細了解靜電測試的實質的話可以參考我之前的文章《EMC 測試實質之ESD抗擾度》:

究竟是什么原因導致的呢?想要分析靜電帶來的問題時可以從下面幾方面來考慮:

首先判斷測試位置是連接器還是縫隙,連接器是金屬的還是其它的材料的,產品外殼是金屬還是其它材料。

如果是金屬材料,分析產品是否接大地(也稱為PE),如果是浮地系統,則看是否接了功能地。

查看金屬連接器或者金屬按鍵等是否和金屬外殼搭接良好,金屬外殼是否接大地。

總之,靜電問題,一般都是接地不良或者金屬搭接不良導致的。

Part 2

原因分析

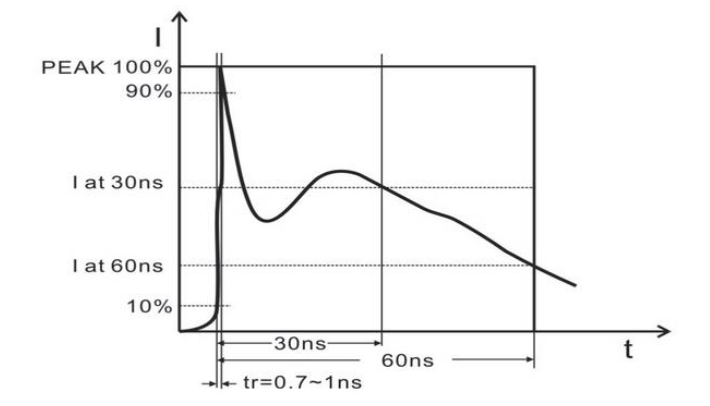

靜電放電(如下圖所示)是一種瞬態能量高,寬頻譜的一種電磁騷擾 ,它主要通過以下兩種途徑來干擾EUT:

直接能量,瞬態的大電流導致內部電路損壞(如IC芯片的損壞,)或者電路出現錯誤(出現閂鎖效應)。

空間耦合,由上圖可知,ESD的前沿時間很短, 約 0.7-1ns, 其頻譜范圍可以達到數百MHz,所以稍微長一點的線纜,PCB中的微帶線或帶狀線都可能形成有效的耦合。

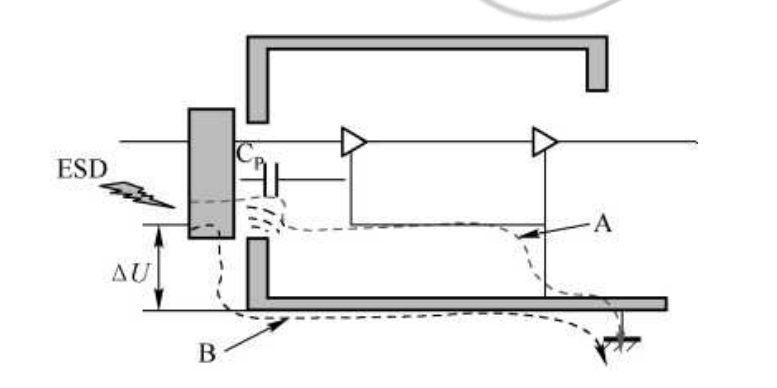

如前面所述,在測試中發現DB連接器的金屬外殼和產品外殼之間有很明顯的縫隙,從電路的角度來看,這個縫隙就等效為一個阻抗,在DB外殼上的靜電放電電流(如圖中虛線所示)的作用下,就會產生較高的壓降ΔU

我們知道,在圖中存在分布電容的地方有如下幾個地方:

DB連接器外殼及機殼與內部電路的地平面

DB連接器外殼及機殼與信號線之間

其中DB連接器外殼及機殼與PCB中地平面之間的分布電容最大,如圖中Cp所示,該分布電容在靜電放電高頻干擾的情況下影響也最大。

在 ΔU 存在的情況下,必然導致一部分靜電放電電流經分布電容Cp流向地平面, 最后流向大地,如圖中虛線 A 所示。

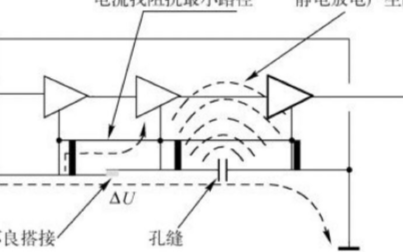

實際上,PCB中的地平面也并不是理想的地面,其并不完整(完整的地平面阻抗為3mΩ),存在一定的阻抗,因為一般地平面上一定有過孔,過孔的縫隙會導致阻抗不連續。

當干擾電流流經工作地平面時,由于阻抗的存在, 就會出現壓降 ΔU1 , 而這個 ΔU1就是造成電路混亂的元兇。

另外,ΔU也是常常是引起輻射發射的超標的原因之一。

通過以上分析,我們可以認為,如果阻抗不連續,干擾信號就很難較快地泄放,這樣就會通過分布電容耦合到內部電路,從而出現損壞或者內部電路混亂。

如果搭接良好,靜電就會很快泄放到外殼上并導入到大地上(前提是外殼也接好大地)。

另外搭接良好,會使外殼具有更好的屏蔽效果,在靜電泄放過程中產生的電磁場就會被屏蔽在外殼外部, 從而保證了內部電路的穩定。

Part 3

處理措施

為了保證DB連接器金屬外殼與產品外殼良好搭接,可以將DB連接器通過螺釘固定在外殼上面,使 DB連接器與金屬面板緊密連接。

從而保持了DB連接器外殼和金屬外殼的電連續性。這樣不僅能提高整機的屏蔽效能,還能使靜電騷擾電流通過金屬外殼很快地泄放掉, 問題得到了解決。

Part 4

思考和啟示

經過上面的分析,我們可以得到如下啟示:

防止靜電干擾直接耦合進PCB的一個有效方法是將靜電干擾信號通過導體直接接到大地上。

要保持靜電放電點的阻抗連續。

-

pcb

+關注

關注

4318文章

23022瀏覽量

396428 -

連接器

+關注

關注

98文章

14345瀏覽量

136208 -

emc

+關注

關注

169文章

3884瀏覽量

182891

原文標題:EMC案例分析——連接器金屬外殼搭接不良對靜電放電抗擾度的影響

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

靜電放電抗擾度測試方案-EMS測試系統

防水連接器金屬與塑料連接器的區別

塑料外殼與金屬外殼連接器對ESD的影響分析

分析塑料外殼連接器和金屬外殼連接器對ESD測試的影響

EMC案例分析——連接器金屬外殼搭接不良對靜電放電抗擾度的影響

EMC案例分析——連接器金屬外殼搭接不良對靜電放電抗擾度的影響

評論