好像任何一個行業的EMC都離不開ESD測試,ESD問題排查中,最重要最難的無疑是靜電路徑問題了。本次就和大伙稍微探討下ESD電流路徑的分析,哪怕在為大家排查靜電問題的時候提供一絲絲有益的思路,我就覺得沒有白寫。

靜電波形

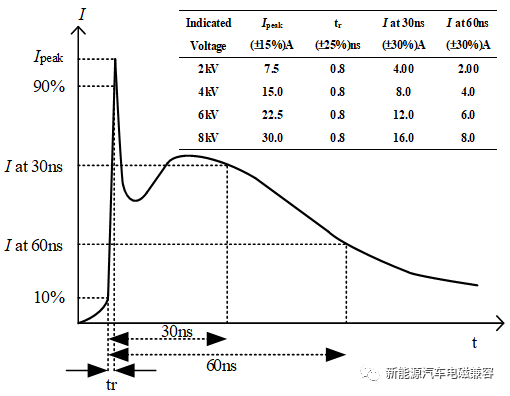

在試驗室,通常使用電容加電阻的方式來模擬人體或其他金屬尖端的靜電效應,由于不同行業可能有不同的放電模型要求。本人僅從汽車電子的角度來分析靜電放電模型(消費電子好像是同一個模型?因為這兩行業最重要的靜電源頭都來自于人體放電),汽車電子的放電模型在IEC 61000-4-2中有明確規定,放電模型決定了靜電放電電流波形,IEC中的靜電放電波形如下圖所示。

靜電電流頻譜分布

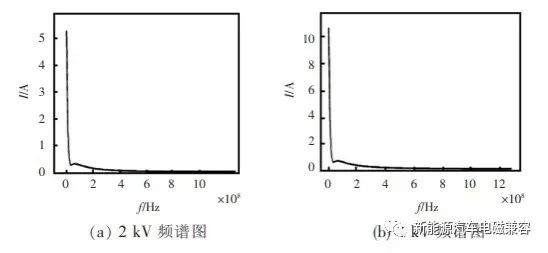

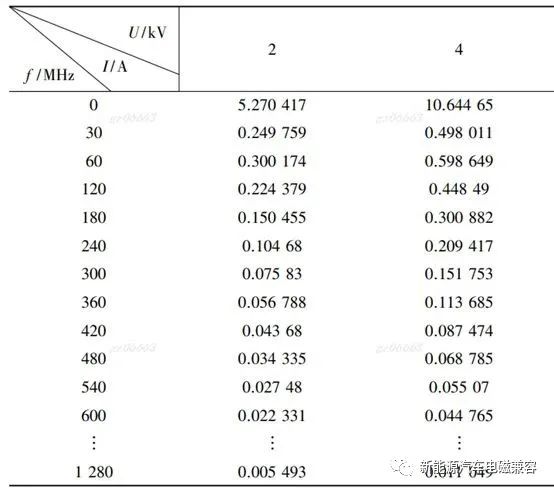

實際上靜電放電效應可以簡單的認為電容通過電阻放電的效應。都是在前段極短的時間內上升到高點,后慢慢減小。上升時間大概為1ns,持續大約為60ns。該波形確實可以通過數學公式進行標明,但是比較復雜,本文只注重結果,所有不進行表述。該數學公式可以通過傅里葉變換得到靜電電流的頻譜。如下圖所示。

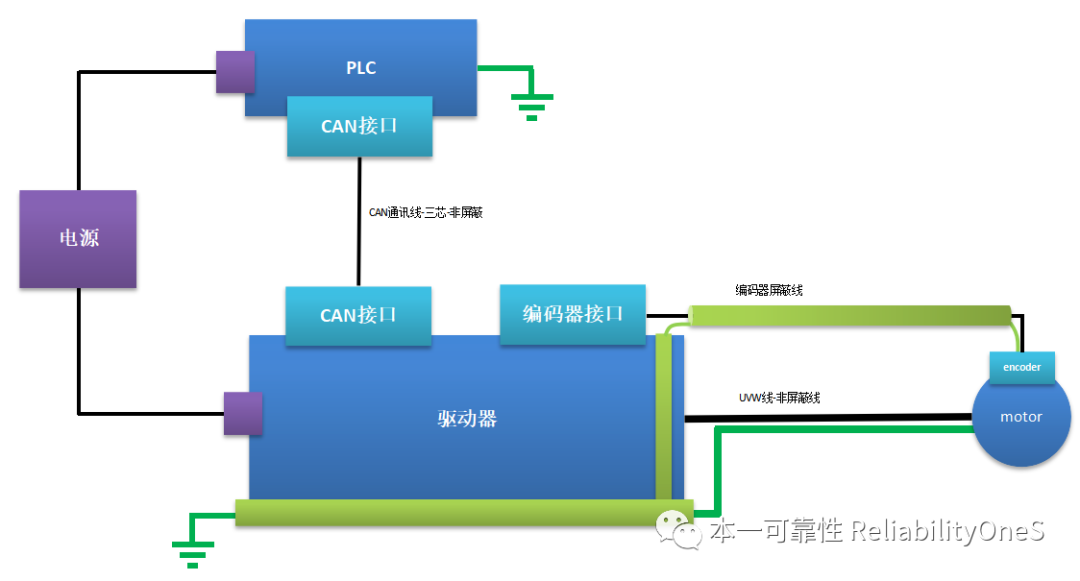

可見,靜電最大的能量還是集中在直流分量上面。頻譜分布從直流到1GHz,因此靜電的電路路徑會比較復雜。從傳導到輻射,都有。但是靜電99%的能量都集中在300MHz之前。因此,對于過高頻率的路徑我們可以忽略不計,將注意力集中在分析300MHz帶寬的路徑上面。大部分的汽車電子產品在進行靜電放電測試時,都是通過電源負極對靜電電流進行回流(通過金屬外殼回流的一般風險也比較小,本文不闡述)。正是因為靜電的電流頻譜很寬,因此,要完全把握靜電電流的路徑非常困難,一般要借助二維場求解器。

但是在設計前期,必須要考慮到所有靜電放電點到電源負極的直流路徑,為靜電的直流分量提供一條低阻抗的路徑,避免該直流分量引起共阻抗耦合的風險!!另外在靜電風險比較高的走線,必須在板內放置濾波電容,1nF的貼片電容是比較合適的值(因為諧振點在300MHz左右,對于靜電整個頻段都有較好的濾波效果)。還有,對于靜電電流產生的輻射場導致的問題,非常難于把控,我自己也無法準確說出該類問題的輻射源頭。但是基本上是由于高頻分量路徑過長導致。

另外,產品的靜電風險是比較容易進行仿真的一個項目,我們只要仿真出放電點到預設泄放安全點的阻抗-頻率曲線和放電點到被害點(敏感芯片管腳或信號)的阻抗-頻率曲線,這兩個阻抗進行比較,就能夠得出到達被害點的靜電能量,以評估該放電點的風險。這個仿真還是比較準確,比較有設計參考意義的。建議靜電設計有難度的產品進行開展。當然,當產品已經設計出來之后,也可以使用網分或阻抗分析儀對放電點和泄放點之間進行測試,如滿足一定的阻抗-頻率曲線(每個公司都有該曲線的不同理解,需要根據產品情況進行進行約束),則該放電點的靜電風險很低。

最后,需要注意的是芯片的datasheet中一般會指出該芯片能夠滿足的靜電放電等級,一般標明的是HBM(人體放電模型)和CDM(帶電體放電模型),這兩個模型都是為了衡量芯片在生產和運輸過程中可能遇到的ESD風險,不適用于產品在日常使用過程中可能遇到的靜電問題。這兩個模型和IEC中的模型是不同的。但是基本上可以將IEC的模型認為是HBM模型和CDM模型的疊加。因此,芯片上標明的ESD等級不能夠等同試驗中測試的等級,IEC的模型是更加嚴酷的。

審核編輯:湯梓紅

-

ESD

+關注

關注

48文章

2012瀏覽量

172798 -

靜電放電

+關注

關注

3文章

284瀏覽量

44620 -

emc

+關注

關注

169文章

3884瀏覽量

182891 -

波形

+關注

關注

3文章

378瀏覽量

31510

原文標題:淺談靜電放電路徑分析

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

驅動器共模電流路徑與數學模型分析

ESD保護元件的對比分析及大電流性能鑒定

ESD保護方法的對比分析

ESD設計與綜合

ESD損壞PCB板的原理分析

基于EMC的ESD防護設計分析

ESD靜電放電

ArcGIS的路徑分析

高速PCB設計——回流路徑分析

案例分享:電單車電控模塊ESD故障分析(下)?

ESD保護元件的對比分析及大電流性能鑒定

網絡路徑的仿真系統設計與分析(基于透明串聯部署的方法)

互感--連接器引起串擾的因素分析 如何改變返回電流路徑

ESD電流路徑的分析

ESD電流路徑的分析

評論