LVDS傳輸?shù)氖鞘裁?a target="_blank">信號?判斷LVDS信號正常的方法

一、LVDS傳輸?shù)氖鞘裁葱盘枺?br />

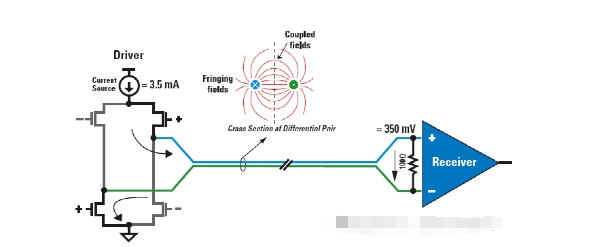

LVDS是一種低電壓差分信號,有兩種電壓狀態(tài),即高電平和低電平,它類似于RS485協(xié)議。LVDS信號作為一種數(shù)字信號,用于高速數(shù)據(jù)傳輸。它的優(yōu)勢包括高速傳輸能力、低功耗、抗干擾能力強、傳輸距離遠等。

二、LVDS信號正常的判斷方法

1. LVDS通信線路測試

LVDS通信線路測試主要用來判斷LVDS通信電纜、連接器、接口是否良好,需要用到萬用表、信號發(fā)生器、示波器等測試設備。測試時首先將信號發(fā)生器傳輸LVDS數(shù)字信號,然后用萬用表測試信號發(fā)生器發(fā)出的數(shù)字信號的高低電平是否正常。接下來,將信號發(fā)生器和LVDS接口連接,再對接口的電壓進行測試,觀察電平是否正常。

2. LVDS信號波形測試

LVDS信號波形測試主要是為了檢測LVDS信號是否干凈、清晰。需要使用示波器等設備進行測試。首先將LVDS信號輸出到示波器上,然后讀取波形。正常情況下,LVDS信號應該是一條干凈的矩形波形。如果LVDS信號波形顯示的不正常,則可能存在通信故障或者存在干擾因素。

3. LVDS傳輸距離測試

LVDS傳輸距離測試主要是為了檢測信號在傳輸過程中的衰減,更好地判斷LVDS信號傳輸情況。測試時,需要使用帶增益放大器的接收器來接收LVDS信號,然后增加距離,逐漸測試信號的衰減情況。如果信號能夠被正常接收,可以說明LVDS信號傳輸過程中不存在較大的衰減,反之則需要進行檢修處理。

四、總結(jié)

LVDS信號的判斷不僅需要單一測試手段,還需要多種測試方法綜合使用,才能更好地確認是否信號正常。在使用LVDS通信協(xié)議的應用中,更需要嚴格檢測,確保其傳輸穩(wěn)定,提高其應用可靠性。

-

連接器

+關(guān)注

關(guān)注

98文章

14310瀏覽量

136158 -

信號發(fā)生器

+關(guān)注

關(guān)注

28文章

1452瀏覽量

108652 -

LVDS信號

+關(guān)注

關(guān)注

0文章

17瀏覽量

7817

發(fā)布評論請先 登錄

相關(guān)推薦

ADS42LB49的CLK一定需要LVDS信號才能驅(qū)動嗎?

lvds接口與其他接口比較

lvds接口適用于哪些設備 lvds接口兼容性問題解析

lvds接口傳輸距離限制 lvds接口優(yōu)勢及劣勢分析

lvds接口和HDMI的區(qū)別 lvds接口電路設計技巧

lvds接口用途與應用 lvds接口連接方法指南

lvds接口需要驅(qū)動嗎

LVDS靜電放電防護方案

低壓差分信號(LVDS)在LED燈墻中的應用

LVDS傳輸?shù)氖鞘裁葱盘枺颗袛郘VDS信號正常的方法

LVDS傳輸?shù)氖鞘裁葱盘枺颗袛郘VDS信號正常的方法

評論