引言:本節(jié)開(kāi)始從一些實(shí)例出發(fā),理論結(jié)合實(shí)際來(lái)進(jìn)一步探討電源噪聲處理的方式選擇和效果評(píng)估。

1.Boost型DC-DC輻射EMI分析

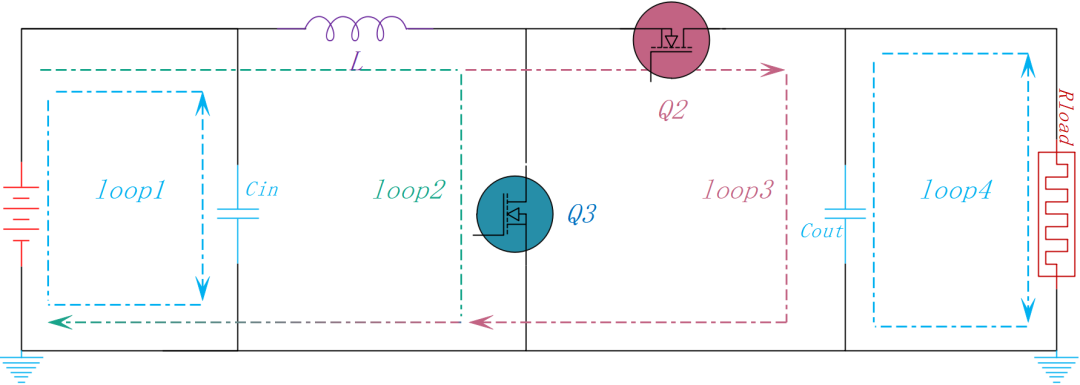

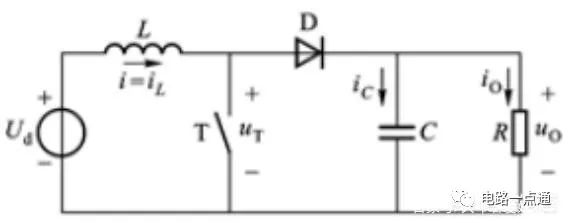

圖10-1是典型的同步Boost電路,由輸入電容Cin,電感L,開(kāi)關(guān)器件Q1、Q2以及輸出電容Cout組成,同時(shí)形成4個(gè)回路。

Loop2和Loop3為開(kāi)關(guān)電流斷續(xù)回路,具有高di/dt和dv/dt,因此SW節(jié)點(diǎn)振鈴明顯。Loop1和Loop4雖然是存在反復(fù)充電放電,但卻是電流連續(xù)回路,電感電流連續(xù),高頻噪聲主要來(lái)源于SW節(jié)點(diǎn)開(kāi)關(guān)高頻噪聲的傳導(dǎo),由于Q2電流斷續(xù)(Boost的特征),Cout的容值大小以及位置決定了Loop4中Vout節(jié)點(diǎn)高頻噪聲幅值。(傳送門:DC-DC-3:升壓型的工作原理)

圖10-1:BOOST開(kāi)關(guān)回路分析

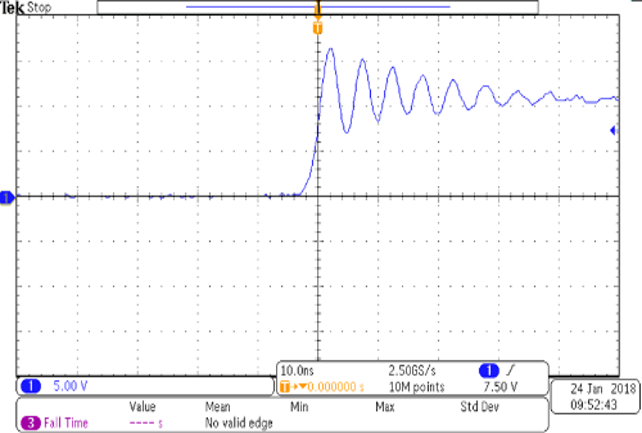

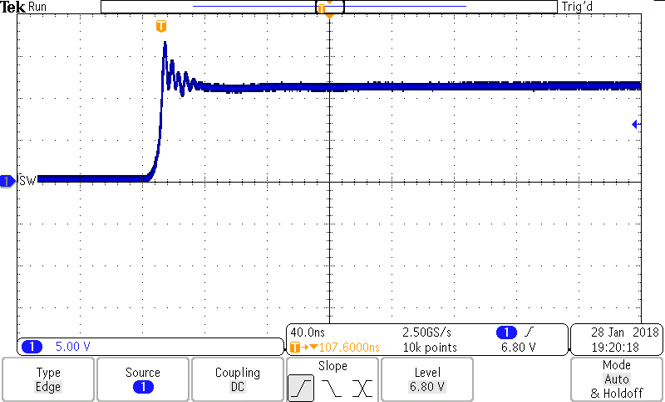

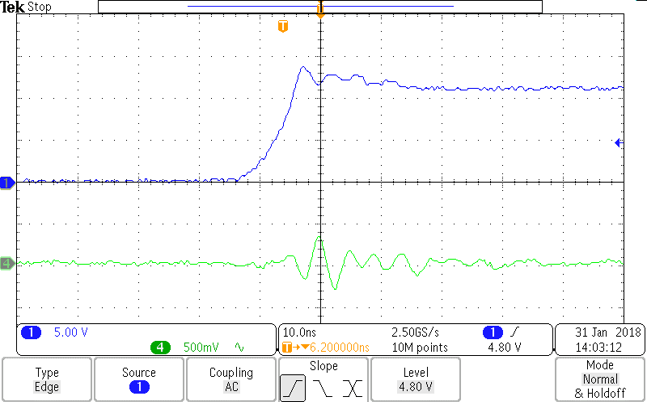

圖10-2為SW節(jié)點(diǎn)典型的開(kāi)關(guān)波形(輸出僅放置Bulk電容),SW開(kāi)關(guān)節(jié)點(diǎn)振鈴幅值高達(dá)10V,震蕩頻率為200MHz左右。

圖10-2:SW開(kāi)關(guān)節(jié)點(diǎn)波形

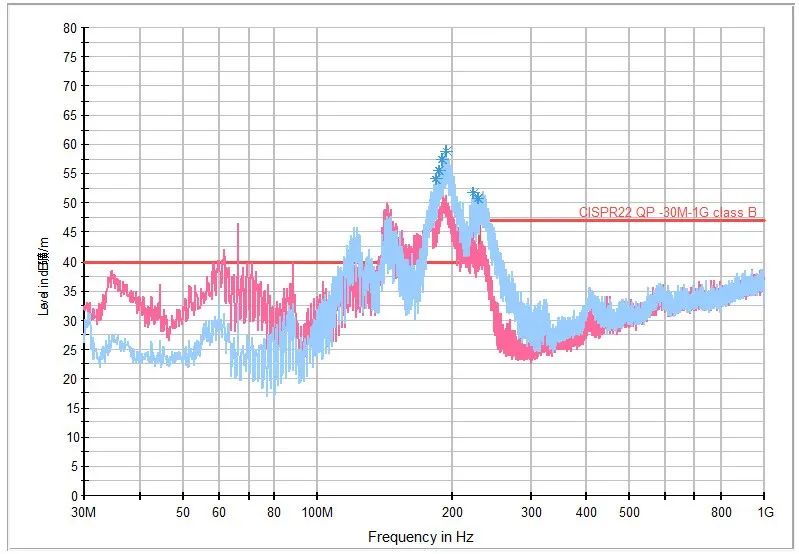

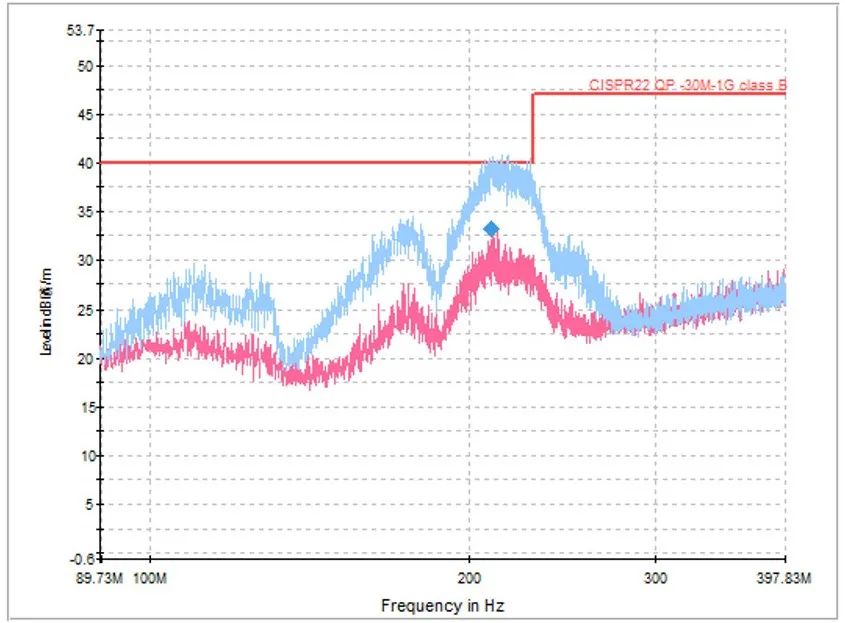

圖10-3是對(duì)應(yīng)于圖10-2的實(shí)際輻射EMI測(cè)試結(jié)果,采用3m方法,藍(lán)色為垂直方向,紅色為水平方向。測(cè)試結(jié)果顯示噪聲在頻域上的峰值在200MHz附近,與時(shí)域測(cè)試結(jié)果圖10-2吻合,因此抑制輻射EMI峰值意味著需要大幅度降低SW節(jié)點(diǎn)的振鈴幅值,以及振鈴周期數(shù)。

圖10-3:輻射EMI測(cè)量幅值(CE測(cè)試標(biāo)準(zhǔn))

2.BOOST輸出電容選擇

如圖10-1所示,Boost的Cout選擇有幾個(gè)關(guān)鍵考慮點(diǎn):

1:輸出紋波幅值

2:系統(tǒng)穩(wěn)定性需求

3:SW節(jié)點(diǎn)的振鈴幅值

4:輸出電容耐壓等級(jí)(陶瓷電容容值隨耐壓增加而衰減)。其中1、2、3、4與SW節(jié)點(diǎn)振鈴幅值,輻射EMI息息相關(guān)。

圖10-1中輸出回路3(包含Q2、Cout)是斷續(xù)回路,必須連接一個(gè)100nF-1uF去耦電容,該去耦電容對(duì)于降低SW振鈴幅值有著關(guān)鍵作用。(傳送門:EMC-7:如何使用電容從后級(jí)應(yīng)對(duì)開(kāi)關(guān)電源噪聲)

為了獲得低的輸出紋波,建議選擇低ESR陶瓷電容,通常3~4顆22uF的X5R電容可以滿足大多數(shù)應(yīng)用,更大的容值有利于輸出電壓動(dòng)態(tài)響應(yīng)。鑒于陶瓷電容隨著電壓增加,容值減小的特性,建議選擇電容耐壓時(shí)考慮留有足夠的裕量。例如輸出電壓12V,建議至少選擇20V或者25V耐壓電容以維持足夠有效的電容值。(傳送門:DC-DC-16:一文教你如何計(jì)算DC-DC的輸入電容Cin與輸出電容Cout)

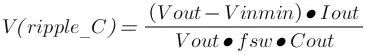

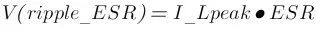

根據(jù)輸出紋波幅值要求,可以利用如下公式計(jì)算最小需求電容值Cout。

其中Vripple_C是輸出紋波幅值,Vripple_ESR是輸出電容ESR導(dǎo)致的紋波,I_Lpeak是電感電流峰值,ESR是輸出電容的ESR。

3.Layout注意點(diǎn)

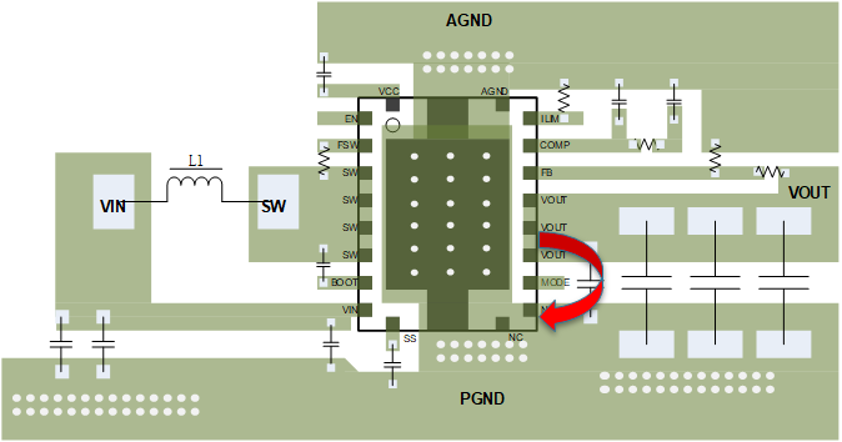

1:由于輸出回路是開(kāi)關(guān)回路,高di/dt和dv/dt,減小回路面積至關(guān)重要,輸出回路去耦電容必須放置在離Vout、GND管腳最近的位置,從而降低SW振鈴幅值,如圖10-4紅色箭頭所示,利用NC管腳作為輸出功率地,從而更近一步降低輸出回路面積,Vout、NC管腳鋪銅盡量寬。

圖10-4:推薦Layout

2:由于SW的高頻振鈴?fù)瑯訒?huì)耦合至輸入端,輸入Bulk電容需要盡量放置離電感、GND近的位置以減小輸入回路面積,輸入端去耦電容同樣需要離Vin端越近越好。

3:下層大面積鋪地,降低地回路阻抗,采用8mil的過(guò)孔連接上下大地,降低熱阻。

4:從系統(tǒng)穩(wěn)定性考慮,

AGND與PGND單端相連,通過(guò)散熱焊盤底部相連,(散熱焊盤同時(shí)也是功率地)。當(dāng)Vout添加上去耦電容,并嚴(yán)格按照版圖注意事項(xiàng)布板,測(cè)試波形如下圖10-5所示,SW振鈴幅值降低到6V,同時(shí)震蕩明顯周期變少。

圖10-5:添加去耦電容和推薦Layout

4.SW開(kāi)關(guān)節(jié)點(diǎn)噪聲吸收電路選擇

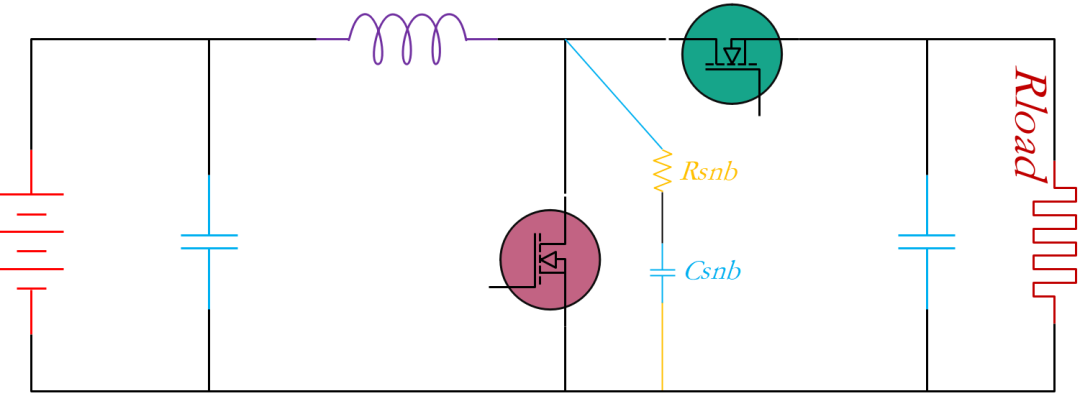

在SW開(kāi)關(guān)節(jié)點(diǎn)添加對(duì)地的RC高頻噪聲吸收電路如圖10-6所示,可以直接降低SW節(jié)點(diǎn)振鈴幅值,該吸收電路通過(guò)降低dv/dt來(lái)降低SW節(jié)點(diǎn)振鈴幅值,因此該電路會(huì)犧牲小于1%的Boost效率。(傳送門:EMC-5:DC-DC的開(kāi)關(guān)節(jié)點(diǎn)振鈴控制)

圖10-6:采用SW節(jié)點(diǎn)振鈴吸收電路

SW高頻噪聲在200MHz附近,因此選擇Rs=2Ω,Cs=2nF,圖10-6為SW節(jié)點(diǎn)加上該吸收電路,測(cè)試結(jié)果為圖10-7所示,相比于圖10-2所示,SW幅值大幅降低(藍(lán)色=SW、綠色=Vin

AC)。

圖10-7:添加SW振鈴吸收電路,測(cè)試波形

基于無(wú)系統(tǒng)級(jí)的EMI濾波器,圖10-8為添加SW節(jié)點(diǎn)RC吸收電路后輻射EMI測(cè)試結(jié)果,相較于 圖10-3 ,EMI峰值下降了20dB。

圖10-8:輻射EMI測(cè)試結(jié)果(RC緩沖電路)

5.磁珠的選擇

在系統(tǒng)級(jí)應(yīng)用中,如果需要進(jìn)一步降低輻射EMI,貼片式磁珠是最簡(jiǎn)單的選擇。關(guān)于磁珠的選擇,有下列幾個(gè)注意事項(xiàng):

1:磁珠的頻率需要覆蓋高頻噪聲頻段,根據(jù) 圖10-3 ,該磁珠需要在100MHz~300MHz頻段表現(xiàn)為高阻抗值。

2:磁珠的飽和電流需要30%高于實(shí)際工作的峰值電流。

3:磁珠的等效阻抗越低越好,有利于減少磁珠帶來(lái)的功耗。

-

emi

+關(guān)注

關(guān)注

53文章

3582瀏覽量

127352 -

DC-DC

+關(guān)注

關(guān)注

30文章

1928瀏覽量

81477 -

Boost

+關(guān)注

關(guān)注

5文章

370瀏覽量

47999 -

電源噪聲

+關(guān)注

關(guān)注

3文章

149瀏覽量

17464

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

DC-DC轉(zhuǎn)換器電路圖 Boost升壓型DC-DC轉(zhuǎn)換器的工作原理

DC-DC 和LDO 簡(jiǎn)單介紹

#硬聲創(chuàng)作季 DC-DC電路之boost電路

如何分析與優(yōu)化設(shè)計(jì)DC-DC 開(kāi)關(guān)電源EMI問(wèn)題

DC-DC變換器的應(yīng)用

DC-DC Boost FH4003

DC-DC Boost FH4001

DC-DC轉(zhuǎn)換器電路圖 Boost升壓型DC-DC轉(zhuǎn)換器的工作原理

Boost升壓型DC-DC轉(zhuǎn)換電路介紹

Boost型DC-DC輻射EMI分析

Boost型DC-DC輻射EMI分析

評(píng)論