談到SystemVerilog,很多工程師都認為SystemVerilog僅僅是一門驗證語言,事實上不只如此。傳統的Verilog和VHDL被稱為HDL(Hardware Description Language,硬件描述語言),而SystemVerilog則是HDVL(Hardware Design and Verification Language,硬件設計與驗證語言)。由此可見,SystemVerilog也是可以用于硬件設計的,也是有可綜合部分的。SystemVerilog本身由3部分構成:

SV-HDL:用于硬件設計,可綜合,是可綜合Verilog的加強版;

SV-Assertion:斷言;

SV-HVL:用于硬件驗證,UVM就是利用此發展而來的驗證方法學。

下圖顯示了SystemVerilog與Verilog可綜合的部分。

至此我們已經澄清了一個事實:SystemVerilog是可以用于硬件設計的。那么相比于Verilog,SystemVerilog在硬件設計部分有哪些優勢呢?

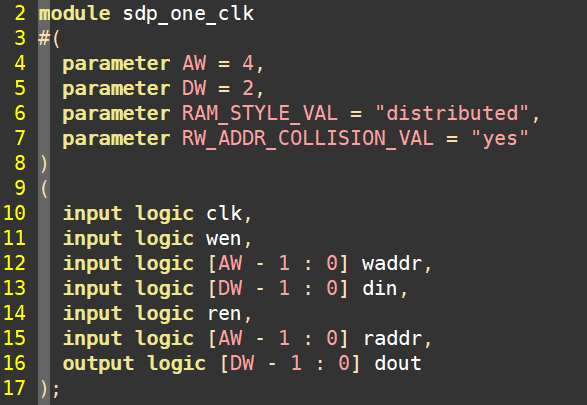

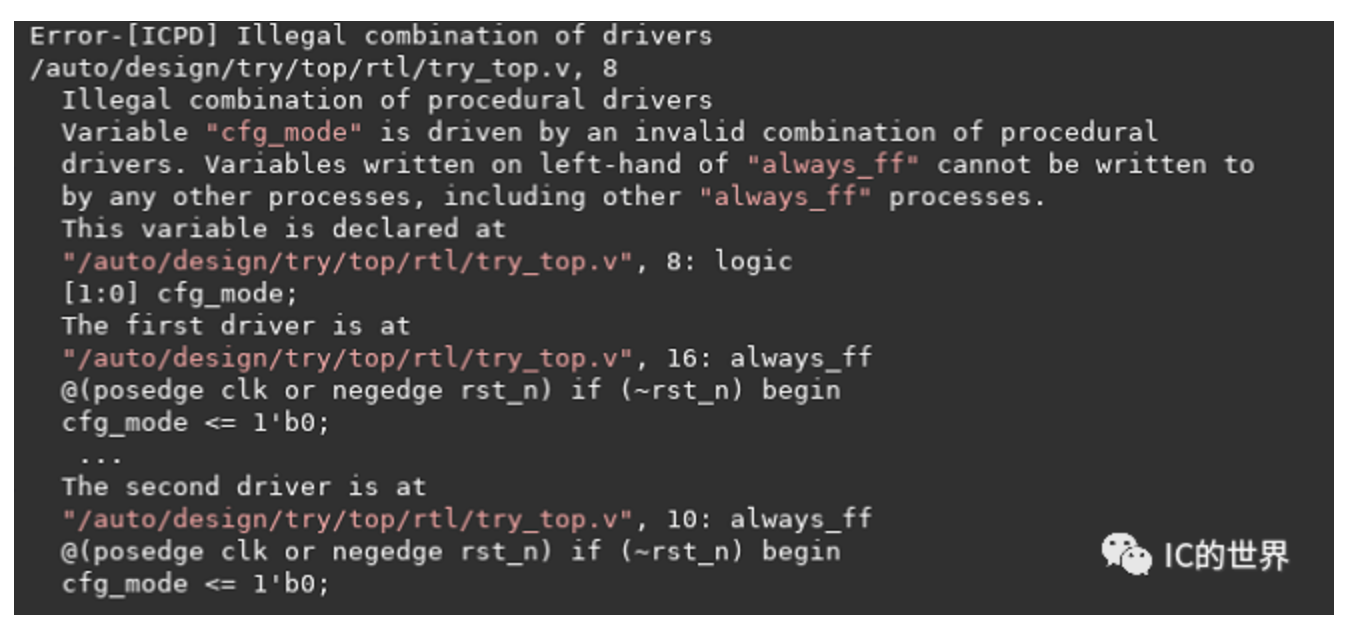

從數據類型的角度看,SystemVerilog引入了4值類型logic,這與VHDL的std_logic是相同的。盡管Verilog中的reg也是4值類型,但在端口聲明時,有的需要聲明為reg,有的需要聲明為wire,內部變量定義亦是如此。同時,reg會讓很多初學者誤以為該變量對應一個寄存器(register),而事實上,只要是always進程或initial中用到的輸出變量都要定義為reg類型。使用logic則避免了這種歧義。如下圖所示代碼片段,輸入/輸出都定義為logic類型。

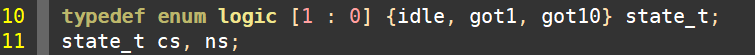

SystemVerilog引入了枚舉類型,通過enum定義,也支持用戶定義的枚舉類型,這使得在描述狀態機時更為方便,如下圖所示代碼片段。同時,SystemVerilog還允許對枚舉變量賦值,這樣就可以根據場景需要明確指定狀態機的編碼方式。

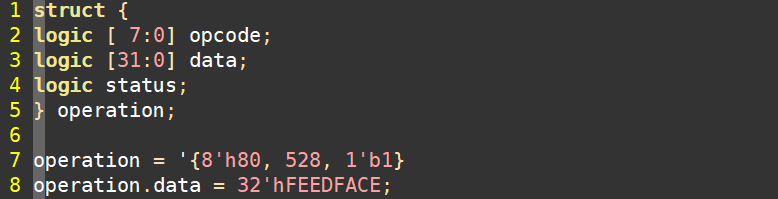

SystemVerilog支持結構體,帶來的好處是可以把相關變量綁定在一起,這樣使用起來更為直觀方便,如下圖所示代碼片段。可以對整個結構體賦值,如代碼第7行所示,也可以對結構體內某個指定變量賦值。struct允許綁定不同類型的數據,而數組則要求數據類型一致,這是兩者的關鍵區別。

同樣地,SystemVerilog也支持用戶定義的結構體,這便于代碼復用。從代碼風格角度看,最好將用戶定義的結構體在package中進行聲明,避免因編譯順序而導致的錯誤。

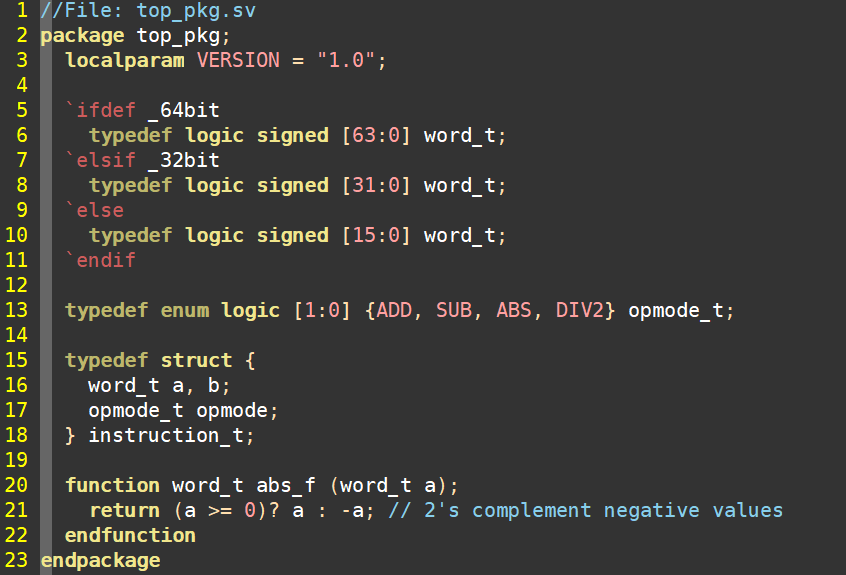

SystemVerilog引入了package,這樣同一個聲明可以被不同模塊使用,避免了重復定義,如下圖所示代碼片段。可以在package中聲明參數、結構體、函數等。具體案例可閱讀這篇文章。

說說SystemVerilog的Package

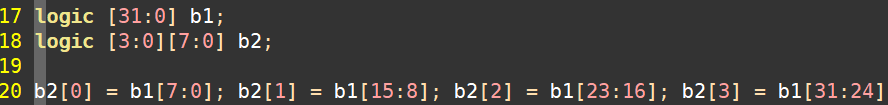

SystemVerilog支持packed array,本質上是對vector的增強。如下圖所示代碼片段。b1是位寬為32的向量,b2本質上也是位寬為32的向量,只是將b2按位域進行分割,如代碼第20行所示。這樣在引用時更為方便,比如獲取b2[1]其實就是獲取b1[15:8]。

對于常規數組,也就是unpacked array,SystemVerilog支持類似于C語言的聲明方式,如下圖所示代碼片段。這兩行代碼是等效的,顯然后者聲明更為簡潔。

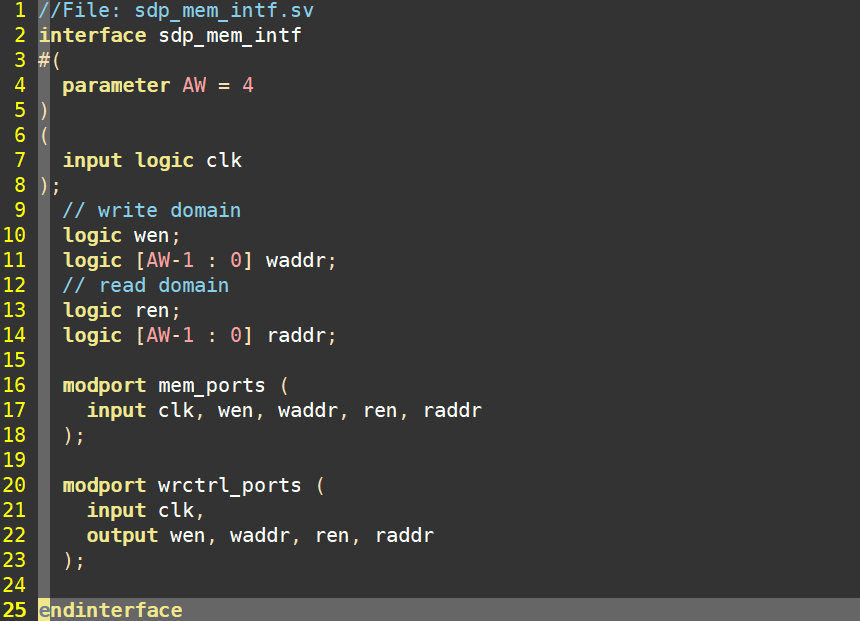

另外,SystemVerilog還引入了interface,這對于描述互連較多的模塊時更為友好方便,具體案例可閱讀這篇文章。

說說SystemVerilog的Interface

審核編輯:湯梓紅

-

Verilog

+關注

關注

28文章

1345瀏覽量

109995 -

System

+關注

關注

0文章

165瀏覽量

36887 -

HDL

+關注

關注

8文章

327瀏覽量

47344 -

硬件設計

+關注

關注

18文章

394瀏覽量

44532 -

驗證語言

+關注

關注

0文章

3瀏覽量

6620

原文標題:SystemVerilog不只是用于驗證(1)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

做FPGA工程師需要掌握SystemVerilog嗎?

SystemC 和SystemVerilog的比較

SystemVerilog設計語言

SystemVerilog的正式驗證和混合驗證

SystemVerilog語言介紹匯總

使用Verilog/SystemVerilog硬件描述語言練習數字硬件設計

FPGA學習-SystemVerilog語言簡介

systemverilog:logic比reg更有優勢?

systemverilog:logic比reg更有優勢

SystemVerilog相比于Verilog的優勢

SystemVerilog在硬件設計部分有哪些優勢

SystemVerilog在硬件設計部分有哪些優勢

評論